Fターム[5F033UU07]の内容

半導体集積回路装置の内部配線 (234,551) | レイアウト、シミュレーション (1,514) | シミュレーション (64)

Fターム[5F033UU07]に分類される特許

21 - 40 / 64

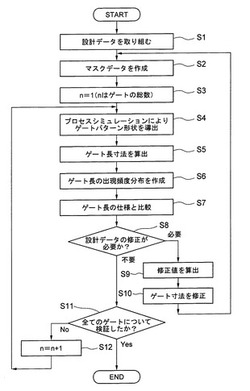

パターンレイアウトの修正方法

【課題】プロセスパラメータのばらつきが生じても仕様に合致した素子の製造を可能にするパターンレイアウトの修正方法を提供する。

【解決手段】設計レイアウトに対応するパターンを基板上に形成するためのプロセスパラメータのばらつきを反映させた複数の条件でプロセスシミュレーションを実行することにより、前記パターンの複数の仕上がりパターンを予測し(ステップS4)、得られた複数の仕上がりパターンの寸法を算出し(ステップS5)、算出された寸法から所定の統計量を算出し(ステップS6)、該統計量と予め設定された仕様とを比較し(ステップS7)、仕様を満たさない場合に(ステップS8)修正量を算出し(ステップS9)、算出された前記修正量に基づいて前記設計レイアウトを修正する(ステップS10)。

(もっと読む)

半導体装置

【課題】 容量低減とビア加工マージンの確保を効率的に達成する。

【解決手段】 複数の配線層を有する半導体装置であって、所定領域を有する第1配線層26と、第1配線層の上層に位置する第2配線層47と、第1配線層と第2配線層との間に設けられる層間絶縁膜36と、層間絶縁膜と第1配線層の配線との間に設けられるバリア絶縁膜(29,31)とを有し、所定領域における配線上部のバリア絶縁膜の厚さは、所定領域以外の領域における配線上部のバリア絶縁膜の厚さよりも厚く、所定領域においては隣接する配線間にエアギャップ35が形成され、所定領域以外においては隣接する配線間にエアギャップが形成されない。

(もっと読む)

半導体装置製造方法およびパターン寸法設定プログラム

【課題】側壁プロセスを用いた場合において、被処理層に最終的に形成されるパターン寸法の面内ばらつきを抑制することができる半導体装置製造方法および最適寸法設定プログラムを提供する。

【解決手段】本発明は、側壁プロセスにおけるパターン変換工程においてそれぞれ形成される各パターンの面内寸法ばらつき量から面内寸法ばらつき量の合計量を求め、該求めた面内寸法ばらつき量の合計量から、面内寸法ばらつき量が少なくなるような各パターンの仕上がり寸法を設定するため、側壁プロセスを用いた場合において、被処理層に最終的に形成されるパターン寸法の面内ばらつきを抑制することができるという効果を奏する。

(もっと読む)

クロストーク防止回路

【課題】 微細化、集積度向上に影響を与えない方法で、クロストークを減少または除去する回路を提供する。

【解決手段】 クロストーク防止回路は、ほぼ平行して形成されている少なくとも2本の信号線、たとえば、マスタスロック用線とスレーブクロック用線l1,l2の間に、これら2本の信号線の少なくとも一方に印加される信号が存在しないとき、たとえば、テスト用信号が印加され、前記2本の信号線に信号が印加されるとき接地状態になる第3の信号線l3を生成する。好ましくは、第3の信号線にドライバ回路を接続し、該ドライバ回路の出力トランジスタのNチャネルトランジスタとPチャネルトランジスタの電流駆動能力の比率をほぼ2:1にする。

(もっと読む)

半導体装置

【課題】配線の幅広配線部から突出した凸状配線部に形成されたビアについて、ストレスマイグレーション耐性を向上し得る半導体装置を提供する。

【解決手段】第1の配線18と、第1の配線18の上方に形成され、第1の配線18に接続されたビア38を一体的に有する第2の配線34と、ビア38に隣接して配置され、ビア38と同層に形成された複数のダミービア40a、40b、40c、40dとを有している。

(もっと読む)

半導体装置の製造方法および半導体装置製造システム

【課題】設計データの変更を行わずに、半導体装置の信頼性を高める。

【解決手段】設定データに基づき膜のプロセス条件を設定する工程(S1)と、プロセス条件に基づいて膜の平坦化シミュレーションを行う工程(S2)と、平坦化シミュレーションから膜の危険個所の有無を判断する工程(S3)と、平坦化シミュレーションの判断に基づいて膜の平坦化を行う工程(S4)と、を有する半導体装置の製造方法によって、設計データの変更を行わずに、信頼性が高められた半導体装置が提供される。

(もっと読む)

半導体装置

【課題】曲げ等の外力が加わり応力が生じた場合であってもトランジスタ等の損傷を低減する半導体装置を提供することを目的とする。

【解決手段】可撓性を有する基板上に設けられた第1の島状の補強膜と、第1の島状の補強膜上に、チャネル形成領域と不純物領域とを具備する半導体膜と、チャネル形成領域の上方にゲート絶縁膜を介して設けられた第1の導電膜と、第1の導電膜及びゲート絶縁膜を覆って設けられた第2の島状の補強膜とを有している。

(もっと読む)

ダミーパタン設計方法、情報処理装置およびプログラム

【課題】配線のうち高速信号線における信号速度の低下を抑制し、CMP処理における平坦化効果を向上させたダミーパタン設計方法を提供する。

【解決手段】絶縁層を挟んで第1の配線層および第2の配線層が順に積層された半導体装置の第1の配線層に対するダミーパタン設計方法であって、第2の配線層に含まれる配線のうちダミーパタンとの配線容量が所定の値以下であることが要求される第1の配線を抽出し、第1の配線との間で生じる容量が所定の値以下になる、形状および位置の第1のダミーパタンを空き領域に配置し、第2の配線層において第1の配線を除く配線である第2の配線の下方の空き領域に第2のダミーパタンを配置するものである。

(もっと読む)

半導体装置の設計支援装置、当該装置としてコンピュータを機能させるためのプログラムおよび記録媒体、ならびに半導体装置の製造方法

【課題】半導体装置の経時的な絶縁破壊寿命を高精度で予測することができる設計支援装置およびそれを用いた半導体装置の製造方法を提供する。

【解決手段】設計支援装置100は、設計パターンデータ入力部810と、工程ばらつき入力部820と、工程ばらつきの実現値生成部854と、最小間隔算出部855と、絶縁破壊時間の累積分布関数確定部856と、絶縁破壊時間の実現値生成部857とを備えている。工程ばらつきおよび絶縁破壊時間のそれぞれの実現値はモンテカルロ法により生成される。最小間隔算出部855は、工程ばらつきの実現値に基づいてビアパターンと配線パターンとの最小間隔を算出する。

(もっと読む)

半導体装置の平坦化方法および半導体装置の平坦化システム

【課題】ダミーパターンの一部を削除することにより、ダミーパターン挿入量を最小化しつつ、かつチップ内の凹凸を抑制することができる半導体装置の平坦化方法および半導体装置の平坦化システムを提供する。

【解決手段】半導体装置の製造において、シミュレーションサーバを用いて、配線として形成される溝以外に電気的に機能しないダミーパターンを導入する半導体装置の平坦化方法であって、ダミーパターンを設計データ上にて、配線またはその他の電気的に機能するパターンが存在する場所以外の全ての領域に規定の間隔で導入した後、CMPプロセス後の膜厚が厚くなると予測される場所から設計データ上のダミーパターンを削除し、ダミーパターンが削除された後の設計データを用いてシャドウマスクを製造する。

(もっと読む)

回路装置、回路装置の製造方法および半導体モジュール

【課題】回路装置における配線の接続信頼性を向上する技術を提供する。

【解決手段】回路装置10は、回路素子が形成された半導体基板12と、半導体基板12の表面Sに形成された電極14と、電極14の上に設けられた絶縁層16と、絶縁層16の上に設けられた第2の配線層18と、絶縁層16を貫通して電極14および第2の配線層18を電気的に接続する導電性バンプ20と、を備える。導電性バンプ20は、電極14と第2の配線層18との導通方向の結晶粒のサイズより、半導体基板12の表面Sと平行な方向の結晶粒のサイズが大きい。

(もっと読む)

半導体装置の評価方法及び評価システム

【課題】配線にかかわる物理量の製造ばらつきを高精度に決定すること。

【解決手段】半導体装置中の配線構造の設計値からの製造ばらつきを評価するための方法が提供される。その評価方法は、(a)配線構造に関する配線抵抗・容量を、製造ばらつきを示すパラメータσの関数として表す近似式を作成するステップと、(b)当該配線構造に関する配線抵抗・容量の分布を実測するステップと、(c)上記近似式で上記分布が所定の確率で再現されるように上記パラメータσを決定するステップと、を有する。

(もっと読む)

成膜形状シミュレーション方法及び電子デバイスの製造方法

【課題】膜厚の正確な予測が可能な成膜形状シミュレーション及びこれを用いた電子デバイスの製造方法を提供する。

【解決手段】基体の表面に堆積種を供給することにより形成される薄膜の厚みを計算する成膜形状シミュレーション方法であって、計算に用いるパラメータを、堆積された薄膜の厚みに応じて変更することを特徴とする成膜形状シミュレーション方法が提供される。また、本発明の他の一態様によれば、上記の成膜形状シミュレーション方法により薄膜の堆積条件を求め、前記求められた条件により薄膜を堆積することを特徴とする電子デバイスの製造方法が提供される。

(もっと読む)

信頼性設計支援方法

【課題】経年変化による特性の劣化が抑制され、寿命に係る性能を十分に満足した信頼性の高い半導体集積回路装置を効率良く設計することが可能な信頼性設計支援方法を提供する。

【解決手段】信頼性設計支援方法は、初期マスクレイアウトパターン10で示され、半導体集積回路装置の内、経年変化により特性が劣化する劣化発生箇所を求める経年劣化対象箇所抽出ステップ20と、初期マスクレイアウトパターン10を変形して、経年変化後の半導体集積回路装置を示す劣化マスクレイアウトパターン40を生成する経年劣化実行ステップ30と、劣化マスクレイアウトパターン40で示される半導体集積回路装置の特性を評価する経年劣化対策ステップ50とを備えている。経年劣化対策ステップ50では、評価結果に基づいて初期マスクレイアウトパターン10を修正する。

(もっと読む)

素子特性測定回路及び半導体装置

【課題】従来の素子特性測定回路では、同じ測定対象に対して抵抗値と容量値を精度良く測定することができなかった。

【解決手段】本発明にかかる素子特性測定回路は、被測定素子M1が接続される第1のノードN1と、被測定素子M1と実質的に同じ幅と被測定素子M1よりも短い長さを有するダミー素子M2が接続される第2のノードN2と、第1の端子VDD1と第1のノードN1との間及び第2の端子VDD2と第2のノードN2との間に接続される第1のスイッチ12と、第1のノードN1と第3の端子GNDとの間及び第2のノードN2と第3の端子GNDとの間に接続される第2のスイッチ13と、被測定素子M2上に形成される第1、第2の電圧測定ノードN4、N5と、被測定素子M2上の第1、第2の電圧測定ノードN4、N5よりも第1のノードN1との距離が遠くなる位置に形成される第1の電流入出力ノードN3とを有するものである。

(もっと読む)

配線構造及び配線設計方法

【課題】ビア数を減らしても、エレクトロマイグレーション耐性を維持、または向上することのできる配線設計方法を提供する。

【解決手段】異なる層に位置する第1の配線と第2の配線を複数のビアで接続する配線設計方法において、配線幅方向のビアの数であるビア列数を変えたときの配線の寿命の変化率と、配線長方向のビアの数であるビア行数を変えたときの前記配線の寿命の変化率を求める。処理対象となるビアアレイのビア列数を、前記ビア列数に対する前記寿命の変化率と、前記ビア行数に対する前記寿命の変化率とに基づいて決定されるビア行列数増減比Nに従って低減する。そして、前記ビアアレイのビア行数を、少なくとも1行増加する。

(もっと読む)

半導体装置

【課題】中空構造において温度上昇による層間絶縁膜の変形を抑制する。

【解決手段】本発明の例に係る半導体装置は、半導体基板S上に互いに上下に隣接してスタックされる中空構造の第1及び第2配線層L4,L5と、第1配線層L4内に形成され、信号線として機能しないダミーパターンPと、第2配線層L5内に形成される導電パターンPとを備える。そして、半導体基板S上からみて、ダミーパターンPと導電パターンPとは、互いにオーバーラップする部分とそれ以外の部分とを有する。

(もっと読む)

回路パターン設計システム、回路パターン設計方法、及び回路パターン設計プログラム

【課題】突抜けが発生しないようにビアプラグを配置することのできる回路パターン設計システム、回路パターン設計方法、及び回路パターン設計プログラムを提供する。

【解決手段】ビア束の形状とエッチング後にビア底部の突抜けが発生するビア束間スペース幅との対応関係を示すスペース幅算出用データ部を準備するスペース幅算出用データ提供ステップと、複数のビアの配置情報を含む仮レイアウトデータを準備するステップと、前記仮レイアウトデータ中に対して、確認対象ビア束を設定する確認対象ビア束設定ステップと、前記確認対象ビア束の形状を認識する形状認識ステップと、前記スペース幅算出用データを参照して、認識した前記確認対象ビア束の形状に対応する前記ビア束間スペース幅を、禁止スペース幅として算出する禁止スペース幅算出ステップと、前記禁止スペース幅を、前記確認対象ビア束と対応付けて出力する出力ステップと、を具備する。

(もっと読む)

半導体素子、半導体装置および実装基板

【課題】シールリングを介して一の回路に伝播する他の回路のノイズを低減することの可能な半導体素子を提供する。

【解決手段】アナログ回路10およびデジタル回路20がp型半導体基板40に混載されている。スクライブライン領域に環状のシールリング60が設けられており、シールリング60に含まれるp型半導体領域35の一部がチップの内側のレイアウトパターン領域にまで延在している。シールリング60はp型半導体領域35を介してノイズアイソレータ70に接続されており、ノイズアイソレータ70を介して外部の低インピーダンスノード(図示せず)と電気的に接続されている。

(もっと読む)

シミュレーションモデルの評価方法、プログラム及び半導体装置の製造方法

【課題】的確な評価を行うことが可能なシミュレーションモデルの評価方法等を提供する。

【解決手段】第1のパターンに基づく所定の処理によって生成される第2のパターンを予測するためのシミュレーションモデルを用意する工程ST12と、シミュレーションモデルを用いて第2のパターンを予測する工程ST13と、予測された第2のパターンに疑似的な寸法誤差成分を付加した疑似パターンを生成する工程ST14と、疑似パターンに適合するようにシミュレーションモデルに含まれるパラメータを変化させる工程ST15と、変化したパラメータを含んだシミュレーションモデルを用いて第2のパターンを再予測する工程ST16と、再予測された第2のパターンと疑似パターンとの寸法差を求める工程ST17と、疑似的な寸法誤差成分と寸法差との関係を求める工程ST18とを備える。

(もっと読む)

21 - 40 / 64

[ Back to top ]