Fターム[5F033UU07]の内容

半導体集積回路装置の内部配線 (234,551) | レイアウト、シミュレーション (1,514) | シミュレーション (64)

Fターム[5F033UU07]に分類される特許

41 - 60 / 64

半導体装置の製造方法および製造システム

【課題】CMP研磨における残留段差を規定値以下としつつ、膜堆積プロセスとCMPプロセスの製造スループット向上とコスト抑制を実現することができる半導体装置の製造技術を提供する。

【解決手段】半導体製造におけるCMPプロセスおよび膜堆積プロセスにおいて、CMP研磨後に生じる残留段差が規定値以内となる研磨量を情報処理装置で予測し、その研磨量と同一もしくはより厚い膜をCMP装置で研磨する以前に予め堆積させる。これにより、膜堆積プロセスで堆積する膜の厚さを最小限に抑制でき、また堆積した膜をCMP研磨する段階においても最小限の研磨量とすることができ、製造時のスループット向上とコスト抑制が可能となる。また、過剰研磨の発生による不良発生を未然に抑止することが可能となる。

(もっと読む)

金属配線の信頼性評価装置及び方法、並びに金属配線の信頼性評価のためのプログラムを格納した記録媒体

【課題】金属配線のEM損傷支配パラメータを用いた数値シミュレーションにより、ボイド形成および断線故障に関する予測を行う。

【解決手段】 数値シミュレーションにおいて、金属配線は要素に分割される。電流密度および温度の分布は数値解析により得られる(S304)。各要素の原子流束発散AFDgenは、これらの分布と前もって加速試験により決定される材料物性の定数(S306)を用いることにより計算される(S308)。シミュレーションにおける1計算ステップあたりの体積減少(S312)は、各要素の体積、1計算ステップに対応する時間、および計算されたAFDgenに対応する原子体積を乗じることにより与えられる(S310)。体積に関する減少量を基に、各要素の厚さを減少する(S314)。厚さが減少した要素において、ボイドが形成されたことを示している。金属配線における電流密度と温度の分布の数値解析を各要素の厚さを考慮して再び行う(S304)。計算は繰り返し行われる。

(もっと読む)

シミュレーション装置およびそれを含んだ検査装置

【課題】多層配線構造の半導体チップの研磨後標高分布を容易に算出することが可能なシミュレーション装置を提供すること。

【解決手段】凸部占有率算出部22は、シミュレーション対象層の直下のマスクデータに基づいてシミュレーション対象層の膜厚を算出し、下層の標高とシミュレーション対象の膜厚とに基づいて凸部占有率を算出する。標高分布算出部23は、プレストン式を用いて、下層の標高と凸部占有率算出部22によって算出された凸部占有率とに基づいてシミュレーション対象層の研磨後の標高を算出する。したがって、多層配線構造の半導体チップの研磨後標高分布を容易に算出することが可能となる。

(もっと読む)

膜厚予測プログラム、記録媒体、膜厚予測装置および膜厚予測方法

【課題】膨縮後における配線溝の形状を表現する溝形状関数モデルを利用した膜厚予測シミュレーションをおこなうことによって、基板表面上に形成される薄膜の膜厚を正確に予測する。

【解決手段】膜厚予測装置は、TEGを用いて実測された各種パターンの配線溝上に形成される銅メッキの膜厚の実測値と、メッキモデルおよび条件ファイルに基づいて算出された銅メッキの膜厚と、を比較する。つぎに、この比較結果から、最も適したメッキモデルを導出し、最適なメッキモデルを用いて設計対象となる基板表面に形成される銅メッキの膜厚を算出する。これにより、膜厚予測装置によれば、精度の高い膜厚予測シミュレーションをおこなうことができる。

(もっと読む)

半導体装置の製造方法及び半導体装置の製造装置

【課題】半導体ウェハの表面を均一に研磨することのできる半導体装置の製造方法、及び半導体装置の製造装置、を提供する。

【解決手段】研磨パッドに半導体ウェハを押しつけて半導体ウェハを研磨する半導体装置の製造方法において、前記研磨パッドの硬度に基いて研磨条件を求める最適条件算出工程と、求めた研磨条件にて前記半導体ウェハを研磨する工程と、を具備する。

(もっと読む)

LSIの配線構造の設計方法

【課題】 配線容量C及び配線遅延RCの低減の可能なLSIの配線構造の設計方法を提供する。

【解決手段】プロセスばらつき量を推定しδPとし、配線遅延の変動Δ(RC)/(RC)の許容値を設定しξRCとし、フリンジ容量CFと平行平板容量CPからフリンジ容量比F=CF/CPを評価して、以下の式

F ≦ (1−δP)・δP/(δP−ξRC) − 1

を満たすように、配線構造が決定される。

(もっと読む)

半導体装置の製造方法および半導体装置の設計支援システム

【課題】CMP後の金属膜を容易に平坦化できる技術を提供することができる。

【解決手段】半導体デバイス(被加工物)表面上に電気的に機能する溝状または孔状の配線パターン3(第1パターン)と、電気的に機能しない複数の溝状または孔状のダミーパターン4(第2パターン)を形成する工程と、配線パターン3上をメッキ法により、金属膜で被覆する工程と、被覆された金属膜をCMP法により研磨する工程とを有する半導体装置の製造方法であって、ダミーパターン4を形成する工程では、配線パターン3の溝幅に応じて、ダミーパターン4の溝幅および配置領域を決定し、選択的に形成させる。

(もっと読む)

LSIの配線構造

【課題】 配線容量C及び配線遅延RCの低減の可能なLSIの配線構造を提供する。

【解決手段】配線長が1mm未満の配線構造において、配線の厚み方向の配線間絶縁層の誘電率を、配線の幅方向の配線間絶縁層の誘電率より相対的に高くする。

(もっと読む)

設計データ作成方法、設計データ作成プログラム、及び半導体装置の製造方法

【課題】作成された設計データを用いて製造される半導体装置の歩留まりを向上させる設計データ作成方法、設計データ作成プログラム、及び半導体装置の製造方法を提供すること。

【解決手段】本発明の一形態の設計データ作成方法は、半導体装置の設計データを作成する設計データ作成方法であって、パターンレイアウトに含まれるコンタクトホール層パターンを挟む上層配線パターンと下層配線パターンとのAND領域を抽出し(S31)、前記AND領域に含まれるコンタクトホール層パターンを抽出し(S32)、前記AND領域の中心と前記コンタクトホール層パターンの中心とが一致するように前記コンタクトホール層パターンを移動する(S33)。

(もっと読む)

LSIの配線構造

【課題】 配線容量C及び配線遅延RCの低減の可能なLSIの配線構造を提供する。

【解決手段】多層配線層を有する配線構造において、上層配線層では、配線の幅方向の配線間絶縁層の誘電率を、配線の厚み方向の配線間絶縁層の誘電率より相対的に高くした配線構造を有し、下層配線層では、配線の厚み方向の配線間絶縁層の誘電率を、配線の幅方向の配線間絶縁層の誘電率より相対的に高くする。

(もっと読む)

低減された誘電率を有する誘電体の製造方法、および半導体デバイス構成要素、および基板

【課題】低減された誘電率を有する誘電体、およびその製造方法を提供する。

【解決手段】第1の態様では、低減された誘電率を有する誘電体を製造する第1の方法を提供する。第1の方法は、(1)基板上のトレンチを含む誘電体層を形成するステップと、(2)誘電体の実効誘電率を減少させるために、トレンチの側壁および底部のうちの少なくとも一方に沿って、誘電体層内に複数の空隙を形成することにより、誘電体層内にクラッディング領域を形成するステップとを含む。他の多数の態様を提供する。

(もっと読む)

応力解析方法、配線構造設計方法、プログラム及び半導体装置の製造方法

【課題】半導体装置の高品質・高信頼化、及び半導体装置の生産効率の向上を実現可能な応力解析方法を提供する。

【解決手段】分割部が、チップ内を複数の解析エリアに分割するステップ(S10)と、複合物性値導出部が、複数の解析エリア毎の配線構造データに基づいて、複数の解析エリアのそれぞれについて、その解析エリアに含まれる複数の材料の物性値を複合した複合物性値を導出するステップ(S11,S12)と、応力解析部が、各解析エリアを要素とする有限要素法の3次元モデルを作成し、各要素に複合物性値を当てはめ、応力解析を行うステップ(S13,S14)とを含む。

(もっと読む)

レイアウト方法、CAD装置、プログラム及び記憶媒体

【課題】本発明は、レイアウト方法、CAD装置、プログラム及び記憶媒体に関し、素子のレイアウト時に素子のEMルールの違反によるレイアウトの作業工数の増大を防止し、TATの増大を防止することを目的とする。

【解決手段】回路のレイアウト設計において、回路のシミュレーションを行うシミュレーションステップと、回路を構成する素子の端子間を流れる最大電流値及び素子形状を指定する指定ステップと、素子のレイアウトを、指定された最大電流値及び素子形状に基づいて、エレクトロマイグレーション(EM)ルールを満足するように自動的に作成して完成するレイアウト合成ステップとを含むように構成する。

(もっと読む)

半導体デバイス製造プロセスモニタ装置および方法並びにパターンの断面形状推定方法及びその装置

【課題】

半導体デバイスの製造プロセスをモニタする装置において,被評価パターンの断面形状,あるいは被評価パターンのプロセス条件,あるいは被評価パターンのデバイス特性を,パターンを非破壊で計測可能にする。

【解決手段】

露光プロセス,あるいはエッチングプロセスにおいて,被評価パターンのSEM像から,被評価パターンの断面形状,あるいは前記パターンのプロセス条件,あるいは前記パターンのデバイス特性を推定するのに有効な画像特徴量を算出し,前記画像特徴量を予めデータベースに保存しておいたパターンの断面形状,あるいは前記パターンのプロセス条件,あるいは前期パターンのデバイス特性とSEM像から算出した前記画像特徴量とを関連づける学習データに照合することにより,被評価パターンの断面形状,あるいは前記パターンのプロセス条件,あるいは前記パターンのデバイス特性を算出する。

(もっと読む)

デバイス設計支援方法、デバイス設計支援システム及びデバイス設計支援プログラム

【課題】 メッキプロセスによって形成した金属膜のメッキ後の高さ分布を予測する。

【解決手段】 本発明では、設計CADデータから単位面積あたりの配線の側壁表面積からメッキ後のメッキ膜厚さ分布を予測する。また予測したメッキ膜厚さ分布からCMP後の高さ分布を予測する。

【効果】 本発明によれば、簡単な方法で精度良くメッキ後のメッキ膜高さ分布を予測可能であり、メッキ後のプロセスにおける高さ分布の予測も可能となる。

(もっと読む)

コンパクト・モデルにおける窒化物ライナ応力作用のレイアウトに基づく変更および最適化のための方法

【課題】 半導体デバイス(200)において、窒化物ライナ(260)応力のレイアウト誘発性の変化の影響を正確に明らかにするための、コンパクト・モデル・アルゴリズム(310〜350)のためのシステムおよび方法。

【解決手段】 レイアウト・センシティブ・コンパクト・モデル・アルゴリズム(310〜350)は、正確な応力応答近似を取得するためのアルゴリズム、および、応力応答を引き起こす正確な幾何学的パラメータを取得するためのレイアウト抽出アルゴリズムを実施することによって、回路に対する大きなレイアウト変動の影響を明らかにする。特に、これらのアルゴリズムは、検索「バケット」からの具体的な情報を含む。この「バケット」は、方向を重視したものであり、半導体デバイスの近傍の具体的な形状を詳細に分析するための、方向に特定的な距離測定値を含む。アルゴリズムは、更に、単一のストレス・ライナ膜およびデュアル・ストレス・ライナ(260)(界面において当接する2つの異なるライナ膜)を有するデバイスのモデリングおよび応力影響の決定を可能とするように適合されている。

(もっと読む)

欠陥の修正方法および欠陥修正装置

【課題】 様々な欠陥を効率よく修正することができるように改良された欠陥の修正装置を提供することを目的とする。

【解決手段】 欠陥の修正装置は、半導体装置または液晶表示装置の製造過程において欠陥を検出する欠陥検出・分析装置1と、欠陥の位置・形・サイズ・構成成分のデータを分析収集し記憶する記憶装置2と、この記憶された前記欠陥に関するデータと、回路設計レイアウトデータベース4および欠陥知識データベース5とを比較して電気的に不整合を引き起こす欠陥を抽出する欠陥自動分類・抽出処理部3と、抽出された前記電気的に不整合を引き起こす欠陥を修正するための対処方法を欠陥修正方法知識データベース7から選択する欠陥修正方法選択処理部6と、選択された欠陥修正方法により、欠陥を除去もしくは修復する欠陥修正装置8とを備える。

(もっと読む)

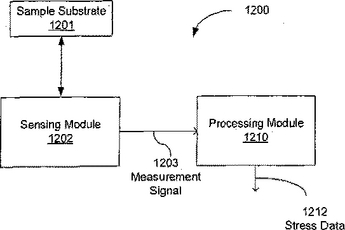

基板に集積した埋込み配線およびバイアのストレス解析および監視

埋込み配線フィーチャを有する層にストレス解析計算を適用してストレス情報を取得し、微細構造を設計し、そして生産プロセスを設計、管理するための技法およびシステム。  (もっと読む)

(もっと読む)

半導体装置

【課題】 半導体装置に関し、強誘電体キャパシタに印加される樹脂の吸湿による応力を実効的に低減して、安定した分極反転を可能にする。

【解決手段】 強誘電体キャパシタ1の上部電極4に接続する配線7の延在方向に沿って、強誘電体キャパシタ1を挟んで2つのプラグ5,6を配置する。

(もっと読む)

半導体装置

【課題】高密度容量化を達成できる容量素子を搭載した半導体装置を提供すること。

【解決手段】第1の方向に延在する第1電極Aの配線と、第1の方向に延在する第2電極Bの配線とが交互に配置された第1の層と、第2の方向に延在する第1電極Aの配線と、第2の方向に延在する第2電極Bの配線とが交互に配置された第2の層とが交互に積層された半導体装置であって、第1の層の第1電極Aである配線と第2の層の第1電極Aである配線がそれぞれ交差している部分で相互に接続する第1ビア21と、第1の層の第2電極Bである配線と第2の層の第2電極Bである配線がそれぞれ交差している部分で相互に接続する第2ビア22と、第1電極Aと第2電極Bとの間に設けられた誘電体とを備え、各配線は、第1ビア21又は第2ビア22を介して複数の他の配線と接続され、第1電極Aと第2電極Bとの間でキャパシタが形成される。

(もっと読む)

41 - 60 / 64

[ Back to top ]