Fターム[5F033VV07]の内容

半導体集積回路装置の内部配線 (234,551) | 配線の用途 (10,506) | ボンディングパッド、バンプ電極 (1,972)

Fターム[5F033VV07]に分類される特許

1,961 - 1,972 / 1,972

チタン・タングステンのベース層および関連構造体を含む導電構造体を形成する方法

基板、基板上の導電パッド、および基板上の絶縁層を含む電子デバイスを形成する方法であって、上記絶縁層は導電パッドの一部を露出するバイアホールを有する。詳細には、絶縁層上であり導電パッドの露出部分上に導電構造体を形成できる。導電構造体は、チタン・タングステン(TiW)のベース層と、アルミニウムおよび/または銅のうちの少なくとも1つの導電層とを含みうる。さらに、導電構造体のベース層を、導電層と絶縁層との間に形成できる。関連デバイスについても説明する。

(もっと読む)

(もっと読む)

半導体装置

【課題】ESD 保護回路のサージ電流経路に使用される配線層に生じる熱を効率よく放熱でき、サージ電流経路に使用される配線層も保護する。

【解決手段】外部端子と内部回路との間の配線に接続され、外部端子に印加された過大な静電サージ入力から内部回路を保護する保護素子を有する入力保護回路と、入力保護回路に接続され、そのサージ電流経路に含まれる第1のメタル配線層25と、第1のメタル配線層に連なり、熱伝導性が良好な材質の配線を用いてなる放熱器20とを具備する。

(もっと読む)

化合物半導体発光素子の製造方法

【課題】 本発明は、1回のワイヤボンディングで済み、位置合わせの容易な実装が可能で、工数の低減につながるチップを作製することを課題とする。

【解決手段】 基板11の一面上に、n型半導体薄膜層13と、活性層と、p型半導体薄膜層17とを積層形成し、このp型半導体薄膜層17上面に一方の電極32を基板11の他面上に他方の電極33aを設ける化合物半導体発光素子の製造方法において、基板11の他面側から電極33aと接続されるn型半導体薄膜層13に到達する深さの縦穴20を波長が500nm以下の短波長レーザを照射して設け、基板11の他面に設けた電極33aとn型半導体薄膜層13を縦穴20に形成した導電性材料30を介して電気的に接続し、電極32を基台100の第1のリード電極101に接続し、電極33aを第2のリード電極103にワイヤボンド線104で接続する。

(もっと読む)

銅コンタクトを有する集積回路ダイおよび該集積回路ダイのための方法

集積回路ダイ(10)は、銅コンタクト(16,18)を有する。銅コンタクトは、周辺空気にさらされると天然の酸化銅を形成する。有機材料を、銅コンタクトに塗布する。有機材料は、天燃の酸化銅と反応して、銅コンタクト上に有機コーティング(12,14)を形成し、さらなる銅の酸化を防ぐ。このようにして、たとえば100℃を上回る高温でさらに処理を行なっても、過剰な銅の酸化によって妨げられることはない。たとえば高温でワイヤ・ボンド・プロセスを行なっても、有機コーティングのために、信頼性の高いワイヤ・ボンディングを妨げる過剰な酸化には至らない。したがって、有機コーティングを形成することによって、信頼性が高くかつ耐熱性のあるワイヤ・ボンド(32,34)が可能になる。あるいは、集積回路ダイを形成する間のいつでも、露出する銅に有機コーティングを形成して、銅の酸化の形成を防止または抑制することができる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】半導体チップ上に絶縁膜を介して外部端子と再配線とが形成される半導体装置において、従来は外部端子、若しくは再配線からのノイズの影響から電子回路を保護する為、接地電位層を設けていたが、この接地電位層の為に工程が大幅に増加し、さらに、半導体装置の厚さが厚くなってしまう可能性があった。

【解決手段】本発明では、基板上の多層配線、即ち、それぞれが層間絶縁膜を介して積層された複数の層と、それぞれの層内に形成された配線とを有する多層配線の最上位の層内において、配線が配置された領域以外の領域に、定電位が与えられるノードに電気的に接続するメタル部材が形成される。これにより、工程を大幅に増加することなく、かつ、半導体装置の厚さを厚くすることなく、電子回路がノイズの影響を受けてしまう可能性を低減することができる。

(もっと読む)

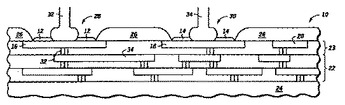

フリップチップFET素子

【課題】電力素子のオン状態抵抗、放熱特性、インダクタンスを改善する。

【解決手段】半導体素子は導電パッド領域26,36を含み、各々の導電パッド領域は複数の金属トレースに電気的に接続される。複数の金属トレースは各々が順番に拡散に接続される。はんだバンプやビアなどの導電接点素子は各々の導電パッド領域に取り付けられ、導体素子が第1のピッチを有する反復パターンに配列され得る。半導体素子は平行移動トレース50,60も含み、各々の平行移動トレースは2つ以上の導電接点素子に電気的に接続され得る。各々の平行移動トレースはそこに取り付けられる相互接続素子を有し得る。相互接続素子は第1のピッチより実質的に大きい第2のピッチを有する反復パターンに配列され得る。

(もっと読む)

半導体装置及びその製造方法

【課題】ボンディングパッドの下層におけるクラックの発生を抑制しつつ、ボンディングパッドの下層を有効活用して装置の小型化を図る。

【解決手段】半導体装置10は、半導体基板11と、外部との電気的接続をとるための接続領域12aを有するボンディングパッド12と、半導体基板11とボンディングパッド12との間に介在する第1層間絶縁層13と、第1層間絶縁層13に埋設されたメタル配線層14とを備える。メタル配線層14は第1層間絶縁層13より硬度の小さい材質からなる。メタル配線層14の少なくとも一部は、積層方向において接続領域12aと重なり、接続領域12aと重なるメタル配線層14の領域には、積層方向に貫通し、メタル配線層14をその層方向において分離している切欠部30a〜30eが形成されているとともに、この切欠部30a〜30eに第1層間絶縁層13の一部が埋め込まれている。

(もっと読む)

多層微細配線構造およびその作製方法

【課題】 高速情報処理用デジタル集積回路チップ内およびそのチップを搭載するためのパッケージ、モジュール、ボードなどの実装系内における多層配線の作製方法に関する新しい多層微細配線構造およびその作製方法を提案する。

【解決手段】 高解像感光性ポリイミドを絶縁層として、銅、銀、金、アルミニウム、パラジウム、ニオブなどの金属を配線層として用いて、ストリップライン、マイクロストリップライン、同軸ラインなどの伝送線路構造を有する多層微細配線構造を実現するため、広い周波数帯域について、インピーダンスが一定に制御され、デジタル高速信号伝送に適する線路を実現することができる。高解像特性を有する感光性ポリイミドを絶縁層として用いることにより、絶縁層へのビア穴加工がリソグラフィ工程のみで達成され、また、金属配線層をリフトオフ法によりパターン形成することにより、従来の多層配線技術に比べて、高密度の配線構造が実現でき、大幅に工程が簡略化される。

(もっと読む)

半導体装置およびその製造方法

【課題】 ポストの配置や形状を変えることなくチップの向きを一目瞭然にすることができる半導体装置およびその製造方法を実現する。

【解決手段】 ダイシングにより個片化された時に、チップの一辺側面に切削残留して露出する識別ポスト20を設けたので、従来のように、ポスト6の配置や形状を変えることなく、チップの向きが一目瞭然になる。また、チップの向きを表すマークとなる識別ポスト20は、チップの一辺側面に露出される為、チップを傾ければ、チップの表面側や裏面側からでもチップの向きを識別でき、ハンドリング性が向上する。

(もっと読む)

配線基板の製造方法、半導体装置及びめっき装置

【課題】 導体層の研磨中に導体層の剥がれを防止できる配線基板の製造方法を提供することを目的とする。

【解決手段】 基板10の一方の面10aに少なくとも孔10bを形成する工程と、基板10の一方の面10a上、他方の面10e上及び側面10f上と、孔10bの内面上とに、めっき給電層14を形成する工程と、電解めっきにより、めっき給電層14を介して、基板10の一方の面10a上、他方の面10e上及び側面10f上に形成され、かつ孔10bを埋め込む金属層18を形成する工程と、金属層18を研磨することにより、孔10bに金属層18が埋め込まれた金属層のパターン17a,17bを形成する工程とを有する。

(もっと読む)

半導体チップ、配線基板およびそれらの製造方法ならびに半導体装置

【課題】複数の半導体チップを配線基板に積層しても、半導体チップを積層した半導体装置の厚みおよび基板面積の増大および半導体チップ間の配線長の増加を招かない半導体チップ、その製造方法および半導体装置等を提供する。

【解決手段】半導体基板13と、半導体基板13の第1の面14に形成された第1の外部電極21と、半導体基板13の第2の面17に形成された第2の外部電極22と、半導体基板13に形成された貫通孔16とを有し、貫通孔16は第2の面17となす内角が鈍角をなして形成された斜面15に設けられ、第1の外部電極21と第2の外部電極22とは、貫通孔16の内壁および斜面15を経由して形成された導電パターン19により電気的に接続されている。

(もっと読む)

半導体装置及びその製造方法

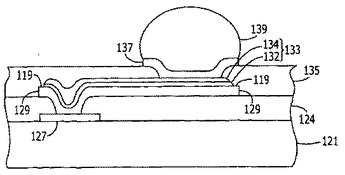

【課題】チップサイズパッケージの実装時における信頼性を向上させる。

【解決手段】上面の面積を底面の面積より大きくすると共に、側面をくびれ形状に湾曲させた柱状端子9を形成し、この上に半田ボール12を搭載する。これにより、柱状端子9と半田ボール12の接触面積Sが従来のSに比して大きくできるため、せん断応力に対する強度を向上することができる。また、くびれ形状に湾曲させたことにより、剛性が低減し(つまりしなやかになり)、弾力性が増すことで、応力緩和性能も改善される。

(もっと読む)

1,961 - 1,972 / 1,972

[ Back to top ]