Fターム[5F033XX22]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | 放熱 (140)

Fターム[5F033XX22]に分類される特許

101 - 120 / 140

相変化メモリ装置およびその製造方法

【課題】相変化メモリ装置のメモリセル部における、相変化領域の上側ならびに下側の金属からの放熱を共に抑制し、熱効率の低下を最小限化して、大規模な相変化メモリ装置の量産を可能とすること。

【解決手段】相変化層の下側のコンタクトプラグからの放熱は、異種材料コンタクトプラグ104を採用して抑制する。すなわち、第2の導電材料に比べて比抵抗が大きい(逆に、熱伝導率は小さい)第1の導電材料からなる第1の導電材料プラグ106にヒータ電極110を接続することによって、放熱を抑制する。相変化層の上側の電極からの放熱は、引き出し電極116を用いた、相変化領域(ヒータ電極110の上面112の近傍)の直上に電極を設けない電極構造の採用によって抑制する。

(もっと読む)

ダマシン配線の形成方法

【課題】ダマシン法により基板に配線パターンを形成する配線形成方法であって、配線形成時にボイド等の不具合発生が無く、信号遅延を低減することのできるダマシン配線の形成方法を提供する。

【解決手段】基板に配線パターンを形成するダマシン配線の形成方法であって、前記基板に形成された絶縁膜2に配線パターンとする溝部2aを形成するステップと、分散剤6に溶かした炭素ナノ物質7の分散溶液5を前記絶縁膜2上に塗布し、該分散溶液5を前記溝部2aに埋め込むステップと、前記分散溶液5の溶媒を蒸発させるベーク処理を行うステップと、前記分散剤6を蒸発させ、炭素ナノ物質7の膜を焼成するアニール処理を行うステップと、前記溝部2a上の余分な炭素ナノ物質7の膜を除去し前記溝部2aに沿った配線パターンを形成するステップとを実行する。

(もっと読む)

犠牲相互接続部を用いたオンチップ相互接続スタック冷却

本発明は、流体冷却チャネルを集積された集積回路デバイス、およびこうした集積回路デバイスを製造する方法に関するものである。この方法は、絶縁層シーケンス内の電気相互接続部の横方向の所望位置、および流体冷却チャネル部の横方向の所望位置に凹部を形成するステップを備えている。この絶縁層シーケンスの凹部内に金属充填物を堆積させて、流体冷却チャネル部内に電気相互接続部および犠牲的充填物を形成する。その後に、この犠牲的金属充填物を、流体冷却チャネル部から選択的に除去する。  (もっと読む)

(もっと読む)

半導体装置

【課題】半導体チップに複数の半導体素子が形成されている半導体装置において、従来の半導体装置と比較して、半導体チップの面積を縮小できる半導体装置を提供する。

【解決手段】半導体チップの表面に平行な面方向において、パワー素子領域aよりも領域が狭い制御回路素子領域bがパワー素子領域aと完全に重複するように、半導体チップの内部に、絶縁分離されたパワー素子領域aを有する第1のSOI層4と、絶縁分離された制御回路素子領域bを有する第2のSOI層7とを、半導体チップの表面に垂直な方向に並んで配置させる。

(もっと読む)

半導体装置、および半導体装置の製造方法

【課題】半導体装置の小型化を実現すると同時に半導体装置の動作時の発熱を廃棄することの可能な半導体装置および斯かる半導体装置の製造方法を提供する。

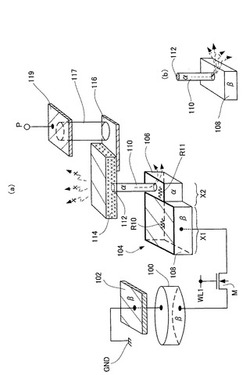

【解決手段】接地面に設けられ、半導体ウエハ102上に配線および電極端子パターン104、106が形成されている半導体装置100において、かかる電極端子パターンのうち、接地面と接続する電極端子パターンが形成されている部位には、かかる部位に設けられた電極端子パターンを貫通するようにして半導体ウエハに導通孔108が形成され、半導体ウエハには、この半導体ウエハの配線および電極端子パターンが形成されている面102aと反対側の面102bから導通孔の底部108aに達するまで、径が導通孔の各底部を包含可能な大きさである孔部110が形成され、かかる孔部には各底部および接地面を電気的に接続する一の導電体112が設けられている。

(もっと読む)

相変化メモリ装置および相変化メモリ装置の製造方法

【課題】相変化メモリ装置における良好な電気特性と良好な熱特性を両立させ、電極や配線の材料選択の自由度も高めて、大規模な相変化メモリ装置の量産を可能とすること。

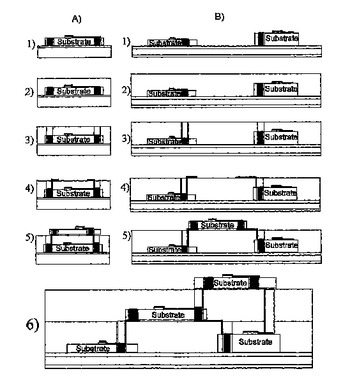

【解決手段】ヒータ電極110と相変化層114の接触界面112の近傍で発生するジュール熱が、ヒータ電極110を介して下方に伝達され、下地の良導電性の金属コンタクトプラグから放熱されることを抑制するために、異種材料コンタクトプラグ104(106,108)を採用する。ヒータ電極110に接触する第1の導電材料プラグ106は、ヒータ電極110の構成材料と同種または同じ金属材料からなり、第2の導電材料プラグ108は、接地電位用プラグ100や接地配線102と同種あるいは同じ金属材料からなる。両プラグ106,108は、共通のコンタクトホール内に積層形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体素子等に起因して発生する熱を効率よく放熱する。

【解決手段】半導体装置は、半導体基板11と、半導体基板に設けられた第1の拡散領域12と、第1の拡散領域12に設けられた半導体素子17と、第1の拡散領域12に設けられ、かつ冷却用の流体が供給される通路14とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】裏面のグランド層を容易に形成するとともに、ビアホールを位置合わせが容易に形成する。

【解決手段】ウェハ1の半導体集積回路が形成されている側の表面11に形成された第1のホール2と、ウェハ1の裏面12に形成された第2のホール3とを有し、1個の第2のホール3と複数個の第1のホール2とがつながってウェハ1を貫通するビアホール4が構成され、ビアホール4には埋め込み金属層5が埋め込まれ、ウェハ1の裏面12の全体にはグランド層6が形成されている。

(もっと読む)

ヒューズ素子及びその切断方法

【課題】ヒューズ回路を大きくすることなく層間絶縁膜のクラックを防止できるとともに、ヒューズ切断前後において大きな抵抗変化を得ることができるヒューズ素子及びその切断方法を提供する。

【解決手段】シリコン層を含む配線部14と、配線部14の一端側に接続されたコンタクト部20bと、配線部14の他端側に接続されたコンタクト部20aとを有するヒューズ素子において、コンタクト部20bからコンタクト部20aへ配線部14を介して電流を流し、コンタクト部20aの金属材料をシリコン層中にマイグレーションさせることにより、配線部14とコンタク部20aとの間の接続抵抗を変化させる。

(もっと読む)

半導体装置およびその製造方法

【課題】 隣接する素子への影響を可及的に低減することを可能にする。

【解決手段】 Ge基板2に設けられた空孔6aと、空孔の上面を覆いGeを含む絶縁膜6bと、を備えている。

(もっと読む)

背面多層信号ルーティングを有するMMIC

MMICチップを有する単結晶ウェハを提供することを含む方法。各チップは、ウェハによって設けられる半導体基板の第1の表面部分にある能動デバイスと、半導体基板の第2の表面上に配置される第1の部分を有する電気配線とを有する。半導体基板の構造は、その中を貫通するバイアを有し、電気配線の第2の部分は、バイアの中を通って、能動デバイスに電気的に接続される。多層配線構造がウェハ上に形成され、チップのうちの対応するチップの第2の表面部分の上に信号ルーティングセクションを設ける。各セクションは誘電体層及び電気導体を有し、そのような電気導体は、能動デバイスに電気信号をルーティングするために、そのような能動デバイスに電気的に結合される。各チップ及び対応する信号ルーティングセクションが、ウェハから切り離される。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】 特許文献1に記載のSOI基板においては、絶縁膜の熱伝導率が高くても、厚い支持基板によって放熱が妨げられてしまう。

【解決手段】 半導体装置1は、SOI基板10、配線層20、および素子分離領域30を備えている。SOI基板10は、支持基板12、支持基板12上に設けられた絶縁膜14(基板絶縁膜)、および絶縁膜14上に設けられたシリコン活性層16(シリコン層)を有している。支持基板12の厚さは、好ましくは10μm以上150μm以下である。絶縁膜14の熱伝導率は、常温で、シリコン活性層16も低く且つSiO2よりも高い。

(もっと読む)

半導体装置及びその製造方法

【課題】 ヘテロ接合半導体素子と別の半導体素子とが同一基板上に集積され、かつ、この別の半導体素子の電極取り出し構造が改良された半導体装置及びその製造方法を提供すること。

【解決手段】 前記別の半導体素子の一例である抵抗素子20を構成する抵抗層11を、イオン注入法または不純物拡散法によって半絶縁性基板1内に形成する。次に、サブコレクタ層2、コレクタ層3、ベース層4、エミッタ層5、そしてエミッタキャップ層6の構成材料層を、基板1の全面にエピタキシャル成長法によって形成する。次に、これらの一部をメサ構造に加工して、HBT10を形成する。一方、抵抗素子20の素子電極14、15を高い位置で取り出すための導電層12、13を、サブコレクタ層2の構成材料層42のパターニングによって形成し、素子電極14、15をこの上に形成する。次に、BCBなどの平坦化膜30を形成し、これを介して配線31、32を形成する。

(もっと読む)

チップの架橋接続

システムは、第1半導体デバイスと第1電気接続とを有する第1チップ、第2半導体デバイスと第2電気接続とを有する第2チップ、および第3半導体デバイスと第3電気接続とを有する第3チップを有し、第3チップは、第1および第2チップの上面にスタックされ、第1および第2チップのそれぞれの少なくとも一部分を物理的に架橋し、前記第1および第2チップに接続される。  (もっと読む)

(もっと読む)

集積電子回路上にマスクを形成する方法

【課題】集積電子回路の基板上の、基板内に埋められたキャビティの上方の位置に、回路部材を容易に形成できるようにする。

【解決手段】集積電子回路の基板100内に形成されたキャビティCの上方が閉じられ、くぼみEが形成されている。くぼみEは、リソグラフィ放射線F1の反射を弱くするように選択された材料10で埋められている。レジスト層3が回路上に積層された後に放射線を照射すると、レジスト層3の、くぼみEの上方に位置する部分は、1次フラックスF1のみによりレジストの現像のしきい値よりも小さい放射線量にさらされる。レジスト層3の、くぼみの外側にある部分は、1次フラックスF1と、基板100の表面で反射された2次フラックスF2により、しきい値よりも大きい放射線量にさらされる。レジスト層3を現像すると、キャビティCの上方のみに位置するマスクM2が得られる。

(もっと読む)

薄膜トランジスタおよび液晶表示装置

【課題】信頼性を向上できる薄膜トランジスタを提供する。

【解決手段】活性層5のソース領域7およびドレイン領域8の長手方向の中央部から両端部に向けてコンタクトホール13a,13b,13c,13d,13eの間隔を徐々に狭くする。通電時の活性層5の放熱量が長手方向の中央部より両端部のほうが小さい。活性層5の長手方向の中央部での放熱性が両端部での放熱性より良くなる。活性層5のチャネル領域に電流が流れて自己発熱したときに、チャネル領域の長手方向の中央部での局所的な温度上昇を抑制できる。通電時の自己発熱をチャネル領域全体に亘って平均化できる。

(もっと読む)

半導体チップ及び半導体チップパッケージ

【課題】半導体チップ内部のアクティブ素子の損傷なしに内部に発生した熱を効果的に放出させることによって、チップの動作信頼性を向上させ得る半導体チップ及び半導体チップパッケージを提供すること。

【解決手段】 複数の単位素子からなるチャネルをそれぞれ複数備える複数のチャネルブロック133と、外部とのデータ送受信のために、複数の単位素子とそれぞれ接続した複数の第1金属配線と、第1金属配線によって伝達されたデータ信号を外部で接続する複数のノーマルバンプ139と、チャネルブロックの間の空間に配置され、基板又は複数のウェル領域に接続した複数の第2金属配線と、チャネルブロックの駆動時に発生する熱を第2金属配線を介して外部配線に伝達するための第2金属配線上に配置された複数の第1熱伝逹バンプ138とを備える。

(もっと読む)

金属基板に接着された半導体基板用のビア構造およびトレンチ構造

ヒ化ガリウム基板のような化合物半導体基板は、共融して金属基板(400)に接着されている。半導体基板は状況に応じて薄くされる、そして、ビアまたはトレンチ(601)が、整合した相互接続を容易にするために、前面から金属基板(400)まで形成される。金属基板(400)によって与えられる機械的支持により、ビアまたはトレンチ(601)がどんな形であることも可能になる。トレンチ(601)は、熱隔離または熱拡散を与える、または(金属エア・ブリッジと組み合わせて)電磁遮蔽を可能にするために、特定の回路素子を取り囲むことができる。トレンチ構造物(601)は、また、標準的なビア・ホールと比較して、超短波で低いインピーダンスの接地接続を可能にする。金属基板(600)を、接地面として、またはヒート・シンクとして使用することができる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 単位基板あたりの半導体チップ数を増加できる半導体装置の製造方法を提供する。

【解決手段】 この半導体装置の製造方法では、半導体基板1の主面S1に切断すべき部分1hを露出する様にしてマスク7を形成し、そのマスク7に基づき前記切断すべき部分1hをエッチングにより切断することにより、半導体基板1を個々の半導体チップに分割する。

(もっと読む)

半導体装置、半導体本体並びにその製造方法

この発明は、内部にICが形成され、表面上にICのための多くの接続領域(1)を有し、少なくとも二つの接続領域(1A)が供給接続のためである半導体本体(11)を備えた半導体装置(10)であって、半導体本体(11)の下側に多くのさらなる電気的接続領域(2)が設けられ、これらは、半導体本体(11)の側面上に存在し、そこから電気的に絶縁されている電気的接続部(3)により接続領域(1)に接続され、半導体本体(11)はリードフレーム(4)に固定され、ワイヤ接続部(5)がリードフレーム(4)のリード(4A)と接続領域(1)との間に形成されている。この発明によれば、電気的接続部(3)は複数の平行で、等間隔で配置されたストリップ状導体(3A)を備え、そして、供給接続のための接続領域(1A)が、各々、二つ又はそれ以上のストリップ状導体(3A)により、さらなる接続領域(2)に接続され、このさらなる接続領域は直接フレーム(4)のリード(4B)に接続され、接続領域の残部(1B)はワイヤ接続部(5)により直接リード(4)に接続される。このような装置(10)は供給電圧が非常に安定であり、高周波での動作に優れており、供給電流も非常に大きくなる。この発明は、さらに、そのような装置(10)に用いるのに適した半導体本体(11)とそのような装置(10)を製造する方法を備える。  (もっと読む)

(もっと読む)

101 - 120 / 140

[ Back to top ]