Fターム[5F033XX22]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | 放熱 (140)

Fターム[5F033XX22]に分類される特許

21 - 40 / 140

ビアホールの製造方法およびビアホールを有する半導体素子の製造方法

【課題】内部への埋め込み材料を増量させて放熱性向上効果を得ることが可能なビアホール構造を、ビアホール形成のための半導体基板へのエッチングの回数を少なくしつつ製造することのできるビアホールの製造方法およびビアホールを有する半導体素子の製造方法を提供する。

【解決手段】メタルマスク8は、メタルマスク10の開口23により露出させられた部分8aを有する。メタルマスク10は、メタルマスク8よりも厚く形成する。メタルマスク10の厚さは、開口23内のエッチングが半導体デバイス形成層4にほぼ到達すると同時に、開口22のエッチングがソース電極1に到達する厚さに設定する。

(もっと読む)

成膜付半導体素子、及びその製造方法

【課題】半導体素子を破壊することを防止しつつ半導体素子の金属膜に対し安価に成膜できるとともに容易に厚膜化できる成膜付半導体素子の製造方法を提供すること。

【解決手段】シリコン層11に重ねてアルミ膜12を有する半導体素子10に対しコールドスプレー装置30によって成膜する成膜付半導体素子の製造方法は、第1工程と、第2工程とを有する。第1工程では、コールドスプレー装置30が、アルミ膜12の厚さV1より小さい粒径R1の第1銅粉末41を噴射することにより、アルミ膜12の表面に下地層21を形成する。第2工程では、コールドスプレー装置30が、第1銅粉末の粒径R1より大きく且つ下地層21の表面からアルミ膜12とシリコン層11との境界面までの寸法V2より小さい粒径R2の第2銅粉末42を噴射することにより下地層21に重ねて厚膜層22を形成する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】 基板を薄くしてもその反りを防止するTSV構造の製造方法を提供する

【解決手段】本発明の半導体装置の製造方法は、半導体基板の表面に半導体素子を集積させて回路の少なくとも一部を形成する工程と、半導体基板の表面から穴を開ける工程と、穴の内表面に絶縁膜およびバリア膜を形成する工程と、バリア膜の表面に、穴を埋めるように導電性金属を形成する工程と、半導体基板の裏面を加工して厚さを減少させ、導電性金属を突出させる工程と、半導体基板の裏面にSiCN膜を設ける工程とを有する。

(もっと読む)

半導体チップ及びそれを搭載した半導体モジュール

【課題】半導体チップに安定した電源電流を供給したり、電源から信号系へ混入する雑音を低くするための、半導体デバイスの電源流入及び電源流出端子の端子数の低減と、前記半導体チップを搭載した実装面積の低減を可能とする半導体モジュールを提供する。

【解決手段】半導体チップ20の両面に電源系と信号系の電気的接続端子を振り分けて配置する。大電流が流れる流路の許容電流値を大きくする構成により、少ない端子数でも安定な電源供給が可能、信号系への雑音混入を低減、ピン数の低減による実装面積の低減、放熱効果の増大などが可能となる。また、この半導体チップ20を搭載した半導体モジュールにより、大電流が流れる高速動作でも安定した特性を実現できる。

(もっと読む)

熱の抽出及び遮蔽のための埋込み式熱伝導層

【課題】多ブロック半導体デバイスにおいて熱を抽出しかつ遮蔽するための方法及び装置。

【解決手段】一実施形態は、互いに上下して積み重ねられる複数のブロック205,305は、熱伝導材料で充填される垂直バイア240,350によって相互に接続され、かつ埋込み式の熱伝導層340によって分離される。熱伝導層は、複数のブロックのうちの一番上または下へ熱抽出層または接地平面として接着される。熱伝導層は、高い熱伝導率を有する。基板110上には、断熱層210,320が堆積される。断熱層は、基板の加熱を低減するための温度勾配をサポートすることができる。断熱層の内部には埋込み式の熱伝導層が形成され、これは、基板を介して外部の熱抽出層へ接続される垂直バイアを有する。半導体層はこの断熱層上へ堆積され、電気配線用にパターン化される。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】Cuを主要な成分とする再配線に設けられた外部接続用Auパッドの剥離を抑制する。

【解決手段】Cu膜15aの上部にNi膜15bを積層した2層膜からなる再配線15の表面には、ワイヤが接続されるパッド18が形成されている。パッド18は、Ni膜19aの上部にAu膜19bを積層した2層膜からなり、再配線15の上面および側面を覆うように一体形成されている。これにより、再配線15とパッド18の接触面積が大きくなるので、パッド18が再配線15から剥がれ難くなる。

(もっと読む)

半導体装置及びその製造方法

【課題】3次元集積化技術を適用した場合にも十分な放熱効果が得られる、放熱効率の高い放熱構造を持つ半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1の素子形成面の反対面1bには、貫通電極2の少なくとも端面を露出させる第1の凹部3と、貫通電極2を露出させない第2の凹部8とが形成されている。半導体基板1の反対面1b上には、第1の凹部3における貫通電極3の端面を除く内面及び第2の凹部8の内面を覆うように第1の絶縁膜4が形成されている。第1の絶縁膜4上には、貫通電極2の端面と接続し且つ第1の凹部3の外側まで延びる導電膜5が形成されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】チップ面積及びコストを増大させることなく、熱抵抗を低減できる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体装置100は、半導体層1aと配線層1bとを有する半導体基板1と、半導体層1aの中央部に半導体層1aの表面から所定の深さまで形成された活性領域3と、活性領域3及び活性領域3の周辺の配線層1bに形成され、半導体層1aと電気的に接続された接続用電極4と、半導体層1aから発生する熱を放熱する放熱部とを備え、放熱部は、半導体層1aの裏面から活性領域3の近傍まで凹状に形成された少なくとも1の第1の孔5に充填された放熱体7を有する。

(もっと読む)

半導体装置、電子装置、及び半導体装置の製造方法

【課題】第1半導体チップで発生した熱を、熱伝導端子を介して実装基板に放熱することができ、かつ第1半導体チップにクラックが発生することを抑制できるようにする。

【解決手段】第1半導体チップ200は、配線基板100の第1面(本実施形態では裏面)にフリップチップ実装されている。接続端子120は例えばハンダボールであり、配線基板100の第1面に設けられている。熱伝導端子220は、第1半導体チップ200のうち配線基板100に対向しない面に設けられており、互いに離間している。

(もっと読む)

3次元集積のための裏側ダミー・プラグを含む半導体構造およびこれを製造する方法

半導体チップおよびこれを用いた半導体装置

【課題】接続導体との間のはんだ接合部の信頼性を確保する。

【解決手段】ジンケート法による無電解めっき法を用いて、半導体チップ1の表面側のAl電極3の上にNiめっき層5が形成される。Al電極3の上には、選択的にNiめっき層5が析出されるため、周辺耐圧構造4部分には、Niめっき層5は形成されない。また、形成されるNiめっき層5は、所定の厚さに均一に形成することができる。続いて、Niめっき層5の上にAuめっき層6が形成される。無電解めっき法を用いることによって、Auめっき層6もNiめっき層5と同様に、Niめっき層5の上に選択的、かつ均一に形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】簡便に半導体集積回路を小領域に電気的に分離する。

【解決手段】厚さが150〜600μm程度のInP基板、GaAs基板等の化合物半導体基板1の表面に半導体集積回路2を形成し、化合物半導体基板1の裏面(半導体集積回路2が形成された表面とは反対側の面)に、直角に交わっている複数の切込溝3を設け、半導体集積回路2の表面から切込溝3の底面までの距離を50〜150μmとし、切込溝3内にAu等の金属4を埋め込み、金属4を化合物半導体基板1の裏面全面にも設ける。

(もっと読む)

プロセス均一性及び熱消散を改善するダミーTSV(スルーシリコンビア)

【解決手段】

各々が能動回路領域を含むチップの積層体において、多重チップ積層体内の複数のスルーシリコンビア(TSV)開口をパターニングし、エッチングし、そして熱的伝導性材料で充填することによって、多重チップ積層体からの熱を熱的に伝導させるための複数のTSV構造が形成され、複数のTSV開口は、いずれの能動回路領域をも貫通せずに多重チップ積層体の実質的に全体を通って延びる第1の大きなTSV開口と、能動回路領域まで下に延びるが通過はしない第2の小さい開口と、を含む。

(もっと読む)

三次元集積回路用の層間充填材組成物、塗布液、三次元集積回路の製造方法

【課題】 少ない無機フィラーの含有量であっても、より熱伝導性が高い充填層を形成することができる層間充填材組成物を提供すること。

【解決手段】 三次元集積回路用の層間充填材組成物が、微粒子状樹脂フィラー、熱伝導度が1W/m・K以上の無機フィラー、及びマトリックス樹脂を含有し、かつ該層間充填材組成物100体積%あたり、微粒子状樹脂フィラーを1体積%以上50体積%以下、無機フィラーを1体積%以上80体積%以下含有する。

(もっと読む)

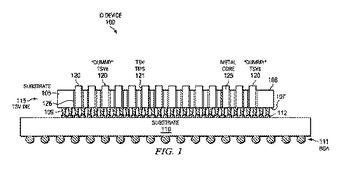

ICデバイスのエンハンストされた熱放散のための突出するTSV

集積回路デバイス(100)が、基板パッド(102)を含む上面を有する基板(110)、及び能動回路を含む上部半導体表面(107)と(底面)106とを含む半導体基板(105)を含む複数の基板貫通ビア(115)ダイを含む。上部半導体表面(107)は、基板の上面上の基板パッドに結合されるボンドコネクタ109を含む。複数の基板貫通ビア(TSV)が、底面から外に延びる突出するTSVティップ(121)に上側半導体表面から延びる内部金属コア(125)を含む。複数のTSVの少なくとも1つが、そこへの如何なる電気的接続もない、突出するTSVティップを有し、TSVダイの底面からの熱消散を可能にするための付加的な表面領域を提供するダミーTSV(120)である。

(もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】発熱に対して効率的に冷却を行うことができる、半導体装置を提供する。

【解決手段】半導体層の表面に形成された活性領域5,6と、N型の不純物を有する半導体から成るN型ゲート7Nと、P型の不純物を有する半導体から成るP型ゲート7Pと、N型ゲート7N及びP型ゲート7P及び活性領域5,6に接続された第1の金属配線13と、P型ゲート7P及びN型ゲート7Nに接続された第2の金属配線と15、第2の金属配線15に接続され、熱を外部に放出するための放熱部19とを含む冷却機構素子を備えた半導体装置を構成する。

(もっと読む)

金属キャリアを有する半導体デバイスおよび製造方法

【課題】 金属キャリアを有する半導体デバイス及び製造方法を提供する。

【解決手段】 金属キャリア基板を含む半導体デバイス。キャリア基板の上には、Alx1Gay1Inz1N(x1+y1+z1=1、x1≧0、y1≧0、z1≧0)の第1の半導体層が形成される。第1の半導体層の上にはAlx2Gay2Inz2N(x2+y2+z2=1、x2>x1、y2≧0、z2≧0)の第2の半導体層が配され、第2の半導体層の上にはゲート領域が配置される。半導体デバイスはさらに、ソース領域およびドレイン領域を含み、これらの領域のうちの一方が金属キャリア基板と電気的に接続され、第1の半導体層を介して延在する導電性領域を含む。

(もっと読む)

電子デバイスの製造方法および該方法により製造された電子デバイス

GaAs半導体基板(HS)を備えた電子デバイスにおいて、基板前面には半導体素子(BE)が、基板背面には多層の背面金属化部(RM)が設けられている。このような電子デバイスのために、背面金属化部の有利な積層体構造が提案される。たとえば背面金属化部は固着層としてAu層を有している。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】放熱性が向上した半導体装置およびその製造方法の提供。

【解決手段】第1の辺を有する第1の面を有する半導体基板10と、前記半導体基板上に設けられた電極14と、前記電極の上に位置する第1の開口部24を有する第1の絶縁層16と、前記第1の絶縁層の上であって、前記電極の少なくとも一部を避けて設けられた樹脂層20と、前記樹脂層の上に設けられた第1の部分31と、前記第1の部分と前記電極とを電気的に接続する第2の部分32と、前記第1の部分または前記第2の部分と電気的に接続する第3の部分33と、を有する導電層と、前記導電層の前記第2の部分を覆うように設けられ、前記導電層の前記第1の部分の少なくとも一部の上に位置する第2の開口部41を有し、かつ、前記導電層の前記第3の部分を避けて設けられた第2の絶縁層40と、前記導電層の前記第3の部分は、前記第1の面の前記第1の辺と、前記第2の絶縁層との間に位置する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体素子の電極パッド間の距離の縮小や半導体素子のサイズを拡大することなく多ピン化への対応が可能となり、回路コア部の電源の出力電圧が降下するIRドロップ現象を防止することができる半導体装置を提供する。

【解決手段】半導体素子3の回路形成領域4の外周部に外周部電極パッド5が形成され、各外周部電極パッド5に外周部バンプ10が形成され、回路形成領域4の範囲内に内部電極パッド14が形成され、内部電極パッド14に内部バンプ16が形成され、フリップチップ実装により、半導体素子3と半導体基板との間にエポキシ系樹脂材を介在させて、各外周部および内部バンプ10,16と半導体基板の各配線電極部とが接続される。

(もっと読む)

21 - 40 / 140

[ Back to top ]