Fターム[5F038AR20]の内容

Fターム[5F038AR20]に分類される特許

1 - 20 / 51

半導体装置

【課題】導体半導体接合を用いて、優れた特性を示す、あるいは、作製の簡単な、あるいは、より集積度の高い電界効果トランジスタを提供する。

【解決手段】半導体層の電子親和力よりも仕事関数の小さな導体との接合においては、導体より半導体層にキャリアが注入された領域が生じる。そのような領域を電界効果トランジスタ(FET)のオフセット領域、あるいは、インバータ等の半導体回路の抵抗として用いる。また、ひとつの半導体層中にこれらを設けることにより集積化した半導体装置を作製できる。

(もっと読む)

過電流保護回路

【課題】入力電源電圧の動作保証範囲が大きいとしても当該電圧変動の影響を抑制して正常に過電流保護を図るようにした過電流保護回路を提供する。

【解決手段】支持基板10が第1半導体層11および第2半導体層12を絶縁層13で挟んで構成されている。第1半導体層11上には絶縁膜14を介してフィールドプレート抵抗膜20が形成されている。可変電流源ISが、ゲート電極19からドレイン電極17にかけて絶縁膜14上に沿って形成されたフィールドプレート抵抗膜20(フィールドプレート抵抗R1およびR2)に生じるノードN1の電圧に応じて出力電流値を変更してセンス抵抗Rsの検出電圧V2を補正する。

(もっと読む)

半導体装置

【課題】内部回路の動作時における電源ノイズの影響を抑え、少ピン化および小面積化を実現する半導体装置を提供することである。

【解決手段】第1の内部回路102に対する電源線PL1と第2の内部回路104に対する電源線PL2とは共通のピン端子30aに接続され、第1の内部回路102に対する接地線SL1と第2の内部回路104に対する接地線SL2とは共通のピン端子30bに接続される。第1の内部回路102の動作時に電源線PL1上に発生した電源ノイズは、電源線PL1に介挿され、ゲートが接地線SL1に接続されたPチャネルMOSトランジスタP1および電源線PL1および接地線SL1の間に設けられたキャパシタC1により吸収される。接地線SL1上に発生した電源ノイズは、接地線SL1に介挿され、ゲートが電源線PL1に接続されたNチャネルMOSトランジスタN1およびキャパシタC1により吸収される。

(もっと読む)

半導体装置およびそれを用いた無線通信機器

【課題】半導体装置の熱抵抗を低減すること、および小型化できる技術を提供する。

【解決手段】複数の単位トランジスタQを有する半導体装置であって、半導体装置は、単位トランジスタQを第1の個数(7個)有するトランジスタ形成領域3a、3b、3e、3fと、単位トランジスタQを第2の個数(4個)有するトランジスタ形成領域3c、3dとを有し、トランジスタ形成領域3c、3dは、トランジスタ形成領域3a、3b、3e、3fの間に配置され、第1の個数は、第2の個数よりも多い。そして、単位トランジスタは、コレクタ層と、ベース層と、エミッタ層とを備えており、エミッタ層上には、エミッタ層と電気的に接続されたエミッタメサ層が形成され、このエミッタメサ層上に、エミッタ層と電気的に接続されたバラスト抵抗層が形成されている。

(もっと読む)

高電圧動作電界効果トランジスタとそのバイアス回路およびその高電圧動作回路要素

【課題】 ICまたはLSIの標準電源電圧用のトランジスタ構成部分ないしはプロセス技術を活用して高電圧動作電界効果トランジスタを該IC中に作りこむ。

【解決手段】 電界効果トランジスタの動作電圧を大きくするために、ゲートにドレイン電位に応じて変化する電位分布を設ける手段をとる。

(もっと読む)

マルチゲート半導体デバイス

【課題】バランス抵抗器の接続されたゲート間伝導領域を有するマルチゲート半導体デバイスにおいて、スイッチ素子として使用した際の低挿入損失と素子サイズを抑えつつ、オフ時の非線形性を改善する。

【解決手段】バランス抵抗器405のゲート間伝導領域への接続点をゲートの2つの両端より内側に設ける。好ましくはメアンダ状ゲートの屈曲領域4061に設ける。

(もっと読む)

静電気保護素子及びその製造方法

【課題】リーク電流の少ない静電気保護素子を提供する。

【解決手段】半導体基板100nと、半導体基板内に形成され、第1の導電型の不純物が拡散された第1のウェル101と、第1のウェル内に、第1のウェルの一部の領域を挟んで形成され、第2の導電型の不純物が拡散されたコレクタ領域110及びエミッタ領域112と、第1のウェル内に、前記エミッタ領域と分離する第1の分離領域102を挟んで形成され、第1のウェル内に拡散された不純物の濃度よりも高い濃度の、第1の導電型の不純物が拡散されたベース拡散領域114と、前記エミッタ領域下方から前記エミッタ領域と前記ベース拡散領域との間までの第1のウェル内の領域に形成され、第2の導電型の不純物が拡散された拡散領域103aとを備えた静電気保護素子。

(もっと読む)

半導体装置

【課題】 占有面積の増加を少なく、十分なESD保護機能を持たせたESD保護用のN型のMOSトランジスタを有する半導体装置を提供する。

【解決手段】 ESD保護用のN型MOSトランジスタのドレイン領域は、トレンチ分離領域の側面および下面に設置されたドレイン領域と同一の導電型の不純物拡散領域によって形成されたドレイン延設領域を介して、ドレイン領域と同一の導電型の不純物拡散領域によって形成されたドレインコンタクト領域と電気的に接続している半導体装置とした。

(もっと読む)

半導体装置

【課題】低電圧時の電流が適度に大きく、高電圧時の電流が小さい半導体装置を提供する。

【解決手段】半導体装置100は、整流素子D1と、抵抗R1と、nチャネルディプリーショントランジスタDTと、アノード電極パッド7bとが直列接続された構成を有する半導体装置100であって、nチャネルディプリーショントランジスタDTのゲート電位を抵抗R1の両端の電位差により生成し、かつゲート電位によってnチャネルディプリーショントランジスタDTのチャネル91に空乏層Dを生じさせるよう構成されている。

(もっと読む)

半導体集積回路

【課題】同一ウェル領域にしきい値の異なる絶縁ゲート電界効果トランジスタが形成された半導体集積回路を提供する。

【解決手段】第1抵抗を有する第1領域14a、14b、14cと第1抵抗より高い第2抵抗を有する第2領域15a、15bとが連接してなる第2導電型のウェル領域13と、第1領域14b、14cに形成された絶縁ゲート電界効果トランジスタ16、17と、を具備する。ウェル領域13の一端からウェル領域13の他端に通電し、電圧降下によりウェル領域13内に電圧分布を生じさせる。

(もっと読む)

薄膜集積回路装置及びその製造方法

【課題】商品の意匠性を低下させないICタグ等を形成することができる薄膜集積回路装置を提供する。

【解決手段】透明基板1上に少なくともTFT素子Aと容量素子B及び/又は抵抗素子Cとを有し、TFT素子Aを構成するゲート電極2A、ゲート絶縁膜3A、半導体膜4、ソース電極6S及びドレイン電極6Dがいずれも透明膜であり、容量素子Cを構成する誘電体膜3Bが前記ゲート絶縁膜3Aと同一材料であり、その誘電体膜3Bを積層方向Zに挟む一方の第1電極2Bが前記ゲート電極2Aと同一材料で、他方の第2電極6Bが前記ソース電極6S及びドレイン電極6Dと同一材料であり、抵抗素子Cを構成する抵抗体膜4Cが前記半導体膜4と同一材料であり、その抵抗体膜4Cを面内方向Xに挟む第3電極6Eと第4電極6Fが前記ソース電極6S及びドレイン電極6Fと同一材料であるようにした薄膜集積回路装置10Aを提供する。

(もっと読む)

ESD保護素子

【課題】ESD耐量を向上させたESD保護素子を提供する。

【解決手段】本発明によるESD保護素子は、バイポーラトランジスタを用いたESD保護素子である。バイポーラトランジスタは、第1端子(Pad)に接続されるコレクタ拡散層7とエミッタ端子とを備えるバイポーラトランジスタと、第2端子(GND)からエミッタ拡散層4を介してコレクタ拡散層7に至る複数の電流経路上のそれぞれに設けられた電流制御抵抗11とを具備する。

(もっと読む)

半導体装置

【課題】環流ダイオードの逆回復動作時に発生する電流及び電圧の振動現象の収束時間を短縮する。

【解決手段】半導体装置1は、還流ダイオードDと、還流ダイオードDに対し並列に接続され、且つ、キャパシタCと抵抗Rを有する半導体スナバ2を備え、環流ダイオードDの遮断状態における静電容量に対するキャパシタCの静電容量の比が0.1以上になっている。このような構成によれば、振動現象の収束効果が高くなるように半導体スナバ2を構成するキャパシタCの静電容量が設定されているので、環流ダイオードDの逆回復動作時に発生する電流及び電圧の振動現象の収束時間を短縮することができる。

(もっと読む)

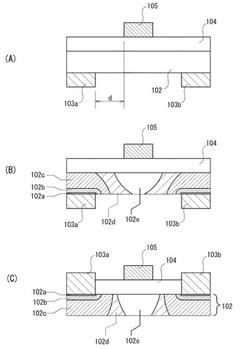

半導体装置及びその製造方法

【課題】メタルゲート電極を有するMIS型トランジスタと高抵抗素子とを容易に集積化でき、製造工程数の増加と歩留まりの低下を抑制できる半導体装置及びその製造方法を提供する。

【解決手段】基板100の素子領域にシリコン膜118と金属膜103の積層構造からなるMIS型トランジスタのゲート電極、及び素子分離領域上に前記シリコン膜と前記金属膜の積層構造からなる高抵抗素子を形成する。そして、前記ゲート電極の側壁に耐酸化性の絶縁膜110を形成し、前記高抵抗素子の前記金属膜103を酸化する。

(もっと読む)

静電気放電保護素子及びその製造方法

【課題】ESD保護素子の動作特性を向上させ、かつ、ESD保護素子の大きさを減少させて半導体チップの大きさを縮小可能なESD保護素子及びその製造方法を提供すること。

【解決手段】基板上に形成されたゲート電極と、前記ゲート電極の両側に露出する前記基板内に互いに同じ導電型で形成された第1ドーピング領域及び第2ドーピング領域と、前記第2ドーピング領域内に前記第2ドーピング領域とは逆導電型で形成された第3ドーピング領域と、前記ゲート電極から離隔し、前記ゲート電極の両側に露出する前記基板内に前記第1ドーピング領域及び第2ドーピング領域と同じ導電型で形成された第4ドーピング領域及び第5ドーピング領域と、を備える静電気放電保護素子を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】適切な抵抗素子を得ることが可能な半導体装置を提供する。

【解決手段】素子領域11及び素子分離領域12を含む基板10と、素子領域上に形成されたゲート絶縁膜21と、ゲート絶縁膜上に形成された金属膜22及び金属膜上に形成された第1の半導体膜23を有するゲート電極とを含むトランジスタ部と、基板の上方に形成され且つ第1の半導体膜と同一の材料で形成された第2の半導体膜23と、基板と第2の半導体膜との間に形成された空洞25とを含む抵抗素子部とを備える。

(もっと読む)

トランジスタ型保護素子および半導体集積回路

【課題】保護素子のターンオン電圧を決める制約を少なくする。

【解決手段】半導体基板1、Pウェル2、ゲート電極4、ソース領域5、第1ドレイン領域6、第2ドレイン領域8および抵抗性接続領域9を有する。第1および第2ドレイン領域6,8は、ゲート電極4直下のウェル部分と所定の距離だけ離れたN型半導体領域からなる。第1および第2ドレイン領域6,8も互いに離れており、その間が抵抗性接続領域9によって接続されている。抵抗性接続領域9は薄膜抵抗層によって代替できる。

(もっと読む)

保護回路を備えた半導体装置

【課題】 サージの印加時に全てのMOSがオンし易い保護回路を備えた半導体装置を提供する。

【解決手段】 サージから内部回路を保護する保護回路を備えた半導体装置であって、ウェル領域を備えている。ウェル領域内には、一方向に沿って配列されている複数のMOS構造と、第1配線に接続されているウェルタップ領域が形成されている。各MOS構造は、第1配線に接続されているソース領域と、第2配線に接続されているドレイン領域と、ソース領域とドレイン領域の間のウェル領域に絶縁膜を介して対向しているゲート電極を備えている。ウェルタップ領域は、複数のMOS構造の配列を延長した範囲内に形成されている。ウェル領域の第1導電型不純物濃度が、前記一方向に沿って見たときに、前記延長した範囲内のウェルタップ領域に近い位置よりもそのウェルタップ領域から遠い位置で高くなっている。

(もっと読む)

サンプルホールド回路、ドライバ、電気光学装置、及び電子機器

【課題】演算増幅器の電源ラインの電位を安定化させる。

【解決手段】サンプルホールド回路は、演算増幅器OP1と、演算増幅器の出力端子と第1の入力端子のノードであるサミングノードNEGとの間に設けられた帰還用スイッチ素子SFと、帰還用スイッチ素子のオン・オフを制御するスイッチ信号生成回路80を含む。スイッチ信号生成回路を構成するN型トランジスタは第1のP型ウェルPW1に、スイッチ信号生成回路を構成するP型トランジスタは第1のN型ウェルNW1に、第1のP型ウェル及び第1のN型ウェルは第1のディープN型ウェルDNW1にそれぞれ形成される。演算増幅器のN型トランジスタは第2のP型ウェルPW2に、演算増幅器のP型トランジスタは第2のN型ウェルNW2に、第2のP型ウェル及び第2のN型ウェルは、第1のディープN型ウェルと分離された第2のディープN型ウェルDNW2にそれぞれ形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極のチャージアップによるMOSFETの閾値電圧Vtシフトの防止を図ることである。

【解決手段】キャパシタ下部電極3をゲート電極6aと結線し、またキャパシタ上部電極6bをP型接地層12と結線する事により、ゲート電極6aとゲート絶縁膜4から成るゲートに並列にキャパシタを形成する。この場合、キャパシタ絶縁膜5をゲート絶縁膜4に比べ薄く形成する事によりゲート電極6a上にチャージアップした電荷を、キャパシタを経由してP型接地層12に放電させる。

(もっと読む)

1 - 20 / 51

[ Back to top ]