Fターム[5F038AZ06]の内容

Fターム[5F038AZ06]に分類される特許

1 - 20 / 138

半導体装置

【課題】異なる配線を介して異なる電源端子から内部回路を構成する第1の回路および第2の回路にそれぞれ給電する際に、第1の回路に給電する配線と第2の回路に給電する配線との間に発生するノイズを抑制する。

【解決手段】半導体装置は、第1の回路に給電を行う第1の電源配線と、第2の回路に給電を行う第2の電源配線と、第1の電源配線と第2の電源配線との間に容量素子を設けることにより、両端子間のインピーダンスを、大幅に低減させることにより異種電源間のノイズを低減する。

(もっと読む)

ネスト化複合ダイオード

【課題】高いスイッチング速度を有し、電圧降伏耐性を強化したネスト化複合ダイオードを提供する。

【解決手段】ネスト化複合ダイオードの種々の実現を、本明細書に開示する。1つの実現では、ネスト化複合ダイオードが、複合ダイオードに結合されたプライマリ・トランジスタを含む。複合ダイオードは、中間型トランジスタとカスコード接続された低電圧(LV)ダイオードを含み、中間型トランジスタは、LVダイオードよりは大きく、プライマリ・トランジスタよりは小さい降伏電圧を有する。1つの実現では、プライマリ・トランジスタはIII-V族トランジスタとすることができ、LVダイオードはIV族LVダイオードとすることができる。

(もっと読む)

半導体電力増幅器

【課題】ビアホールの数を少なくしてもループ発振などの特性劣化が生じにくい半導体電力増幅器を提供する。

【解決手段】半導体電力増幅器は、ゲート電極Gと、ドレイン電極Dと、前記ゲートフィンガー電極に対向して配置されるソースフィンガー電極横手方向の両サイドに引き出される2つのソース電極Sと、を有するユニットFETと、前記ユニットFETが、前記ソース電極間を結ぶ略直線方向に複数個並列配置され、隣り合うユニットFET間に存在する2つのソース電極の両方を共通して高周波グランド面と接続する第1の接地インダクタンス値を有する第1のビアホール18Kと、隣り合うユニットFETが存在しない側のソース電極上に配置され、接地インダクタンスを等しくするために前記高周波グランド面に接続する第2の接地インダクタンス値を有する第2のビアホール18Dと、を有する。

(もっと読む)

容量素子および半導体装置

【課題】容量素子のQ値(Quality Factor)特性を向上する。

【解決手段】容量素子は、互いに対向する一対の電極EL10、EL20と、一対の電極の一方の電極に設けられ、一方の電極の両端部から間隔を置いて配置された第1端子部とTE10、一対の電極の他方の電極に設けられ、他方の電極の両端部から間隔を置いて配置された第2端子部とTE20を有している。

(もっと読む)

半導体装置及びDC−DCコンバータ

【課題】耐久性が高い半導体装置及びDC−DCコンバータを提供する。

【解決手段】実施形態に係る半導体装置は、高電位側電源電位に接続するための第1の配線と、前記高電位側電源電位に接続するための、前記第1の配線とは別の第2の配線と、前記第1の配線に一端が接続され、他端が出力端子に接続されるスイッチングトランジスタと、前記高電位側電源電位と前記低電位側電源電位との間で前記スイッチングトランジスタと並列に接続される保護素子とを備える。前記保護素子は、前記第1の配線に接続される、第1のp形半導体領域と、前記第2の配線に接続される、前記第1のp形半導体領域に接したn形半導体領域と、前記n形半導体領域に接し、前記第1のp形半導体領域から離隔し、前記低電位側電源電位に接続するための配線に接続される第2のp形半導体領域と、を有する。

(もっと読む)

半導体装置及びそのテスト方法

【課題】従来の半導体装置では、電源電圧変動を抑制するために回路規模が大きくなる問題があった。

【解決手段】本発明の半導体装置は、テスト対象回路11〜13と、スキャンモード制御信号SMCと、ノイズ制御信号CNTと、クロック信号CLKと、テストパターンSINとが入力され、テスト対象回路12に対するテストを行うテスト回路20と、を有し、テスト回路20は、ノイズ制御信号CNTがイネーブルであるダミーノイズ生成期間にテスト回路20において保持されているテストパターンSINに基づくテスト値を維持し、ダミーノイズ生成期間にクロック信号CLKの周期に応じて変動するダミー電源ノイズを生成し、ダミーノイズ生成期間の終了後にテストパターンによりテスト対象回路12をテストする。

(もっと読む)

半導体パッケージ

【課題】ボンド・ワイヤの寄生インダクタンスを小さくし、高周波特性を良好とすることができる半導体パッケージを提供する。

【解決手段】高周波信号が入力される入力整合回路を有しダイボンド領域に配された半導体集積回路チップと、前記ダイボンド領域の周辺に配されたリード端子と、を備え、前記半導体集積回路チップが有する各端子と前記各リード端子とがボンド・ワイヤにより接続された半導体パッケージにおいて、前記ダイボンド領域の中央部より前記入力整合回路に高周波信号を入力させるための前記リード端子である高周波入力端子側および/または前記入力整合回路のグランド接続用の前記リード端子であるグランド端子側にシフトした位置に前記半導体集積回路チップは配される構成とする。

(もっと読む)

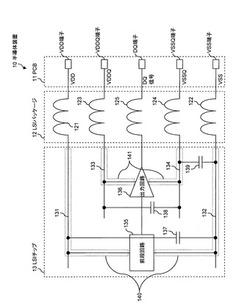

半導体パッケージ

【課題】ボンディングワイヤのループインダクタンスを低減した半導体パッケージを提供する。

【解決手段】所定の方向に交互に配置された信号用パッドおよび補助パッドのそれぞれが複数設けられた半導体装置と、信号用ボンドフィンガー、電源電圧用ボンドフィンガーおよび接地電位用ボンドフィンガーのそれぞれが複数設けられたパッケージ基板と、を有する。複数の信号用パッドのそれぞれが複数の信号用ボンドフィンガーのそれぞれと第1のワイヤを介して接続され、複数の電源電圧用ボンドフィンガーおよび複数の接地電位用ボンドフィンガーのそれぞれが複数の補助パッドのそれぞれと第2のワイヤを介して接続されている。第1のワイヤが、電源電圧用ボンドフィンガーに接続された第2のワイヤと接地電位用ボンドフィンガーに接続された第2のワイヤとの間に配置されている。

(もっと読む)

半導体装置

【課題】内部回路の動作時における電源ノイズの影響を抑え、少ピン化および小面積化を実現する半導体装置を提供することである。

【解決手段】第1の内部回路102に対する電源線PL1と第2の内部回路104に対する電源線PL2とは共通のピン端子30aに接続され、第1の内部回路102に対する接地線SL1と第2の内部回路104に対する接地線SL2とは共通のピン端子30bに接続される。第1の内部回路102の動作時に電源線PL1上に発生した電源ノイズは、電源線PL1に介挿され、ゲートが接地線SL1に接続されたPチャネルMOSトランジスタP1および電源線PL1および接地線SL1の間に設けられたキャパシタC1により吸収される。接地線SL1上に発生した電源ノイズは、接地線SL1に介挿され、ゲートが電源線PL1に接続されたNチャネルMOSトランジスタN1およびキャパシタC1により吸収される。

(もっと読む)

半導体集積回路装置

【課題】入力回路ブロックの入力配線と出力回路ブロックの出力配線を短くする。

【解決手段】半導体集積回路装置30において、入力回路ブロック32用の外部接続用電極P2及びP3は、入力回路ブロック32と出力回路ブロック33との間に複数配置されており、出力回路ブロック33用の外部接続用電極P1及びP4は、出力回路ブロック33とリード電極34及び35との間に複数配置されており、金属細線Wb1及びWb2を介して外部接続用電極P1及びP2に接続されるリード電極34と、金属細線Wb3及びWb4を介して外部接続用電極P3及びP4に接続されるリード電極35は、いずれも、入力回路ブロック32、外部接続用電極P2及びP3、出力回路ブロック33、外部接続用電極P1及びP4、リード電極34及び35の順に配置された方向と平行する方向に複数配置されている。

(もっと読む)

半導体集積回路のノイズ耐性評価方法およびノイズ耐性評価装置

【課題】大規模な半導体集積回路であってもノイズ耐性評価が短時間で可能なノイズ耐性評価方法を提供する。

【解決手段】回路ネットリストを作成する第1のステップS11と、能動素子を受動素子回路に置き換えて置換回路ネットリストを作成する第2のステップS12と、トランジスタの制御端子に該当する制御ノードを抽出する第3のステップS13と、ノイズ注入ノードを設定する第4のステップS14と、所定周波数のノイズを設定し、互いに異なる制御ノードとノイズ注入ノード間の経路のインピーダンスを計算する第5のステップS15と、制御ノード、ノイズ注入ノードおよび経路の各組み合わせにおけるインピーダンスのリストを作成する第6のステップS16と、インピーダンスの最小値から半導体集積回路のノイズ耐性を判定する第7のステップS17とを有してなるノイズ耐性評価方法100とする。

(もっと読む)

半導体装置

【課題】超高周波帯におけるシリコン基板による損失を低減すると共に、貫通配線のインダクタンス成分の影響を小さくした半導体装置を実現できるようにする。

【解決手段】半導体装置は、回路素子105が形成された半導体基板100と、半導体基板100の主面の上に形成された第1の誘電体層121と、第1の誘電体層121の上に形成された第2の誘電体層131と、第1の誘電体層121を貫通し、回路素子105と接続された第1の貫通配線122と、第2の誘電体層131を貫通し、第1の貫通配線122と接続された第2の貫通配線132とを備えている。第2の貫通配線132は、第1の貫通配線132よりもインダクタンスが小さい。

(もっと読む)

半導体装置

【課題】信号線の上面に微小な凹凸が形成されても、伝送線路の伝送特性が劣化することを抑制できるようにする。

【解決手段】信号線522は、多層配線層400及び再配線層500の第a層(a≧2)に形成されている。プレーン配線444は多層配線層400及び再配線層500の第b層(b<a)に形成されており、平面視で信号線522と重なっている。2つのコプレーナ配線524は多層配線層400及び再配線層500の第c層(b≦c≦a)に形成されており、平面視で信号線522と平行に延伸しており、かつ信号線522を挟んでいる。信号線522からプレーン配線444までの距離hは、信号線522からコプレーナ配線524までの距離wより短い。信号線522の上方のうち、信号線522からwと同じ高さの範囲内には、電源線、グランド線、及び他の信号線が位置していない。

(もっと読む)

半導体装置

【課題】コモンノイズを低減する。

【解決手段】半導体装置10は、直列に接続された半導体スイッチング素子11,12と、正極端子13と、負極端子14と、出力端子15とを具備する半導体モジュール16と、半導体モジュール16に絶縁されたボディ17とを備える。ボディ17と各端子13,14との間の各浮遊容量C1,C3に対して、出力端子15とボディ17との間で、出力端子15の浮遊容量C2と浮遊容量C1とが直列接続または出力端子15の浮遊容量C2と浮遊容量C3とが直列接続になるようにして、各端子13,14,15が配置されている。

(もっと読む)

半導体装置

【課題】VCOに含まれるスパイラルインダクタとMOSバラクタを接続する配線に付加される寄生インダクタ、および/または寄生容量を低減することができる半導体装置を提供する。

【解決手段】LCタンクVCOは、第1および第2のスパイラルインダクタL1,L2と、第1および第2のMOSバラクタC1,C2とを備える。第1および第2のMOSバラクタC1,C2は、半導体基板に垂直な方向から見たときに、第1のスパイラルインダクタL1と第2のスパイラルインダクタL2の間の領域に配置される。

(もっと読む)

高周波回路チップとこのチップを有する高周波回路装置並びにその製造方法

【課題】MMICの特性測定において,DCバイアス印加時の発振を抑制する。

【解決手段】この発明に係る高周波回路チップのMMIC60は、GaAs基板12上に所定の間隔をおいて並行して配設されたDCバイアス線路62が、その端部に互いに間隔をおいて隣接したDCパッド64を備えたもので、DCバイアス線路62の端部のDCパッド64に個別にDCバイアスを印加することができ、高周波信号の影響を少ない状態でチップの電気的特性を測定することができる。

(もっと読む)

半導体集積回路及びそれを備えたコンデンサマイクロフォン

【課題】高RF妨害波耐性の半導体集積回路及びそれを備えたコンデンサマイクロフォンを提供すること。

【解決手段】本発明にかかる半導体集積回路は、端子Bと端子Cとの間に設けられた出力トランジスタMN1と、端子Bと端子Cとの間に設けられたローパスフィルタ100と、出力トランジスタMN1のゲートと端子Cとの間に設けられたプルダウン用抵抗R3と、プルダウン用抵抗R3と端子Cとの間に設けられたインダクタL1と、を備える。

(もっと読む)

半導体集積回路

【課題】半導体集積回路のチップ面積とコストの増加や、電気的特性の問題を招くことなく、出力バッファ回路の出力電圧のリンギングを抑制する。

【解決手段】半導体集積回路200は、電源線10、電源抵抗11、接地線12、接地抵抗13、出力バッファ回路14,15,16、電源端子PVdd、接地端子PVss、出力端子PO1,PO2,PO3、及びリード端子17,18を含んで構成される。電源抵抗11は、電源線10と出力バッファ回路14の電源電位入力端との接続点N1と電源端子PVddとの間に接続されている。接地抵抗13は、接地線12と出力バッファ回路14の接地電位入力端との接続点N4と接地端子PVssとの間に接続されている。

(もっと読む)

DC/DCコンバータ用半導体装置

【課題】半導体装置の電源電圧の変換効率を向上させる。

【解決手段】ハイサイドスイッチ用のパワーMOS・FETとローサイドスイッチ用のパワーMOS・FETとが直列に接続された回路を有する非絶縁型DC−DCコンバータにおいて、ローサイドスイッチ用のパワーMOS・FETと、そのローサイドスイッチ用のパワーMOS・FETに並列に接続されるショットキーバリアダイオードD1とを同一の半導体チップ5b内に形成した。ショットキーバリアダイオードD1の形成領域SDRを半導体チップ5bの短方向の中央に配置し、その両側にローサイドのパワーMOS・FETの形成領域を配置した。また、半導体チップ5bの主面の両長辺近傍のゲートフィンガ6aから中央のショットキーバリアダイオードD1の形成領域SDRに向かって、その形成領域SDRを挟み込むように複数本のゲートフィンガ6bを延在配置した。

(もっと読む)

半導体装置

【課題】V−G間SSOノイズだけでなく、S−G間SSOノイズも低減することができる半導体装置10を提供する。

【解決手段】本発明の半導体装置10は、出力回路12毎に受信回路15の入力容量34と所定の関係を有する容量の近傍オンチップバイパスキャパシタ23を、所定の配線抵抗となるように設け、それぞれの出力回路12について容量および配線抵抗が所定の関係となる遠方オンチップバイパスキャパシタ24を、複数の出力回路12に共通に設ける。

(もっと読む)

1 - 20 / 138

[ Back to top ]