Fターム[5F038CD20]の内容

Fターム[5F038CD20]に分類される特許

1 - 20 / 51

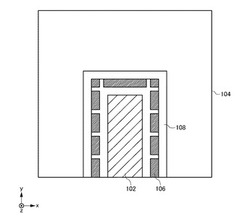

半導体装置および半導体装置設計方法

【課題】半導体基板においてダミーパターンの配置密度を高める。

【解決手段】半導体基板104には、配線パターン102とダミーパターン106がレイアウトされる。配線パターン102の周囲にはマージン領域がレイアウトされ、マージン領域の周囲にダミー領域がレイアウトされる。このダミー領域に、複数のダミーパターン106がレイアウトされる。ダミーパターン106は、ダミー領域の延伸方向に配列される。マージン領域とダミー領域は、配線パターン102を基準として交互にレイアウトされる。

(もっと読む)

DC/DCコンバータ用半導体装置

【課題】半導体装置の電源電圧の変換効率を向上させる。

【解決手段】ハイサイドスイッチ用のパワーMOS・FETとローサイドスイッチ用のパワーMOS・FETとが直列に接続された回路を有する非絶縁型DC−DCコンバータにおいて、ローサイドスイッチ用のパワーMOS・FETと、そのローサイドスイッチ用のパワーMOS・FETに並列に接続されるショットキーバリアダイオードD1とを同一の半導体チップ5b内に形成した。ショットキーバリアダイオードD1の形成領域SDRを半導体チップ5bの短方向の中央に配置し、その両側にローサイドのパワーMOS・FETの形成領域を配置した。また、半導体チップ5bの主面の両長辺近傍のゲートフィンガ6aから中央のショットキーバリアダイオードD1の形成領域SDRに向かって、その形成領域SDRを挟み込むように複数本のゲートフィンガ6bを延在配置した。

(もっと読む)

化合物半導体装置

【課題】抵抗層で発生する熱が基板の側に伝導しやすい状態で、基板との界面への導電層の形成が抑制できるようにする。

【解決手段】InPからなる基板101と、基板101の上に形成された窒化シリコン層102と、窒化シリコン層102の上に形成された酸化シリコン層103と、WSiNから構成されて酸化シリコン層103の上に形成された抵抗層104と、酸化シリコン層103の上に形成されて抵抗層104に接続された配線105および配線106とを少なくとも備える。

(もっと読む)

半導体回路装置

【課題】配線が微細化された半導体回路装置でも、銅(Cu)からなる配線間ブリッジ等による配線ショートの発生を予防することを目的とする。

【解決手段】隣接する配線との最小スペース幅13によって、設けられる配線幅12の最大値を規定することにより、配線が微細化された半導体回路装置でも、銅(Cu)からなる配線間ブリッジ等による配線ショートの発生を予防することができる。

(もっと読む)

ナノワイヤの製造方法及び集積回路

【課題】低温プロセスのナノワイヤの製造を実現する。

【解決手段】封入されたナノワイヤを製造する方法であって、表面層を有する基板を提供することと、前記表面層にパターンを付け、ナノメートルサイズのフィーチャを形成することと、前記ナノメートルサイズのフィーチャ内に導電材料を配置し、前記基板上にナノワイヤを形成することと、前記表面層を除去することと、前記ナノワイヤ上に絶縁材料を配置することと、を含み、前記ナノワイヤ上に前記絶縁材料を配置することは、約350℃未満の温度で前記ナノワイヤ上に絶縁材料を配置することを含む。

(もっと読む)

パッシベーション層のクラックの発生を防止した集積回路の製造方法

【課題】パッシベーション層のクラックの発生を防止する。

【解決手段】エッチング及びダマシン法を用いて製造される集積回路においては、金属配線層から周囲の誘電体材料に応力が伝達されることによって、デバイスに組み込まれる配線層(400)の周囲の誘電体材料にクラックが発生することが一般的である。本発明は、周囲の誘電体層に伝達される応力を低減することができると考えられる丸められたコーナを有する配線層を形成することにより、この問題を解決する。

(もっと読む)

半導体装置

【課題】MEMS構造体に対して外部空間からの圧力や振動信号を直接受信できるように構成し、かつ、MEMS構造体と集積回路とを形成した半導体チップをバンプ電極でモジュール基板にフェイスダウン実装することにより、小型化を実現できる技術を提供する。

【解決手段】半導体基板1の一方の面に集積回路が形成され、半導体基板1の他方の面にMEMS構造体が形成されている。そして、集積回路上に形成されているバンプ電極BPによって実装基板にフリップチップ接続する構造となっている。このとき、トランスデューサは外部空間に向いた状態で配置できる。このため、トランスデューサが外部空間と直接対話する機能を損なうことなく、半導体装置を小型化することができる。なお、集積回路とMEMS構造体とは半導体基板1を貫通する貫通電極20a、20bにより電気的に接続される。

(もっと読む)

半導体装置

【課題】配線に係る抵抗を低減することができるため、半導体セルの面積を縮小することができる。

【解決手段】本発明に係る半導体装置は、半導体基板1と、半導体基板1表面に形成されたコンタクト領域4と、半導体基板1上に形成された層間絶縁膜21とを備える。層間絶縁膜21には、コンタクト領域4まで達する線状に延設された開口溝が設けられる。そして、開口溝内に埋設され、コンタクト領域4と電気接続された導電層8をさらに備える。

(もっと読む)

半導体集積回路装置の製造方法

【課題】 製造プロセスへの付加を抑えコスト・TATを増大させることなくタイミング最適化が可能となる半導体集積回路装置の製造方法を提供することを目的とする。

【解決手段】 タイミング制約違反の有無を判定し、タイミング制約違反が検出された場合にこれを解消する為に信号やクロックの更なる遅延が必要な最適化対象配線333とこれに所定間隔以下で近接する隣接配線361の間(隣接配線間)の一部又は全部にボイド形成抑止領域381を設定し、ボイド形成抑止領域内の最適化対象配線と隣接配線の間(隣接配線間)に絶縁膜を形成し、ボイド形成抑止領域外の最適化対象配線と隣接配線の間(隣接配線間)にボイド371a,bを形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】容量素子の歩留まりおよび信頼性の低下を抑制する。

【解決手段】半導体装置100は、半導体基板の上部に設けられ、SiO2膜103およびSiO2膜103中に埋設された第一銅配線105を含む第一配線層、第一配線層上に設けられたSiO2膜109、SiO2膜109上に設けられたSiO2膜111、SiO2膜111上に設けられた容量素子121を含む。容量素子121は、SiO2膜111上に設けられた下部電極115、下部電極115の上部に対向して設けられた上部電極119およびこれらの間に設けられた容量絶縁膜117から構成されている。第一銅配線105の上面に突起部135が設けられている。SiO2膜111の上面は平坦である。

(もっと読む)

半導体装置およびその製造方法

【課題】バッティング・ディフュージョン構造を有する半導体素子を備えた半導体装置の製造歩留まりを向上させる。

【解決手段】半導体基板1の主面に、素子分離領域2で囲まれたpMIS用の活性領域3aと、Vdd電位給電部用の活性領域3bと、pMIS結合用の活性領域3cとの3つの活性領域が規定されており、2入力NANDゲートCMOS論理回路で2つのpMIS(Qp)に共有されるソース用のp+型半導体領域7bとVdd電位給電部用のn+型半導体領域6bとの境界部8が、pMIS結合用の活性領域3cには設けられておらず、pMIS用の活性領域3a内に設けられている。これにより、境界部8の全てに沿ったpMIS(Qp)のソース用のp+型半導体領域7bおよびVdd電位給電部用のn+型半導体領域6bの表面に形成されたシリサイド層の断線がなくなる。

(もっと読む)

半導体集積回路装置

【課題】 この発明は、半導体基板またはメタル配線層を介して伝播するノイズを遮蔽・低減することができる半導体集積回路装置を提供する。

【解決手段】 この発明は、半導体基板10上に形成される複数の半導体素子29で形成される回路部11と、複数のメタル配線層100と、半導体基板100に形成される拡散層21,22を備える半導体集積回路装置において、半導体基板10に回路部11を取り囲むように形成される拡散層からなる拡散層ガードリング30と、拡散層ガードリング30上に設けられる複数のメタル配線層100間並びに拡散層30間とを接続するビア41を備える第1のメタルガードリング31と、前記回路部上に蓋をするように配置されたメタル配線からなる第2のメタルガードリング32と、により、回路部11を立体的に囲うガードリング部34を構成する。

(もっと読む)

半導体装置

【課題】二つの素子領域間に介在するシールリングを通じたノイズ伝搬を抑制する。

【解決手段】半導体装置100は、ロジック部およびアナログ部を有する。半導体装置100は、シリコン基板101、層間絶縁膜173、層間絶縁膜173中に埋設された導電膜により構成されロジック部151の外周を取り囲むシールリング105、およびシリコン基板101に設けられたウェルにより構成されるとともにロジック部からシールリング105を経由してアナログ部に至る経路の導通を遮断するNウェルガードリング161を有する。Nウェルガードリング161は、シールリング領域106とロジック部またはアナログ部との間に配置される。

(もっと読む)

LSI品種決定方法、LSI設計支援方法、LSI品種決定プログラム、LSI設計支援プログラム、記録媒体、LSI品種決定装置およびLSI設計支援装置

【課題】LSIの製造途中において、中間製造物のトランジスタ性能を推定することにより、各中間製造物に合った適切な品種を決定し、LSI製造における歩留まりを向上させる。

【解決手段】ストラクチャードASIC製造時において、トランジスタ層またはトランジスタ層およびメタル1層が形成された中間製造物を製造後、当該中間製造物ごとのトランジスタ速度を測定し、この測定結果とトランジスタ速度に関連付けられた統計データとを用いて、トランジスタ速度の最大遅延推定値を算出する。そして、この算出結果に基づいて、LSIの品種リストの中から、ストラクチャードASICの品種を決定する。

(もっと読む)

半導体装置の製造方法

【課題】通常の半導体装置の製造装置のみで、小型、薄型の半導体装置、特にGaAs等の化合物半導体装置に適用することができる半導体装置の製造方法を提供する。

【解決手段】半導体基板の主面に回路素子を形成した後、電極形成予定領域に複数の凹部3を形成する。回路素子の電極と接続し、凹部の内壁を被覆する金属膜4を形成し、凹部内を電極金属6で充填する。その後、表面を樹脂層7で被覆する。半導体基板の裏面をエッチングし、金属膜4を露出させる。ダイシングラインに沿い、凹部内に充填した電極金属6の一部を凹部の側壁部に残して切断し、個々の半導体装置に個片化する。

(もっと読む)

半導体装置及びその製造方法

【課題】少ない枚数のレチクルセットで、シングルコアデバイスとマルチコアデバイスの両方のデバイスを製造できる、新規な耐湿リングレイアウトを提案する。

【解決手段】同一回路構成を有するチップを複数含む半導体デバイスにおいて、複数チップを個々に囲うように形成された複数の第一耐湿リングと、複数チップの全体を囲うように形成された第二耐湿リングとを有する。

(もっと読む)

半導体集積回路および製造方法

【課題】X線分析などを利用したリバースエンジニアリングに対して防御機能を有する半導体集積回路を提供する。

【解決手段】半導体集積回路100は、複数の回路素子を接続する実配線パターンが形成されている配線層101,102と、配線層101,102の上部の層に、実配線パターンに重なるように配置され、複数の回路素子と実配線パターンとのいずれにも接続されない擬似配線パターンとして形成されている第1の擬似配線パターン群113と、第1の擬似配線パターン群113の上部の層に、第1の擬似配線パターン群113に重なるように配置され、複数の回路素子と実配線パターンとのいずれにも接続されない擬似配線パターンとして形成されている第2の擬似配線パターン群114とを備え、第1の擬似配線パターン群113における擬似配線パターンの間隔と第2の擬似配線パターン群114における擬似配線パターンの間隔との差がX線の波長程度である。

(もっと読む)

半導体装置および電気ヒューズの切断方法

【課題】切断された電気ヒューズの切断状態を良好に保つ。

【解決手段】半導体装置100は、半導体基板(不図示)上に形成され、導電体により構成された電気ヒューズ200を含む。電気ヒューズ200は、切断前状態において、それぞれ異なる層に形成された上層配線134と、上層配線134に接続されたビア128と、ビア128に接続された下層配線122とを含み、切断状態において、導電体が上層配線134から外方に流出してなる流出部142が形成されるとともに、下層配線122とビア128との間に空隙部140が形成される。

(もっと読む)

半導体装置及び配線補助パターン生成方法

【課題】基板面内でのビアの分布の均一化が図られた半導体装置および配線補助パターンの生成方法を提供する。

【解決手段】

第1の配線と第1の配線の上層に配置された第2の配線とを有する半導体集積回路において、配線レイアウト情報をもとにビアパターンの密度が低い領域を抽出する。次に、選択された領域内のビアパターンの周辺領域において、第1の配線と第2の配線のいずれか一方に接続されたダミービアパターンを配置する。これにより、配線が混雑する箇所にもダミービアを配置することができる。

(もっと読む)

半導体装置

【課題】相異なる絶縁材料によって形成された層間絶縁膜間の界面では、同一の絶縁材料によって形成された層間絶縁膜間の界面に比して、剥離が生じ易い。

【解決手段】半導体装置1は、半導体基板10、層間絶縁膜20(第1の層間絶縁膜)、層間絶縁膜30(第2の層間絶縁膜)、および配線構造40を備えている。半導体基板10上には、層間絶縁膜20が設けられている。層間絶縁膜20は、第1の絶縁材料によって形成されている。層間絶縁膜20上には、層間絶縁膜30が設けられている。層間絶縁膜30は、第2の絶縁材料によって形成されている。ここで、第1および第2の絶縁材料は、相異なる絶縁材料である。半導体装置1の外周領域には、配線構造40が形成されている。配線構造40は、導電プラグを含んで構成され、層間絶縁膜20と層間絶縁膜30との界面を貫通している。

(もっと読む)

1 - 20 / 51

[ Back to top ]