Fターム[5F044MM24]の内容

Fターム[5F044MM24]に分類される特許

1 - 15 / 15

TAB(TapeAutomatedBonding)テープ、及び、半導体装置の製造方法

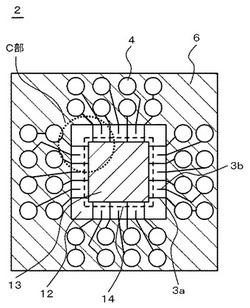

【課題】開口と、当該開口に先端が延在しているリードとを有するTAB(Tape Automated Bonding)テープにおけるリード変形を軽減する。

【解決手段】開口12を有する絶縁性フィルム6と、絶縁性フィルム6上から開口12内に延在し、半導体チップに環状に配置された複数の第1パッド各々に開口12内で接続する複数の第1リード3a、及び、第1パッドよりも外周側に環状に配置された複数の第2パット各々に開口12内で接続する複数の第2リード3bと、開口12内に位置し、複数の第1リード3aと繋がり、第2リード3bとは繋がらないリード端部保持部材13とを有するTABテープ。

(もっと読む)

プリント配線板およびその製造方法

【課題】 デバイスホールに突出するように設けられるフライングリードに寸法誤差や形状歪みや変形が発生することを抑制ないしは解消したプリント配線板およびその製造方法を提供する。

【解決手段】 絶縁性基材1の表面に、配線2と、デバイスホール4と、前記配線2に連なると共に前記デバイスホール4に突出するように設けられたフライングリード3とを有するプリント配線板であって、前記デバイスホール4が、少なくとも前記フライングリード3の先端を含むように設けられた第1のデバイスホール5(5a、5b、5c)と、当該第1のデバイスホール5よりも大きな面積を有し、かつ当該第1のデバイスホール5に対して少なくとも部分的に連続するように設けられた第2のデバイスホール6とからなるものである。

(もっと読む)

半導体装置用配線基板及びそれを用いた半導体装置

【課題】製品エリアの切断ラインに沿って導体装置用配線基板を切断する際に、同時に切断される配線の切断端から金属バリや金属異物が発生するのを抑制することができ、これにより隣接する配線間で短絡が発生するのを抑制することができる、半導体装置用配線基板及びそれを用いた半導体装置を提供すること。

【解決手段】基板2上に、半導体素子3の電極端子と接続される接続端子と液晶表示装置等の外部機器と接続される接続端子4とを備えた配線5を形成してなる、半導体装置用配線基板1であって、その切断ライン8に沿って切断することにより個別の半導体装置を得るように区画された製品エリア6を有し、製品エリア6の外側のエリアまで配線5を引き出してテストパッド7を形成すると共に、製品エリア6の切断ライン8と交差する部分10の配線5上に、有機材料からなる皮膜11を形成してなる、半導体装置用配線基板。

(もっと読む)

COF用フィルム、半導体装置およびCOF用フィルムの製造方法

【課題】半導体チップに接合されたインナリードの曲げによる応力を低減する手段を提供する。

【解決手段】ベースフィルムの半導体装置形成領域に設定されたチップ搭載領域と、チップ搭載領域に形成された複数のインナリードと、インナリードと端子との間を接続するアウタリードと、アウタリードを覆うソルダレジスト層と、を備えたCOF用フィルムにおいて、ソルダレジスト層のチップ搭載領域側に、厚さを厚くした厚膜部を形成する。

(もっと読む)

半導体実装回路テープ用スペーサテープ

【課題】本発明の目的は、回路テープの製造や保管のための共巻き用に使用されるスペーサテープであって、回路テープを損傷することがなく、製造が容易で生産性に優れるスペーサテープを提供することにある。

【解決手段】 本発明の半導体実装回路テープ用スペーサテープは、ベースプラスチックテープ2と、該ベースプラスチックテープの長さ方向に向けて連続的に固着された、少なくとも2列の幅がベースプラスチックテープの1/5以下であるスペーシングプラスチックテープ3とから少なくともなることを特徴とする。

(もっと読む)

電子部品実装用フィルムキャリアテープ、その製造方法、および、半導体装置

【課題】接続信頼性の高い電子部品実装用フィルムキャリアテープ、そのフィルムキャリアテープの製造方法、及び、そのフィルムキャリアテープを用いた半導体装置を提供する。

【解決手段】電子部品実装用フィルムキャリアテープ10は、電子部品50に形成されたバンプ電極52により電子部品50に接続して電子部品からの入出力信号を処理するためのインナーリード20、及び、インナーリード20からの信号を配線パターンを介して入出力処理するためのアウターリードを有する電子部品実装用フィルムキャリアテープ10において、電子部品50に形成されているバンプ電極52と接合するインナーリード20に、バンプ電極52が嵌合して接続する嵌合凹部54が形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】COF等のフリップチップやILBによるベアチップ実装において、配線基板の寸法変化に起因する半導体素子の電極との間の位置ずれを緩和する。

【解決手段】配線基板1は、導体配線2が延在して形成され、半導体素子4の領域の外側から半導体素子の第1素子電極列5と各々接合された第1接合用配線列9と、半導体素子領域の外側から半導体素子の第2素子電極列7と各々接合された第2接合用配線列10とを備える。第1接合用配線列を構成する各々の導体配線のピッチは、半導体素子領域の外側では第1素子電極列のピッチより広く、半導体素子の中心側の先端では第1素子電極列のピッチより狭くなるように連続的に変化しており、第2接合用配線列を構成する各々の導体配線のピッチは、半導体素子領域の外側では第2素子電極列のピッチより狭く、半導体素子の中心側の先端では第2素子電極列のピッチより広くなるように連続的に変化している。

(もっと読む)

COFパッケージ及びそれに用いるテープ基板

【課題】 チップの小型化と高信頼性を実現するCOFパッケージ及びそれに用いられるテープ基板を提供する。

【解決手段】

チップ非搭載領域に設けられた複数の外部入力端子及び複数の外部出力端子と、外部入力端子と接続される複数の入力配線と、外部出力端子と接続される複数の出力配線と、チップ非搭載領域からチップ搭載領域にわたって設けられるともに、入力配線間に設けられ、外部入力端子と接続される複数の内部入力配線と、チップ非搭載領域からチップ搭載領域にわたって設けられるともに、内部入力配線間に設けられたダミー配線と、を備えるテープ基板と、入力配線と接続される複数の入力電極と、入力配線と接続される複数の出力電極と、内部入力配線と接続される内部入力電極と、表面上の1辺に沿って、入力電極と間隔を空けて設けられると共に、ダミー配線と接続されるダミー電極と、を供える半導体チップから構成される。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】配線パターンにおけるエレクトロマイグレーションの発生を抑制できるようにした半導体装置の製造方法及び半導体装置を提供する。

【解決手段】ポリイミド等からなるフィルム1上に形成され、その表面がメッキ層で覆われているインナーリード2の接合位置にICチップ20のバンプ22を重ね合わせて接合する際に、インナーリード2の表面を覆うメッキ層5を接合時の熱で溶融し、溶融したメッキをインナーリード2の(フィルム1から剥がれた)先端部2aの剥離面へ回り込ませる。これにより、先端部2aの剥離面にもメッキ層が形成される。

(もっと読む)

半導体装置用テープキャリアおよびその製造方法

【課題】インナーリードボンディング時にリード未切断が発生せず、安定したボンディングが行えるようにした半導体用TABテープ及びその製造方法を提供する。

【解決手段】開口部11が設けられた樹脂テープ1上には、銅箔により配線リード20が形成されている。配線リード20には、開口部11に露出する部分にノッチ部21が設けられている。ノッチ部21のノッチ幅WNと、ボンディングツールが接触する部位のリード幅WL2(または樹脂テープ1の近傍のリード幅WL1)との比率、WN/WL1(またはWN/WL2)を0.5を超えて0.685以下にする。これにより、生産性が高く、高密度で小型な半導体装置用TABテープを得ることができる。

(もっと読む)

フィルムキャリアテープ、半導体アッセンブリ、半導体装置およびそれらの製造方法、実装基板および電子機器

【課題】本発明の目的は、CSP技術が適用されるフィルムキャリアテープ、半導体アッセンブリ、半導体装置及びこれらの製造方法並びに実装基板及び電子機器であって、表面にソルダレジストを塗布する必要のない技術を提供することにある。

【解決手段】表面にソルダレジストを塗布する必要のない半導体装置である。ポリイミドフィルム10の一方の面にリード54が形成され、ポリイミドフィルム10の他方の面から突出するように、ビアホール30を介してリード54上に外部接続用端子11が形成され、一方の面側にICチップ15が接着されているので、リード54がICチップ15にて覆われ、ソルダレジストの塗布を省略することができる。

(もっと読む)

フィルムキャリアテープ及び半導体装置

【課題】本発明の目的は、可能な限り従来の製造ラインや既存の技術を利用して、設備の負担や特殊技術の開発負担を軽減しつつ、製造工程におけるリードの曲がりを低減し、チップサイズのパッケージを高い信頼性の下に製造すると共に、歩留まりを向上させることにある。

【解決手段】TABのリード54a,54bの先端部はフレーム59に接続することなく、パターン形成のときから自由端としておき、最後のボンディング工程に至るまで、一切、加工を加えない。一方、半導体チップの実装領域において複数の連結部57a〜57jを配置し、1つのICチップの実装面の内側において多数のリードを連結し、その連結部を介して電気的にフレームに接続する。

(もっと読む)

配線基板及びそれを用いた半導体装置ならびにその製造方法

【課題】可撓性を有する絶縁基材上の導体配線と半導体子の素子電極とが突起電極を介して接合された構造において、接合時の超音波振動等に起因して導体配線の破損や断線を抑制する手段を提供する。

【解決手段】配線基板19は、絶縁基材10と、その上に設けられた複数の第1の導体配線11と、第1の導体配線に設けられた第1の突起電極13と、第1の導体配線の外端側にそれぞれ隣り合うように設けられた1本以上の第2の導体配線12を有する。半導体チップ18は、半導体素子20と、その上に設けられた素子電極21と、素子電極上に設けられた第2の突起電極22を有する。配線基板の第1の突起電極と半導体チップの第2の突起電極が対向して接合されることにより、第1の導体配線から半導体素子までが電気的に接続される。第2の導体配線は、第2の突起電極および半導体素子との間に隙間が設けられ、絶縁されている。

(もっと読む)

プリント配線基板、その製造方法および半導体装置

【課題】インナーリードの先端の変形による不良率が低減されたプリント配線基板およびその製造方法、半導体装置を提供する。

【解決手段】プリント配線基板10は、電子部品を実装するためのデバイスホール14を有する絶縁フィルム12の少なくとも一方の面に配線パターン18が形成されてなり、配線パターン18はデバイスホール14内にインナーリード20を構成し、他端部側にアウターリード22を構成している。デバイスホール14内に片持ち状態で延設されたインナーリード20の先端部は、デバイスホール14の各辺毎に連結部材30によって連接されており、該デバイスホール14の各辺毎に形成された連結部材30が、デバイスホール14の対向する辺に形成された連結部材30との間に形成された橋渡し構造によって相互に拘束しあっている。

【効果】インナーリードの変形が著しく低い安定した特性の製品を効率よく製造することができる。

(もっと読む)

印刷配線板およびその製造方法

【課題】本発明は、弾性率の低いポリイミド系複合物膜で微細配線を被覆することにより、電気絶縁性や高周波特性などの電気特性に優れ、軽量でしなやかさを有する印刷配線板、およびその製造方法を提供する。

【解決手段】本発明の印刷配線板は、樹脂フィルム基体の上に設けられた金属層からなる微細配線の少なくとも一部または全部がポリイミド系複合物膜で被覆されてなり、該ポリイミド系複合物膜が、(A)ポリイミド成分と、(B)その他のポリマー成分とから形成され、かつ、該複合物膜の弾性率が10GPa未満であることを特徴とする。

(もっと読む)

1 - 15 / 15

[ Back to top ]