Fターム[5F044QQ08]の内容

ボンディング (23,044) | ワイヤレスボンディング用半導体チップ (2,288) | ショート防止 (34)

Fターム[5F044QQ08]に分類される特許

1 - 20 / 34

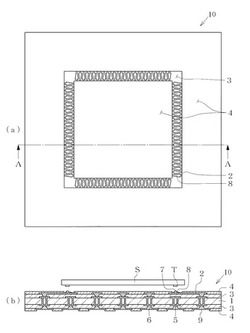

配線基板

【課題】高密度配列された電極端子を有する半導体素子を搭載する場合であっても、隣接する半導体素子接続パッド間にショートや電気的な絶縁不良を発生させることなく、正常に搭載することが可能な配線基板を提供すること。

【解決手段】複数の電極端子Tが下面の外周に沿って並ぶように配列された半導体素子Sを搭載するために、上面に電極端子Tと半田7を介して接続される複数の半導体素子接続パッド8が電極端子Tの配列と対応する並びに配列されて成る配線基板10であって、半導体素子接続パッド8は、互いに隣接するもの同士において、その幅が交互に反対方向に向けて広くなる形状であるとともに、その幅の広い部分に半田7の溜まりが形成されている。

(もっと読む)

電子装置及び電子部品

【課題】電子部品の電極間隔が狭い場合でもはんだバンプの高さを高くできるようにする。

【解決手段】UBM105の長さLuを開口104の1辺の長さLhよりも小さくする。これにより、UBM105の長さLuは比較例1のUBM105′の長さLu′よりも小さくなる。したがって、はんだバンプ300の底面部分の面積は、比較例1のはんだバンプ300′の底面部分の面積よりも小さくなる。その結果、はんだバンプ300の表面張力の作用によって、はんだバンプ300の体積を増やさずともその高さをはんだバンプ300′よりもΔhだけ高くすることができる。

(もっと読む)

半導体装置、それを用いた電子部品およびそれらの製造方法

【課題】エレクトロマイグレーション現象の発生を抑制して高い接続信頼性を確保すると共に、従来技術と同等以上の放熱性および導電性を確保したフリップチップ接続部を有する半導体装置およびそれを用いた電子部品を提供する。

【解決手段】本発明に係る半導体装置は、球状の金属コアを内蔵したはんだボールが配設されたフリップチップ接続部を備えた半導体装置であって、前記半導体装置は前記はんだボールと電気的接続されるランドおよび前記ランドと電気的接続される引出配線を有しており、前記金属コアは前記はんだよりも高い熱伝導率と電気伝導率とを有する材料からなり、前記ランドには前記はんだボールと接続する表面に球面状の窪みが形成されており、前記窪みの中心と前記引出配線との距離が前記ランドの中心と前記引出配線との距離よりも長いことを特徴とする。

(もっと読む)

導電接続シート、端子間の接続方法、接続端子の形成方法および電子機器

【課題】樹脂成分中に金属材料を残存させることなく、端子同士間に選択的に金属材料を凝集させて、これら端子同士を電気的に接続することができる導電接続シート、かかる導電接続シートを用いた端子間の接続方法、接続端子の形成方法、および、信頼性の高い電子機器を提供すること。

【解決手段】本発明の導電接続シート1は、樹脂組成物層11、13と、低融点の第1の金属材料で構成される第1の金属層121と、第1の金属材料より低融点の第2の金属材料で構成される第2の金属層122とを備える積層体により構成されるものであり、このものを、端子21有する半導体チップ(基材)上に配置する際に、端子21上に配置されるべき第1の部分15と、この第1の部分15以外の第2の部分16とからなり、第1の金属層121は、第1の部分15に対応して選択的に設けられている。

(もっと読む)

半導体素子、半導体素子実装体及び半導体素子の製造方法

【課題】狭ピッチに対してショート不良等を生じることなく、配線基板等に実装できるようにすること。

【解決手段】半導体素子10は柱状の接続端子15を備える。この接続端子15は、その先端15aの近傍部分において当該接続端子の横断面積が先端15aに向かって減小するよう形成されている。特定的には、接続端子15の形状は、先端15aの近傍部分を除いて円柱状であり、その近傍部分において当該接続端子の側面15bはテーパ状に形成されている。さらに接続端子15の、少なくともテーパ状に形成された側面15bに、はんだ濡れ性を向上させるための金属層が形成されていてもよい。

(もっと読む)

フリップチップボンデッドパッケージ

【課題】微細ピッチ技術に適用可能なフリップチップボンデッドパッケージを提供する。

【解決手段】2列に、かつ互いにジグザグに配列されるボンディングパッドを有する半導体チップ10aと、半導体チップ10a上の、隣接する3つのボンディングパッド毎に3つのパッド間の領域及びその3つのパッドのそれぞれの一部を覆うように形成された絶縁ポスト50aと、絶縁ポスト50aによって覆われていないボンディングパッドの部分及びこれに隣接した絶縁ポスト50aの部分上に形成された信号接続金属部材52aと、半導体チップ10aが絶縁ポスト50a及び信号接続金属部材52aによってフリップチップボンディングされ、第1面に電極を有し、第2面にボールランドを有する基板と、半導体チップ10aと基板との間の空間をアンダーフィルする埋込材と、各ボールランド上に付着されたソルダボールとを備える。

(もっと読む)

パッケージ、電子機器、パッケージ接続方法及びパッケージ修理方法

【課題】CSP及びBGAに搭載されている鉛フリーはんだボールに許容値内で高低差があった場合でも、未はんだやブリッジを防止することができるパッケージ、電子機器、パッケージ接続方法及びパッケージ修理方法を提供する。

【解決手段】半導体デバイス1が配置されたトップパッケージと配線6が配置されたボトムパッケージとを電気接続したパッケージ接続方法であって、少なくとも1以上の半導体デバイス1が配置され、少なくとも1以上の接続パット3に導電性のはんだボール2を搭載したトップパッケージの全てのはんだボール2の高さを揃える高さ揃え工程と、配線6が配置され、少なくとも1以上の接続パット5が配置されたボトムパッケージの少なくとも1以上の接続パット5の上にはんだボール2より融点の低いはんだ4が溶融され、前記トップパッケージと前記ボトムパッケージとを電気接続する接続工程と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】複数の半導体素子を積層させる半導体装置を低コストで製造する手段を提供する。

【解決手段】半導体装置31は、回路基板1上に第1の半導体素子10が実装されており、第1の半導体素子10の第1の電極パッド14上のハンダバンプ17に第2の半導体素子20の接続端子26が接合されている。第1の半導体素子10の第2、第3の電極パッド15,16はワイヤ18で回路基板1に電気的に接続されている。第1の半導体素子10と第2の半導体素子20の間の距離H0は、背高の接続端子26によって、ワイヤ18のループ高さH1以上になっている。

(もっと読む)

導電接続材料、端子間の接続方法、接続端子の製造方法、電子部材及び電気、電子部品

【課題】電子部材上の複数の端子等によって生じる凹凸を良好に埋め込むことができ、且つ、接続端子間において良好な電気的接続と隣接端子間において高い絶縁信頼性を得ることを可能にする導電接続材料、電子部材を電気的に接続する方法及び電子部材の電極上に簡便な方法で接続端子を製造する方法を提供すること。

【解決手段】本発明の導電接続材料は、樹脂組成物と、半田箔又は錫箔から選ばれる金属箔とから構成される積層構造を有するものであって、前記導電接続材料を電子部材の電極上に貼り付ける際の貼り付け温度をT[℃]、前記導電接続材料に掛ける圧力をP[Pa]、前記貼り付け温度における樹脂組成物の前記溶融粘度をη[Pa・s]としたとき、1.2×103≦(T×P)/η≦1.5×109の関係を満足し、前記貼り付け温度Tは、60〜150℃、前記圧力Pは、0.2〜1.0MPa、前記貼り付け温度における前記樹脂組成物の溶融粘度ηは、0.1〜10000Pa・sであることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】金属ナノ粒子を用いたフリップチップ接合において、印刷時とフリップチップ実装時の金属ナノ粒子の過剰な濡れ拡がりを抑制し、隣接電極とのショートを防止する。

【解決手段】第一の電極2を有する配線基板1と、前記第一の電極2と対向する位置に第二の電極6を有し前記配線基板1に実装される半導体素子5と、前記第一の電極2と前記第二の電極6との間に介在して電気的に接合される接合材料4とを備え、前記第一の電極2と前記第二の電極6の側面に撥液層3を形成し、該撥液層3を無電解めっきによるNiとPTFE(ポリテトラフルオロエチレン)からなる複合膜で形成する。

(もっと読む)

電子部品と可撓性基板との実装構造体

【課題】バンプ電極の樹脂の膨らみを吸収することにより、導電膜の幅の広がりを防止することができ、隣接する導電膜間の間隔を十分に確保することができ、導電膜を構成する金属によるマイグレーションが生じる虞が無く、ショート不良等が発生する虞の無い電子部品と可撓性基板との実装構造体を提供する。

【解決手段】本発明の実装構造体は、フレキシブル基板上に電子部品が加圧加熱により接着固定されて一体化された構成であり、この電子部品のバンプ電極23は、断面略蒲鉾状の突条の内部樹脂24がコアとされ、この内部樹脂24の外周面の長手方向に沿う帯状の導電膜を形成すべき複数箇所の両端部それぞれには、周方向に延在する溝25が形成され、この溝25を含む内部樹脂24上には、中央部が半円筒状とされ、この半円筒状の両端部が溝25の形状に沿って縮径されたつば状とされている導電膜26が形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】高電圧を印加した場合にも空中放電が生じにくく、耐圧を向上させた半導体装置を実現できるようにする。

【解決手段】半導体装置は、一の面に電極パッド103を有する半導体チップ101と、接続パッド201を有する実装基板200とを備えている。半導体チップ101の上には、電極パッド103を露出する開口部を有する保護膜105及び絶縁膜107が順次形成されている。電極パッド103の上には接続端子109が形成され、接続端子109は接続パッド201と接続され且つ絶縁膜107に囲まれている。絶縁膜107は実装基板200と密着している。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】2つの部材の接合の信頼性を向上し得る半導体装置の製造方法および半導体装置を提供する。

【解決手段】半導体装置の製造方法は、以下の工程を含む。基板本体1aに電極3aおよび3bを形成し、その上にバンプ5aおよび5bを配置する。半導体素子本体2aに電極4aおよび4bを形成する。バンプ5aおよび5bを加熱し電極3aおよび3bと電極4aおよび4bとを接合する(加熱工程)。電極3aおよび3bを形成する工程は以下の工程を含んでいる。下地電極11aおよび11bを形成し、その上の一部に、バンプ5aおよび5bとの反応を防止するためのバリア層13aおよび13bを形成する。接合する加熱工程は、電極3aおよび3bと電極4aおよび4bとを接近させて、加熱によって溶融したバンプ5aの一部をバリア層13a上からバリア層13aが形成されていない下地電極11a上にはみ出させることを含んでいる。

(もっと読む)

配線基板の製造方法

【課題】 配線基板の製造方法に関し、基板電極に予備はんだを印刷プリコート法で形成する際に、ブリッジを発生させることなく、且つ、均一なはんだ量の予備はんだを予め定めた位置に再現性良く形成する。

【解決手段】 基板上に形成された電極領域に末端基としてチオール基を有する有機物を付与する工程と、前記基板の表面に疎水性を付与する工程と、次いで、前記有機物を除去する工程と、次いで、前記電極領域にはんだを付着する工程とにより配線基板を製造する。

(もっと読む)

電子部品と電子部品の樹脂パッケージ方法

【課題】電子部品の全体の高さを低く抑えることのできる電子部品と電子部品の樹脂パッケージ方法を提供。

【解決手段】部品2の外周部が第1封止樹脂4によって取り囲まれ、第1封止樹脂4の内側に第2封止樹脂3が充填され、部品2と基板1がワイヤ5によって電気接続され、部品2の外周のエッジ部分のうちのワイヤ5が近傍を通過する辺が面取りされた傾斜面31に形成されており、ワイヤ5が傾斜面31に沿って基板1に延設されていることを特徴とし、電子部品の全体の高さを低く抑えることができる。

(もっと読む)

ICチップと外部配線との接続構造およびICチップ

【課題】接着材に含有される導電粒子数を増加することなく、チップ電極と電極端子との安定した導通を確保するとともに、各チップ電極の間の絶縁性を向上する。

【解決手段】駆動用ICチップ10のチップ基板11の一面のうち、平面形状における各チップ電極12の間隙部17よりも、導電粒子13bの流動方向における上流側に、導電粒子13bを各チップ電極12における各電極端子6、7と対向する面に案内するガイド19を設け、ガイド19を、ガイド19における前記流動方向の下流側の下流縁19aが各チップ電極12における流動方向の上流側の上流縁12aから離間して配置する。

(もっと読む)

ポストバンプ及びその形成方法

【課題】電解メッキにより発生するソルダのメッキ偏差から生じさせる不良を防止でき、リフロー時ソルダが必要以上に金属ポストの側面に広がることを防止することにより、ソルダの使用量を最小化できるポストバンプ及びその形成方法を提供する。

【解決手段】ポストバンプの形成方法は、電極パッドが形成されている基板に、電極パッドの形成位置に対応する開口部が形成されたレジスト層を形成する段階S200と、開口部の一部に金属性物質を充填し、金属ポストを形成する段階S300と、開口部の残りの一部にソルダを充填する段階S400と、ソルダに熱を加えてリフローする段階S500と、レジスト層を除去する段階S600と、を含むことを特徴とする。

(もっと読む)

半導体パッケージ、実装基板、およびこれらを含む半導体装置

【課題】実装基板に半導体パッケージが搭載される半導体装置において、はんだ実装後の隣接外部接続端子間のはんだブリッジを効果的に防止する。これにより、実装歩留まりが高く、実装性および実装信頼性に優れた半導体パッケージ、それを搭載する実装基板、および半導体装置を提供する。

【解決手段】半導体パッケージ101が、一方の面に複数の外部接続端子103が設けられた半導体パッケージであって、少なくとも一つの前記外部接続端子の周囲の一部または全部を囲むように壁状部材151が設けられている。

(もっと読む)

半導体装置

【課題】マイグレーション現象の発生を抑制することによって、信頼性の低下を抑制することが可能な半導体装置を提供する。

【解決手段】この半導体装置100は、ポリイミドフィルムからなる基材部1と基材部1上に形成された複数の配線リード2とを含むフィルム基板10と、複数の金バンプ21を含み、この金バンプ21を介して配線リード2のインナーリード部2aと電気的に接続された状態でフィルム基板10上に実装される半導体チップ20と、フィルム基板10と半導体チップ20との間に充填されるアンダーフィル樹脂層30とを備えている。そして、基材部1は、半導体チップ20が実装される実装領域3を有しており、基材部1における実装領域3の表面が、大気圧プラズマ処理またはKMnO4溶液を用いた表面処理によって粗化されている。

(もっと読む)

プリント回路板、電子機器、および半導体パッケージ

【課題】プリント回路板上の電子部品を搭載するためのスペースを効率的に利用する。

【解決手段】プリント回路板3は、回路基板20と、回路基板に対向する対向面と、当該対向面に形成された複数のバンプ12とを有し、当該複数のバンプを介して回路基板に接続された半導体パッケージ10と、回路基板と半導体パッケージとの間の領域において半導体パッケージの対向面の少なくとも各隅部近傍に配設され、回路基板と半導体パッケージとを接着する接着部材30と、を備える。

(もっと読む)

1 - 20 / 34

[ Back to top ]