Fターム[5F045BB12]の内容

気相成長(金属層を除く) (114,827) | 目的 (9,309) | 歪・反り防止 (1,345) | 結晶性・格子整合性の向上・結晶欠陥の防止 (911)

Fターム[5F045BB12]に分類される特許

901 - 911 / 911

積層欠陥核生成部位を低減する逐次的リソグラフィ方法および積層欠陥核生成部位を低減した構造

エピタキシャル炭化ケイ素層が、結晶学的方向に向かってオフアクシスに方向付けられた炭化ケイ素基板の表面内に第1の形態を形成することによって作製される。第1の形態は、結晶学的方向に対して非平行(すなわち、斜めまたは直角)に方向付けられた少なくとも1つの側壁を備える。次いで、第1のエピタキシャル炭化ケイ素層を、第1の形態を備える炭化ケイ素基板の表面上に成長させる。次いで、第2の形態が.、第1のエピタキシャル層内に形成される。第2の形態は、結晶学的方向に対して非平行に方向付けられた少なくとも1つの側壁を備える。次いで、第2のエピタキシャル炭化ケイ素層が、第2の形態を備える第1のエピタキシャル炭化ケイ素層の表面上に成長される。  (もっと読む)

(もっと読む)

積層欠陥核生成部位を低減するリソグラフィ方法および積層欠陥核生成部位を低減した構造

エピタキシャル炭化ケイ素層が、結晶学的方向に向かってオフアクシスに方向付けられた炭化ケイ素基板の表面内に形態を形成することによって作製される。これらの形態は、結晶学的方向に対して非平行(すなわち、斜めまたは直角)に方向付けられた少なくとも1つの側壁を備える。次いで、エピタキシャル炭化ケイ素層が、形態を備える炭化ケイ素基板の表面上に成長される。  (もっと読む)

(もっと読む)

炭化珪素エピキタシーにおけるニンジン状欠陥の低減

オフアクシス基板上の単結晶炭化珪素エピタキシャル層が、基板をエピタキシャル成長反応炉に配置し、基板上にエピタキシャル炭化珪素の第1の層を成長させ、エピタキシャル炭化珪素の第1の層の成長を中断し、第1の層の厚みを減少させるために該第1の層をエッチングし、エピタキシャル炭化珪素の第1の層の上にエピタキシャル炭化珪素の第2の層を再成長させて製造される。ニンジン状欠陥を、エピタキシャル成長処理を中断し、成長した層をエッチングし、エピタキシャル炭化珪素の第2の層を再成長させる工程によって終止できる。成長中断/エッチング/再成長の処理は複数回反復可能である。炭化珪素エピタキシャル層は、内部で終止する少なくとも1つのニンジン状欠陥を有する。半導体構造は、オフアクシス炭化珪素基板上の炭化珪素エピタキシャル層と、基板とエピタキシャル層の境界面の近傍に核形成点を有し内部で終止するニンジン状欠陥とを含む。

(もっと読む)

(もっと読む)

ゲルマニウム堆積

【課題】シード堆積プロセス130において、第一温度でシリコン含有表面上にゲルマニウムのシード層を堆積させることを含む方法。該シード層は、約1モノレイヤーと約1000Åの間の厚みを有する。該方法はさらに、該シード層堆積後、温度ランププロセス140においてゲルマニウムを堆積し続けながら該反応チャンバーの温度を上昇させることを含む。該方法はさらに、バルク堆積プロセス150においてゲルマニウムを堆積し続けながら、第二温度範囲で該反応チャンバーを保持することを含む。該第ニ温度範囲は該第一温度より高い。 (もっと読む)

高度な緩和及び低い積層欠陥密度を有する薄いSiGeオン・インシュレータ(SGOI)ウェハを形成する方法。

【課題】 高度な緩和及び低い積層欠陥密度を有する薄いシリコン・ゲルマニウム・オン・インシュレータ(SGOI)構造体を形成する方法を提供する。

【解決手段】 SiGe層(104)をSOIウェハ(102、100)上に堆積する(300)。SiGe及びSi層の熱混合を遂行し(302)、高度な緩和及び低い積層欠陥密度を有する厚いSGOI(106)を形成する。次に、SiGe層(110)が所望の最終の厚さにまで薄くする(306)。この薄層化処理によって、Ge濃度、緩和量、及び積層欠陥密度は不変に保持される。このようにして、高度な緩和及び低い積層欠陥密度を有するSGOI薄膜が得られる。次に、Si層(112)を薄いSGOIウェハ上に堆積する。薄層化方法には、低温(550℃−700℃)HIPOX又は蒸気酸化法、エピタキシ・チャンバ内でのその場の(in−situ)HClエッチング法、又はCMP法がある。HIPOX又は蒸気酸化薄層化から得られる粗いSiGe表面は、タッチ・アップCMP法、歪みSi堆積中でのその場の水素ベーク及びSiGeバッファ層、又は、HCl、DCS及びGeH4の気体混合物を有する水素環境中でウェハを加熱する方法、を用いて平坦化される。

(もっと読む)

エピタキシャルウェーハおよびその製造方法

シリコンウェーハの表裏面をSC−1液およびSC−2液で洗浄した後、シリコンウェーハの表裏両面をHF系溶液で洗浄して共に撥水面とする。この後、表面にシリコンのエピタキシャル層を成膜する。成膜後の積層欠陥を低減でき、裏面のクモリ発生を低減できる。または、シリコンウェーハの表裏面をSC−1液およびSC−2液で洗浄する。この後、シリコンウェーハの裏面をHF系溶液で洗浄して撥水面とするとともに、その表面を純水洗浄して親水面とする。この後、表面にシリコンのエピタキシャル層を成膜する。表面マウンドを低減でき、裏面のクモリ発生を低減できる。 (もっと読む)

高品質ホモエピタキシ用微傾斜窒化ガリウム基板

【数1】

方向または

【数2】

方向に主に向かう<0001>方向から、約0.2〜約10度の範囲のオフカット角度でオフカットされた(0001)表面を含むIII−V族窒化物、例えばGaN基板。表面が50×50μm2AFM走査により測定された1nm未満のRMS粗さと、3E6cm−2未満の転位密度とを有する。この基板は相当するブールまたはウェハブランクのオフカットスライスにより、オフカットラッピングまたは相当する微傾斜へテロエピタキシャル基板、例えばオフカットサファイア上の基板本体の成長により形成することができる。この基板はIII−V族窒化物系超小型電子および光電子デバイスの作製におけるホモエピタキシャル蒸着に有用に用いられる。  (もっと読む)

(もっと読む)

積層欠陥核生成サイトを減らして、バイポーラデバイスのVfドリフトを低減する方法

炭化珪素ベースのバイポーラデバイスにおいて、積層欠陥核生成を減らし、そして順方向電圧(Vf)ドリフトを低下させるための基板とエピタキシャル層とを作製する方法を開示している。本発明方法は、炭化珪素基板の表面を非選択性エッチングして、表面損傷及び表面下損傷の両方を除去する工程;その後で、選択性エッチングによって同じ表面をエッチングし、それによって、その後に終端する傾向があるか又は該基板表面上でその次のエピタキシャル層成長中に貫通欠陥として伝播する傾向がある該基板表面に達している少なくともいくらかのベーサルプレーン転位からエッチング生成構造を発生させる工程、そして、その後に、二回エッチングされた表面上に炭化珪素の第一エピタキシャル層を成長させる工程を含む。  (もっと読む)

(もっと読む)

緩和シリコンゲルマニウム層のエピタキシャル成長

緩和シリコンゲルマニウム構造は、約1Torrより高い操作圧力での化学気相成長法を用いて提供されるシリコンバッファ層を含む。この緩和シリコンゲルマニウム構造は、シリコンバッファ層上に堆積されたシリコンゲルマニウム層をさらに含む。このシリコンゲルマニウム層は、1平方センチメートル当り約107未満の貫通転位を有する。減少した堆積速度でシリコンバッファ層を堆積させることによって、シリコンゲルマニウム層に「クロスハッチフリー」表面が付与され得る。  (もっと読む)

(もっと読む)

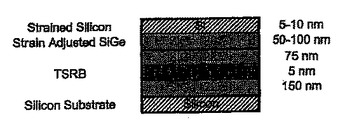

半導体装置、および薄層歪緩和バッファ成長方法

本発明は、半導体基板を含み、その上部に少なくとも薄層歪緩和バッファを有し、本質的に3層のスタックから成っている半導体装置に関するものであり、その薄層歪緩和バッファは半導体装置のアクティブ部分でなく、さらに、薄層歪緩和バッファを形成する前記3層が本質的に一定のGe濃度を有することを特徴としている。前記3層は以下の通りである:Si1−xGexの第1エピタキシャル層、xはGe濃度である;前記第1エピタキシャル層上の、Si1−xGex:Cの第2エピタキシャル層、Cの量は少なくとも0.3%である;前記第2層上のSi1−xGexの第3エピタキシャル層。

(もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 欠陥のないエピタキシャル膜を形成する

【解決手段】 異物除去処理を有し、ドライエッチング処理を行って形成した開口部5内の単結晶シリコン基板1に、SiGeエピタキシャルベース7を成長させる半導体装置の製造方法である。異物除去処理は、前記ドライエッチング処理後からSiGeエピタキシャルベース7の成長までの間に、被成長基板を酸素雰囲気中において、熱処理を行い、ドライエッチング処理によって、シリコン酸化膜2に堆積した炭素系付着物10を、シリコン酸化膜2から完全に除去し、これによって、欠陥のないエピタキシャル膜を形成する。

(もっと読む)

901 - 911 / 911

[ Back to top ]