Fターム[5F045DB03]の内容

気相成長(金属層を除く) (114,827) | 半導体層の選択成長 (353) | 絶縁体マスク (266) | 単結晶と非晶質・多結晶の同時成長 (10)

Fターム[5F045DB03]に分類される特許

1 - 10 / 10

シリコンと炭素を含有するインサイチュリンドープエピタキシャル層の形成

【課題】堆積速度が速く、好ましくは約700℃以下のような低いプロセス温度を維持し、置換型炭素濃度が高い、SiとCを含有する選択エピタキシャル層を得る方法を提供する。

【解決手段】基板上にSiとCを含有するエピタキシャル層を形成する方法であって、単結晶表面と、アモルファス表面、多結晶表面及びこれらの組み合わせより選ばれる少なくとも一つの第二表面とを含む基板をプロセスチャンバ内に配置するステップと、プロセスチャンバ内の圧力を少なくとも300トールに維持しつつ、該基板をシリコン源と、炭素源と、リン源にさらして、該基板の少なくとも一部にリンがドープされたSi:Cエピタキシャル膜を形成するステップと、700℃以下のプロセスチャンバ内の温度の下で、HClを含むエッチングガスに該基板をさらすことにより該基板を更に処理するステップと、を含む。

(もっと読む)

半導体結晶基板、半導体結晶基板の製造方法、半導体装置の製造方法、電源装置及び増幅器

【課題】基板の外周部においてクラックの発生が抑制される半導体結晶基板を提供する。

【解決手段】半導体結晶基板110と、基板110の表面に窒化物により形成された保護層120と、を有し、保護層120は、基板110の外周部となる周辺領域120aはアモルファス状態であり、基板110の周辺領域よりも内側の内部領域120bは結晶化している。

(もっと読む)

エピタキシャルウエハの製造方法

【課題】 半導体ウエハの端面に角張った形状の結晶層を成長させることなく、半導体ウエハ上に厚い単結晶層を成長させることができる技術を提供する。

【解決手段】 半導体ウエハ10上に単結晶層30が形成されたエピタキシャルウエハの製造方法であって、平坦な上面12と、平坦な下面14と、上面12と下面14を接続する端面16を有する半導体ウエハ10の端面16上に、アモルファス層20を形成するアモルファス層形成工程と、アモルファス層形成工程後に、半導体ウエハ10の上面12上に、80μm以上の厚みを有する単結晶層30を気相成長させる単結晶層形成工程を有する。

(もっと読む)

化合物半導体装置の製造方法及び化合物半導体装置

【課題】工程増を最小限とした簡便な手法で、基板に反りを生ぜしめることなく、また基板上方の化合物半導体層の結晶性を損なうことなく確実な素子分離を実現し、信頼性の高い装置構成を得る。

【解決手段】SiC基板1上の素子分離領域に相当する部位にマスク2を形成し、マスク2を覆うようにSiC基板1上に緩衝層3を第1の温度で形成し、第1の温度より高い第2の温度で加熱処理して緩衝層3のうちSiC基板1上の部位を結晶化し、緩衝層3の上方に化合物半導体層10を形成して、化合物半導体層10のマスク2の上方に相当する部位を素子分離領域とする。

(もっと読む)

半導体製造方法と装置

【課題】部分的に絶縁膜が形成されているシリコン基板上を単結晶で覆うことができる半導体装置の製造方法及び基板処理装置を提供する。

【解決手段】部分的に絶縁膜が形成されたSi基板10上に、a−Si膜14を成膜する(図1(b))。このSi基板10を熱処理すると、基板のSi結晶を種としてa−Siが固相Epi化される(図1(c))。基板の厚さ方向に対して充分にEpi結晶化された範囲を保護するようにレジスト膜18を形成し(図1(d))、エッチング処理を行い(図1(e))、その後、アッシング処理によってレジスト膜18を剥離し、このSi基板10上に再度a−Si膜を成膜する(図1(f))。再度、上記熱処理を行うことで、a−Siが固相Epi化される(図1(g))。

(もっと読む)

半導体発光素子及びそれに用いる素子形成用基板

【課題】 動作電圧の低減が可能な半導体発光素子及びそれに用いる素子形成用基板を提供する。

【解決手段】 本発明に係る半導体レーザ50は、GaN単結晶基板30の表面に活性層34を含む積層体38が形成されると共に、GaN単結晶基板30の裏面に欠陥集合部14aが形成され、且つ、裏面の欠陥集合部14aと電気的に接続されるように電極44が形成されている。この半導体レーザ50の欠陥集合部14aは、結晶欠陥が多いことから、キャリア濃度が高くなっており、電気抵抗が有意に低減されている。そのため、この欠陥集合部14aに電極44を形成した本発明に係る半導体レーザ50においては、GaN単結晶基板30と電極44との間でオーミックコンタクトが取りやすくなっており、それにより駆動電圧の低減が実現されている。

(もっと読む)

半導体膜の選択的なエピタキシャル形成

反復して行うブランケット堆積と選択的エッチングとのサイクル的なプロセスによって、半導体ウィンドウ(114)内にエピタキシャル層(125)を選択的に形成する。ブランケット堆積フェーズは、フィールド酸化物等の絶縁領域(112)上へ非エピタキシャル材料(120)を残し、選択的なエッチングフェーズは、優先的に非エピタキシャル材料(120)を除去し、且つ、堆積されるエピタキシャル材料(125)はサイクル毎に堆積される。エピタキシャル材料(125)の品質は、絶縁体(112)上で堆積が発生しない選択的プロセスよりも向上する。プロセスのエッチングフェーズ中にゲルマニウム触媒を使用することは、エッチング速度を促進し、且つ、複数のサイクルを介する等温および/または等圧条件の維持費用の節約を容易にする。スループットおよび品質は、トリシランの使用、絶縁領域(112)上への非晶質材料(120)の形成、および各堆積フェーズにおける非晶質:エピタキシャル材料の厚さの比の最小化によって向上する。 (もっと読む)

非単結晶半導体材料、光電変換素子、発光素子、および非単結晶半導体材料の製造方法

【課題】アモルファスシリコン材料中にナノ結晶をほぼ均一に埋め込んだナノ結晶埋め込み型アモルファス材料を実現し、優れた特性を持つ非単結晶半導体材料、光電変換素子、発光素子、および非単結晶半導体材料の製造方法を提供する。

【解決手段】シリコン及び/又はゲルマニウムを主体とするアモルファス材料3中に粒径1nm〜5nmの結晶シリコン及び結晶ゲルマニウム2を散在させた非単結晶半導体材料1。

(もっと読む)

エピタキシャル膜の形成方法と、これを用いた薄膜形成方法、及び半導体装置の製造方法

【課題】 エピタキシャル膜の形成方法と、これを用いた薄膜形成方法、及び半導体装置の製造方法が開示される。

【解決手段】 エピタキシャル膜の形成方法と、これを用いた薄膜形成方法、及び半導体装置の製造方法において、第1単結晶シリコン膜上に前記第1単結晶シリコン膜の表面を部分的に露出させる開口部を有する第1絶縁膜パターンを形成した後、前記開口部によって露出された第1単結晶シリコン膜上に単結晶シリコンで構成された第1シード膜を形成する。そして、前記第1シード膜が形成された結果物上部にシリコンソースガスを提供して、前記第1シード膜上にエピタキシャル膜を成長させながら、前記第1絶縁膜パターン上に非晶質シリコン膜を形成する。その後、前記非晶質シリコン膜の結晶構造を単結晶に転換させて前記エピタキシャル膜と非晶質シリコン膜から第2単結晶シリコン膜を獲得する。

(もっと読む)

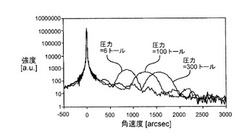

シリコン−ゲルマニウム・エピタキシャル成長における歩留りの向上

【課題】半導体構造の歩留りを向上させるSiGe付着条件を決定する方法を提供すること。

【解決手段】この半導体構造の製造は単結晶シリコン(Si)層から開始される。次いでこの単結晶Si層内に、第1および第2の浅いトレンチ分離(STI)領域を形成する。これらのSTI領域は第1の単結晶Si領域を間に挟み、これを画定する。次に、この構造の上にシリコン−ゲルマニウム(SiGe)混合物を、あるSiGe付着条件で付着させて、(i)第1の単結晶シリコン領域の上面から第2の単結晶シリコン領域を成長させ、(ii)第1および第2のSTI領域の上面からそれぞれ第1および第2のポリシリコン領域を成長させる。その結果として得られる歩留りが予め指定された範囲内に収まるまで、SiGe付着温度を高くし、または前駆体流量を小さくし、あるいはその両方を実施することによって、この構造を大量生産するための満足のいくSiGe付着条件を決定することができる。

(もっと読む)

1 - 10 / 10

[ Back to top ]