Fターム[5F048AC07]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 集積回路要素 (9,617) | バイポーラを含む (260)

Fターム[5F048AC07]の下位に属するFターム

Bi−MOS複合素子 (60)

Fターム[5F048AC07]に分類される特許

1 - 20 / 200

半導体装置の製造方法

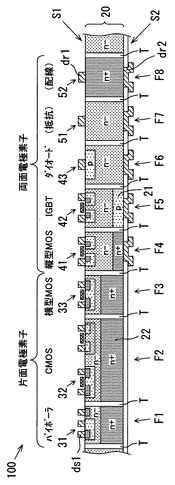

【課題】能動素子または受動素子が一つの半導体基板に複数個形成されてなる半導体装置およびその製造方法であって、両面電極素子についても絶縁分離と集積化が可能であり、安価に製造することのできる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板20が、当該半導体基板20を貫通する絶縁分離トレンチTに取り囲まれて、複数のフィールド領域F1〜F8に分割されてなり、複数個の能動素子31〜33,41〜43または受動素子51,52が、それぞれ異なるフィールド領域F1〜F8に分散して配置されてなり、二個以上の素子が、当該素子に通電するための一組の電極dr1,dr2が半導体基板20の両側の表面S1,S2に分散して配置されてなる、両面電極素子41〜43,51,52である半導体装置100とする。

(もっと読む)

半導体装置の製造方法

【課題】ライフタイムキラーが形成されてなる半導体装置において、オン電圧ばらつきや特性ばらつきを抑制することのできる半導体装置の製造方法を提供する。

【解決手段】半導体基板1aの裏面からコレクタ層10を構成する不純物をイオン注入するイオン注入工程と、半導体基板1aの裏面からレーザを照射し、不純物を活性化させてコレクタ層10を形成する活性化工程と、半導体基板1aの裏面からレーザを照射してライフタイムキラー13を形成するライフタイムキラー形成工程とを行う。これによれば、レーザを照射してライフタイムキラー13を形成しているため、ライフタイムキラー13の分布幅は波長のみに依存する。このため、ライフタイムキラー13をイオン照射により形成する場合と比較して、分布幅がばらつくことを抑制することができ、オン電圧ばらつきや特性ばらつきを抑制することができる。

(もっと読む)

低抵抗及び低インダクタンスの裏面貫通ビア及びその製造方法

【課題】裏面コンタクト構造体及びその構造体を製造する方法を提供する。

【解決手段】表面及び対向する裏面を有する基板100の表面上に第1誘電体層105を形成することと、第1誘電体層を貫通して前記基板の表面にまで延びる導電性の第1スタッド・コンタクト140Bを第1誘電体層内に形成することと、基板の裏面から基板を薄くして基板の新しい裏面を形成することと、基板の新しい裏面から前記第1誘電体層まで延びるトレンチ165を基板内に形成して第1スタッド・コンタクトの底面をトレンチ内に露出させることと、基板の新しい裏面、トレンチの側壁、第1誘電体層の露出面、及び第1スタッド・コンタクトの露出面の上に、トレンチを完全に充填するのに十分には厚くない共形導電層170、175を形成することと、を含む前記方法。

(もっと読む)

窒化物半導体装置

【課題】ダイオード等の保護素子の外付けによる部品点数の増加及び占有面積の増大を抑えた、双方向に高いアバランシュエネルギー耐量を有する窒化物半導体装置を提供する。

【解決手段】半導体基板10は、第1のn型領域12A、第2のn型領域12Bとともにトランジスタ11を構成する。半導体基板10の裏面には、裏面電極13が接合され、また、半導体基板10の上には、HFET21が形成されている。HFET21は、AlGaN層23A及びGaN層23Bを備える半導体層積層体23と、第1のオーミック電極24A、第2のオーミック電極24B、第1のゲート電極25A、第2のゲート電極25Bにより構成されている。第1のオーミック電極24Aと第1のn型領域12A、第2のオーミック電極24Bと第2のn型領域12Bはそれぞれ電気的に接続されている。

(もっと読む)

半導体構造

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、半導体構造を提供することを目的とする。

【解決手段】下部誘電層(151)へ接合された基板(103)、および、下部電極(121)を通じて前記下部誘電層(151)と接合される垂直方向半導体装置(111)を含む半導体構造であって、前記垂直方向半導体装置(111)は、n+−p−n+層(124)を有する隔離構造(135)を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】互いに絶縁分離された複数の素子を有する半導体装置の小型化と、その製造コストの低減とを実現できるようにする。

【解決手段】半導体装置は、第1の素子151、第2の素子152、第3の素子153及び第4の素子154を備えている。基板100は、基板を貫通する第1素子分離領域131により互いに分離された第1の区画101及び第2の区画102を有している。第1の区画は、第2素子分離領域132により互いに分離された第1素子領域121及び第2素子領域122を含む。第2の区画は、第3素子分離領域133により互いに分離された第3素子領域123及び第4素子領域124を含み、基板の裏面に露出した裏面拡散層を有している。第3の素子は、第3素子領域に形成され、第4の素子は、第4素子領域に形成され、第3の素子及び第4の素子は、裏面拡散層105を介在させて互いに接続されている。

(もっと読む)

半導体装置及び半導体素子

【課題】本発明は、スイッチング損失を低減できる半導体装置及び半導体素子を提供することを目的とする。

【解決手段】本発明に係る半導体装置は、第1ゲートを有し該第1ゲートからの信号でオンオフが制御される第1素子部と、第2ゲートを有し該第2ゲートからの信号でオンオフが制御される第2素子部と、を有する半導体素子と、該第1ゲート及び該第2ゲートに接続され、該半導体素子をターンオンするときは該第1素子部と該第2素子部を同時にターンオンし、該半導体素子をターンオフするときは該第2素子部を該第1素子部よりも遅延してターンオフするように該第1ゲートと該第2ゲートに信号を伝送する信号伝送手段と、を備えたことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】 高い位置精度でIGBT領域にイオンを注入することができる技術を提供する。

【解決手段】 IGBTとダイオードを有する半導体装置の製造方法であって、半導体基板12のうちのIGBTが形成される半導体領域であるIGBT領域20の上面を覆わず、かつ、半導体基板12のうちのダイオードが形成される半導体領域であるダイオード領域40の上面を覆うように半導体基板12の上面に金属層70を形成する金属層形成工程S12と、金属層形成工程S12後に半導体基板12の上面側から半導体基板12に向けてイオンを照射するイオン照射工程S14を有しており、製造される半導体装置10において、前記金属層70がダイオードの電極となる。

(もっと読む)

半導体装置及びDC−DCコンバータ

【課題】耐久性が高い半導体装置及びDC−DCコンバータを提供する。

【解決手段】実施形態に係る半導体装置は、高電位側電源電位に接続するための第1の配線と、前記高電位側電源電位に接続するための、前記第1の配線とは別の第2の配線と、前記第1の配線に一端が接続され、他端が出力端子に接続されるスイッチングトランジスタと、前記高電位側電源電位と前記低電位側電源電位との間で前記スイッチングトランジスタと並列に接続される保護素子とを備える。前記保護素子は、前記第1の配線に接続される、第1のp形半導体領域と、前記第2の配線に接続される、前記第1のp形半導体領域に接したn形半導体領域と、前記n形半導体領域に接し、前記第1のp形半導体領域から離隔し、前記低電位側電源電位に接続するための配線に接続される第2のp形半導体領域と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】異なる不純物濃度の埋め込み層を有する半導体装置を短時間かつ低コストで製造する方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板の表面に第1の酸化膜11を形成する第1の酸化膜形成ステップと、フォトダイオードが形成される第1の領域に形成された前記酸化膜の一部を除去して第1の間隔で第1の開口部を形成すると共に、トランジスタが形成される第2の領域に形成された前記酸化膜を除去して前記半導体基板の表面を露出させる第1の開口部12を形成ステップと、前記第1の酸化膜をマスクとして利用して前記第1の開口部及び前記第2の領域に対して第1の不純物を注入する第1の不純物注入ステップと、前記第1の不純物を熱拡散させる第1の熱拡散ステップと、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】埋め込み絶縁層により活性層と支持基板とが電気的に絶縁された半導体基板において、支持基板の電位を活性層の表面から取り出すための基板コンタクトの低抵抗化を図ることができる半導体装置およびその製造方法を提供すること。

【解決手段】活性層16に素子領域4およびコンタクト領域5が形成された厚膜SOI基板2において、CMOSトランジスタ7のB/L層29およびL/I層37、npnバイポーラトランジスタ8のコレクタ層49と同一層に、n型基板コンタクト12の貫通コンタクト58を取り囲むn型コンタクト埋め込み層57を形成する。

(もっと読む)

過電圧保護回路及び半導体集積回路

【課題】異常な過電圧から内部回路を確実に保護することができる過電圧保護回路を提供する。

【解決手段】過電圧保護回路2Aは、整流素子D10と、互いに並列に接続された第1段から第n段(nは2以上の整数)のスイッチング素子NM1〜NMnとを備える。スイッチング素子NM1〜NMnは、整流素子D10の出力端からの出力電圧が印加される第1から第nの制御端をそれぞれ有する。また、スイッチング素子NM1〜NMnの各々は、第1端子3及び第2端子4にそれぞれ接続された被制御端を有する。整流素子D10は、第1端子3から過電圧が入力されたとき、スイッチング素子NM1〜NMnをオン状態にする制御電圧を出力する。

(もっと読む)

3次元デバイスの集積化方法および集積デバイス

【課題】高い集積密度を有するデバイス及び集積化方法の提供。

【解決手段】第1および第2の加工物の表面を各々約5〜10Åの表面粗さまで研磨し、第1および第2の加工物の研磨された表面は、互いに接合される。第3の加工物の表面は、前記表面粗さまで研磨される。第3の加工物の表面は、第1および第2の加工物に接着される。第1、第2および第3の加工物は、各々好ましくはウエハ形態にある1つの表面上に形成される薄い材料を有する半導体デバイスであり得る。薄い材料は、所望の表面粗さまで研磨され、その後、互いに接合される。薄い材料は、各々この薄い材料が上に形成される材料の表面非平面度の約1〜10倍の厚さを有する。多数のデバイスが互いに接合され得、デバイスは、異なるタイプのデバイスまたは異なる技術であり得る。

(もっと読む)

半導体装置

【課題】逆耐圧を高くしてもオン抵抗が高くなることのない半導体装置を提供する。

【解決手段】n型半導体層116と、n+型半導体層116よりも低濃度のn型不純物を含有するn型のドリフト層112と、ドリフト層112の表面に形成した、拡散深さが深いボディ部分118aと、拡散深さが浅いチャネル部分118bとからなるp型のボディ領域118と、ボディ領域118の表面に形成したn+型のソース領域120と、チャネル部分118bの上にゲート絶縁層122を介して形成したゲート電極124とを備える半導体装置であって、平面的に見てボディ領域118と重ならない領域に位置するドリフト層112には、ドリフト層112よりも高濃度のn型不純物を含有するn型の低抵抗領域144aがn+型半導体層116と接するように形成されている半導体装置100。

(もっと読む)

浅いトレンチ分離および基板貫通ビアの集積回路設計への統合

【課題】浅いトレンチ分離および基板貫通ビアの集積回路設計への統合を提供すること。

【解決手段】ICを製造する方法は、第1の側、および第2の対向する側を有する基板を用意すること、基板の第1の側にSTI開口を形成すること、および基板の第1の側に部分的TSV開口を形成すること、および部分的TSV開口を延長することを含む。延長された部分的TSV開口は、STI開口より基板内への深さが深い。方法はまた、STI開口を第1の固体材料で充填すること、および延長された部分的TSV開口を第2の固体材料で充填することを含む。STI開口、部分的TSV開口、または延長された部分的TSV開口のいずれも、基板の第2の側の外面を貫通しない。少なくとも、STI開口および部分的TSV開口は同時に形成され、またはSTI開口および延長された部分的TSV開口は同時に充填される。

(もっと読む)

半導体装置

【課題】同一基板上に混載された他の素子の誤動作を抑制できる半導体装置を提供する。

【解決手段】半導体装置は、p形半導体層12と、n形のソース領域13と、絶縁体23と、n形半導体領域20と、n形のドレイン領域14と、p形のチャネル領域12aと、ゲート絶縁膜15と、ゲート電極16と、ソース電極18と、ドレイン電極19と、電極21とを備える。前記絶縁体は、前記p形半導体層の表面から前記p形半導体層の厚み方向に延びて形成されたトレンチt1内に設けられている。前記n形半導体領域は、前記ドレイン領域と前記絶縁体との間の前記p形半導体層の表面に設けられる。前記電極は、前記n形半導体領域に接続される。

(もっと読む)

半導体製造方法および半導体装置

【課題】ウェーハテスト後のウェーハ状態において所望の回路を印刷処理により容易に形成することが可能な半導体製造方法および半導体装置を提供することを課題する。

【解決手段】本発明に係る半導体製造方法は、ウェーハの被描画パターン形成領域に所定の深さを有する溝部を形成する工程、ウェーハに対してトリミング要否の検査を行う工程、前記ウェーハにおけるトリミング必要なウェーハの前記溝部に導電性溶剤を射出し描画パターンを描画する工程、描画パターンを描画した後、脱気および低温アニールする工程、脱気および低温アニールした成膜後、当該成膜表面を平坦化する工程、および平坦化した後、高温アニールする工程、を有する。

(もっと読む)

半導体装置

【課題】ホールド電圧を変化させずに、トリガー電圧のみを調節することができるようにする。

【解決手段】本実施形態における保護素子10は、低濃度コレクタ層102、シンカー層110、高濃度コレクタ層112、エミッタ層130、高濃度ベース層122、ベース層120、第1導電型層140、及び第2導電型層150を有している。第2導電型層150は低濃度コレクタ層102に形成されており、ベース層120と第1導電型層140の間に位置している。第2導電型層150は低濃度コレクタ層102よりも不純物濃度が高い。

(もっと読む)

エピレス基板における分離型の相補型MOS装置

【課題】高い実装密度を得ることが可能な半導体装置の製造プロセスを提供する。

【解決手段】半導体装置を電気的に分離するための構造は、エピタキシャル層を含まない半導体基板240内にドーパントを打込むことにより形成される。この打込みに続き、極めて限られた熱収支に上記構造を晒すことでドーパントが顕著に拡散しないようにする。その結果として、上記分離構造の寸法が制限かつ規定され、こうして、エピタキシャル層を成長させる工程とドーパントを拡散させる工程とを含む従来のプロセスを用いて得られるよりも高い実装密度を得ることができる。

(もっと読む)

アッド‐オン層形成方法

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、堆積可能なアッド‐オン層形成方法を提供することを目的とする。

【解決手段】堆積可能なアッド‐オン層形成方法であって、第一半導体基板の取り外し層の形成、取り外し層の上の第一半導体基板に多くのドーピング領域の形成、ここで多くのドーピング層の形成は、第一電導型を有するように、ドーピングされ、取り外し層の上の第一半導体基板の第一ドーピング層の形成、第一電導型に対する第二電導型を有するようにドーピングされ、第一ドーピング層の上の第一半導体基板に最低中間ドーピング層の形成、及び中間ドーピング層上の第一半導体基板に最低第三ドーピング層の形成からなり、第三ドーピング層上に第一の電導性ブランケット層の形成、第一電導ブランケット層上に第二の電導性ブランケット層の形成、及び第二電導性ブランケット層が第二半導体基板の対応する電導性上部層と接触するように、第一半導体基板を第二半導体基板への取り付け、からなる。

(もっと読む)

1 - 20 / 200

[ Back to top ]