Fターム[5F048AC10]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 集積回路要素 (9,617) | L、C、R、ダイオード等を含む (1,648)

Fターム[5F048AC10]に分類される特許

1,641 - 1,648 / 1,648

電界効果型半導体装置における容量素子の動的制御

電界効果型装置はキャパシタのプレートをそれぞれ形成する複数のセグメントを有する少なくとも1つのセグメント化されたフィールド・プレートを含んでおり、選択されたセグメントを動的に接続してゲート−ドレイン間容量及びドレイン−ソース間容量を選択的に設定する電子素子に電界効果型装置が接続されている。トランスデューサを送信モードスイッチング装置と、受信モードスイッチング装置との間でスイッチングするスイッチング装置に結合されたトランスデューサを超音波装置が含んでおり、このスイッチング装置は電界効果型装置を含んでいる。  (もっと読む)

(もっと読む)

パンチスルー・ダイオードおよびそれを処理する方法

ショットキーのような動作を有するモノリシック集積パンチスルー・ダイオード。これは、ショットキー金属領域(16)が第1のpドープ・ウェル(9)の表面の少なくとも一部に堆積されるときに実現される。ショットキー金属領域(16)およびpドープ・ウェル(9)は、ショットキー・ダイオードの金属−半導体−遷移を形成する。順方向特性が0.5V未満の電圧降下を有するので、発明のPTダイオードの過電圧保護は改善される。  (もっと読む)

(もっと読む)

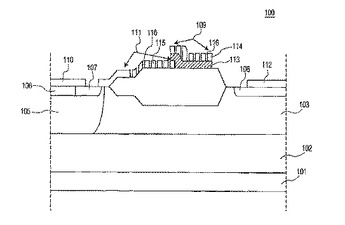

半導体装置および半導体装置の製造方法

【課題】SOI層に形成された素子の誘電損失をより低減させることが可能な半導体装置およびその製造方法を提供することにある。

【解決手段】支持基板1の一部を除去して溝Gを形成する。溝Gは,支持基板1による誘電損失が想定される素子の直下に位置するように形成される。溝Gには,誘電体としてのシリコン結晶が薄くしか存在しないか,あるいは全く存在しないため,その上に位置する素子の誘電損失は極めて小さなものとなる。この素子が高周波回路の構成要素であるならば,この高周波回路は,高周波信号の処理に関して,高い応答性や安定性を発揮することになる。

(もっと読む)

信号伝送システム

【課題】 できるだけ従来のシステム構成と部品構成を肯定しながら、数十GHz帯のディジタル高速信号を通すための信号伝送技術を提供する。

【解決手段】 電子回路全体に渡るトランジスタの論理回路、メモリ回路に含まれるドライバ1とレシーバ2の構成において、ドライバ1は信号伝送線路3を通じてレシーバ2に、電源・グランド伝送線路4を通じて電源Vddにそれぞれ接続される信号伝送システムであって、ドライバ1およびレシーバ2は全て実質的差動入力、差動出力とし、ドライバ1の実質的差動出力の出力端では電源またはグランドへの接続を有することなく、またレシーバ2は実質的差動入力の信号の電位差を検知することで受信し、さらに信号伝送線路3は分配配線がない、構造とする。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】 サブミクロンCMOSトランジスタを、アナログCMOSトランジスタ、高耐圧MOSトランジスタ、バイポーラトランジスタ、ダイオードまたは拡散抵抗などと一緒に、それぞれの特性を劣化させることなく、同一基板上に混載すること。

【解決手段】 半導体基板1の一主面側にパンチスルーストッパー層を形成する際に、アナログCMOSトランジスタ、高耐圧MOSトランジスタ、バイポーラトランジスタ、ダイオードまたは拡散抵抗を形成する領域をマスクしてたとえばイオン注入をおこなう。それによって、サブミクロンCMOSトランジスタの形成領域にパンチスルーストッパー領域4を形成するとともに、アナログCMOSトランジスタ、高耐圧MOSトランジスタ、バイポーラトランジスタ、ダイオードまたは拡散抵抗の形成領域にパンチスルーストッパー領域が形成されるのを防ぐ。

(もっと読む)

パワー半導体装置

【課題】

【解決手段】 ユニットセル部UCPの周囲及びゲートパット部GPPの周囲を第1方向D1乃至第4方向D4に関して完全に取り囲むチップ周辺部CPP内に、ツエナーダイオード11を配設する。ツエナーダイオード11は、各層が第1方向D1乃至第4方向D4に沿って延在した、N+型層1B−P型層33−N+型層32−P型層31−N+型層1Aの構造を有する。

(もっと読む)

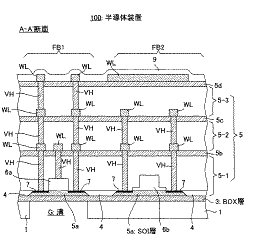

半導体集積回路装置

【課題】順方向基板バイアスを印加する場合に、動作温度の上昇にともなうリーク電流の増加を防止する。

【解決手段】順バイアス制御回路FBBが出力するバイアス信号は電流クランプ回路CLMPを通してCMOS回路LSIの基板へ供給される。電流クランプ回路CLMPは不純物濃度の低い拡散層を利用して構成され、温度変化に対して不変な定電流を供給する。

【効果】CMOS回路の低電圧駆動時、動作速度を順バイアスにより向上するとともに、温度上昇時、順バイアス印加にともなうリーク電流の増加を抑制し、高速かつ高信頼性を持った半導体集積回路装置を実現する。

(もっと読む)

半導体装置

【課題】 半導体基板上のパターン密度の疎密によるトランジスタ特性のばらつきを抑制する。

【解決手段】 半導体基板1上の正規のPoly−R12等の回路素子に加えて、回路素子のパターン密度が均一になるように、半導体チップ内のほぼ全面にわたって、ダミーの機能素子となるPoly−R12aのパターンを配置する。さらに、このダミー用のPoly−R12aを、アルミ被りによる抵抗値の変動を抑制するためにLP−SiN膜17に覆われた構造とし、アルミ配線による抵抗値の変動を抑えるとともに、パターン密度の疎密による抵抗値、トランジスタ特性の変動を低減する。これにより、パターン密度の疎密によるトランジスタ特性のばらつきをなくし、さらに、アルミ被りによるPoly−Rへの影響や、赤外線吸収の素子疎密によるウェーハ内温度差を抑制する。

(もっと読む)

1,641 - 1,648 / 1,648

[ Back to top ]