Fターム[5F048BG06]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 絶縁体分離 (5,896) | 素子領域側面・底面を絶縁物で分離するもの (666) | 複数MOS(CMOS)で一部のみ (116)

Fターム[5F048BG06]に分類される特許

61 - 80 / 116

半導体集積回路

【課題】動作モードに応じて速度、電力消費をコントロール可能とし、さらにリテンション特性を改善する。

【解決手段】半導体集積回路(1)は、シリコン基板(2)上に混載されたメモリ(4)と論理回路(5)を有する。メモリは、UTB(3)上に形成されたSOI構造を有する部分空乏型のnMOS(6)を含む。部分空乏型のnMOSは、UTBの下に、ゲート端子とは独立に電圧が印加可能にされたバックゲート領域(14)を有する。論理回路は、UTB上に形成されたSOI構造を有する完全空乏型のnMOS(7)とpMOS(8)を含む。完全空乏型のnMOSとpMOSは、UTBの下に、ゲート端子とは独立に電圧が印加可能にされたバックゲート領域(14,22)を有する。

(もっと読む)

半導体装置

【課題】部分分離領域によって素子分離された素子形成領域におけるボディ領域の電位を安定性の良く固定できるSOI構造の半導体装置を得る。

【解決手段】部分酸化膜31によって素子分離された素子形成領域に、ソース領域51、ドレイン領域61及びHゲート電極71からなるMOSトランジスタを形成する。Hゲート電極71は左右(図中は上下)の“I”によって、ソース領域51及びドレイン領域61にゲート幅W方向に隣接して形成されるボディー領域13とドレイン領域61及びソース領域51とを電気的に分離し、中央の“−”が本来のMOSトランジスタのゲート電極として機能する。

(もっと読む)

絶縁ゲート型電界効果型トランジスタ及び半導体装置

【課題】 本発明は、歪みSOIトランジスタのチャネルにシリコンゲルマニウム層が接することに起因する短チャネル特性の悪化を回避する。更には、歪みSOIトランジスタのダブルゲート化や通常のシリコンないしはSOIトランジスタとの同一ウェハ上への混載を実現する。

【解決手段】 本願発明は、例えば、歪み緩和シリコンゲルマニウム層上に歪みシリコン層を成長させ、しかるのちに部分的にシリコンゲルマニウム層を除去することによって、歪みシリコン層によってチャネル層を構成する。

(もっと読む)

半導体装置

【課題】印加されたサージによって破壊されることをより抑制することのできる半導体装置を提供する。

【解決手段】半導体装置1は、薄膜SOI基板10の薄膜SOI層40に、入力保護用のダイオード5を有する。そして、このダイオード5を構成する高濃度P型領域41に電気的に接続された電極50aと、同じくダイオード5を構成する高濃度N型領域42に電気的に接続された電極50bとのいずれか一方を介して印加されたサージが、これら両電極50a及び50bのうちの他方の電極に向けて薄膜SOI層40の内部を流れることに起因して該薄膜SOI層40で発生する熱を、熱吸収部材60の相変化を通じて吸収する。

(もっと読む)

正孔移動度を向上させる方法

【課題】 正孔移動度を向上させるためのデバイス、方法を提供する。

【解決手段】 第1のシリコン層の上の酸化物層と、酸化物層の上の第2のシリコン層とを含み、酸化物層が第1のシリコン層と第2のシリコン層との間にある半導体デバイスが提供される。第1のシリコン層210及び第2のシリコン層230は、同一の結晶配向を含む。デバイスは、第1のシリコン層の上の傾斜ゲルマニウム層250をさらに含み、傾斜ゲルマニウム層は、スペーサ240及び第1のシリコン層に接し、酸化物層220には接しない。傾斜ゲルマニウム層の下部は、傾斜ゲルマニウム層の上部より高濃度のゲルマニウムを含み、傾斜ゲルマニウム層の上面にはゲルマニウムが存在しない。

(もっと読む)

半導体装置およびその製造方法

【課題】高耐圧トランジスタと、低耐圧トランジスタとを同一基板に備える半導体装置であって、特に高耐圧トランジスタ領域の面積の削減を図り、半導体装置の全体の小型化を実現することができる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、支持基板10aと、前記支持基板10a上に形成された絶縁層10bと、前記絶縁層10b上に形成された第1半導体層と、前記第1半導体層内に形成された第1高耐圧トランジスタ100Pと、前記絶縁層10b上に形成された第2半導体層10cと、前記第2半導体層内に形成された第2高耐圧トランジスタ100Nと、前記第1半導体層と前記第2半導体層との間に設けられた第1素子分離領域110aであって、第1素子分離領域110aは、デュアルトレンチ構造を有するトレンチ絶縁層20aからなる。

(もっと読む)

半導体装置及びその製造方法

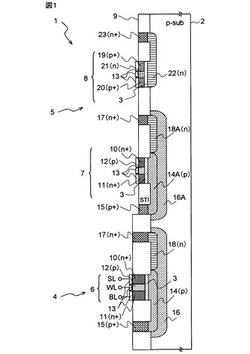

【課題】本発明は、高速・低消費電力で、且つ高集積化できる構成を有する半導体装置を提供することを目的とする。

【解決手段】本発明は、シリコン基板上にBOX層9及びSOI層10が積層されたSOI基板に形成される半導体装置である。そして、本発明は、SOI層10に形成されたボディ領域8にゲート電極3が巻きついたFIN型のトランジスタと、素子分離に部分分離と完全分離を併用して分離され、SOI層10に形成されたプレーナ型のトランジスタとを備える。

(もっと読む)

表示装置の製造方法

【課題】品質を損なうことなく半導体デバイスを基板に搭載でき、且つ、製造効率の良好な表示装置の製造方法を提供する。

【解決手段】表示装置10の製造方法は、半導体デバイス21を位置決め治具40の所定位置に剥離性粘着材32によって仮固定するステップと、半導体デバイス21を仮固定した位置決め治具40と半導体デバイス搭載用基板50とを、半導体デバイス21が半導体デバイス搭載用基板50の所定位置に対向するように位置合わせするステップと、位置合わせした位置決め治具40及び半導体デバイス搭載用基板50のいずれか一方を他方によって押圧することにより、半導体デバイス21を半導体デバイス搭載用基板50の所定位置に接着するステップと、半導体デバイス搭載用基板50の所定位置に接着した半導体デバイス21を、位置決め治具40から取り外すステップと、を備える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】従来の低消費電力のSOIデバイスと、高耐圧のトランジスタとを同一のSOI基板上に形成した半導体装置およびその製造方法を提供する。

【解決手段】シリコン基板層と、シリコン基板層の上に形成された絶縁層と、絶縁層上に形成された半導体層と、を含むSOI基板を用意し、SOI基板のシリコン基板層内に自身の動作活性領域を有する少なくとも1つの第1のトランジスタと、SOI基板の半導体層内に自身の動作活性領域を有する少なくとも1つの第2のトランジスタを形成する。

(もっと読む)

薄膜トランジスタアレイ基板の製造方法

【課題】信頼性が向上された薄膜トランジスタアレイ基板の製造方法を提供する。

【解決手段】基板101上全面にバッファー膜110を形成し、第1及び第2薄膜トランジスタの半導体層、及びストレージキャパシタ下部電極パターン形成し、第1イオンを注入し、第1及び第2薄膜トランジスタの半導体層をチャネルドーピングすると共にストレージキャパシタ下部電極134を形成し、ゲート絶縁膜112を全面形成し、第1及び第2薄膜トランジスタのゲート電極113、123、及びストレージキャパシタ上部電極133を形成し、第2イオンを注入し、第2薄膜トランジスタのソース領域124a及びドレイン領域124cを形成し、第3イオンを注入し、第1薄膜トランジスタのソース領域114a及びドレイン領域114cを形成し、第2薄膜トランジスタのゲート電極123をマスクとして第4イオンを注入し、第2薄膜トランジスタのLDD領域124dを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI領域とバルク領域との間でのクロストークノイズを低減しつつ、結晶欠陥

の発生を防止できるようにした半導体装置及びその製造方法を提供する。

【解決手段】SOI領域とバルク領域とを半導体基板1に有する半導体装置であって、S

OI領域に形成されたLV−MOSFET100と、バルク領域に形成されたHV−MO

SFET200との間が素子分離層300によって隔てられており、素子分離層300の

SOI領域側はトレンチ構造を有し、素子分離層300のバルク領域側がLOCOS構造

を有する。このような構成であれば、LV−MOSFET100とHV−MOSFET2

00との間の素子分離をトレンチ構造のみで行う場合と比べて、クロストークノイズを低

減しつつ、素子分離層300のトレンチ構造を浅くすることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】特性のばらつきおよび分離リークを適切に防ぐことができる半導体装置およびその製造方法を提供する。

【解決手段】I/Oトランジスタは、コアトランジスタに比較して、高い電源電圧で駆動されるので、動作に伴い生じたキャリアがボディ領域に溜まることにより、特性のばらつきが生じやすい。従って、I/OトランジスタのPTI下ウェル領域における不純物濃度を高くすることにより、PTI下ウェル抵抗を低減し特性のばらつきを防ぐ。一方、I/Oトランジスタは、コアトランジスタに比較して、分離リーク特性に対する要求が厳しいので、PTI下ウェル領域における不純物濃度を低くすることにより、分離リークを防ぐ。

(もっと読む)

半導体装置

【課題】回路ブロック間でのノイズによる干渉を抑制しつつ、バルク構造とSOI構造とを同一基板上に混載できるようにする。

【解決手段】絶縁層103上に半導体層5が積層されてなるSOI領域と、下地が基板のみからなるバルク領域とを同一の半導体基板101に備え、バルク領域に形成されたバルクトランジスタ10と、SOI領域に形成されたSOIトランジスタ20との間の半導体基板101に電位固定用の不純物拡散層91を備える。このような構成であれば、バルクトランジスタ10と、SOIトランジスタ20との間で生じる電気力線を不純物拡散層91で遮断することができ、バルクトランジスタ10とSOIトランジスタ20との間でのクロストークノイズを抑制することができる。

(もっと読む)

半導体装置

【課題】キンクの発生や、動作耐圧の低下を防止するとともに、動作特性にばらつきを生じないSOI基板上に形成される半導体装置を提供する。

【解決手段】ゲート電極5は、そのゲート幅方向の両端部が活性領域から平面視的に突出するように配設されている。そして、当該両端部の下部に対応するSOI基板SBの表面内には部分トレンチ分離絶縁膜8が配設され、ゲート電極5のゲート幅方向両端部外方のSOI基板SBの表面内には、それぞれ部分トレンチ分離絶縁膜8に隣接してボディコンタクト領域21が配設されている。ボディコンタクト領域21とボディ領域とは、部分トレンチ分離絶縁膜8下のSOI層(ウエル領域)を介して電気的に繋がる。また、ソース領域31の表面内には、ゲート電極5のゲート幅方向のほぼ中央部近傍に、P型の不純物が比較的高濃度に導入されたソースタイ領域4が配設されている。

(もっと読む)

半導体集積回路装置

【課題】SOI基板上に配設され、入出力回路部の電源電圧がコア回路部の電源電圧よりも高い半導体集積回路装置において、入出力回路部を構成するMOSトランジスタの基板浮遊効果に起因する特性低下を防止した半導体集積回路装置を提供する。

【解決手段】トランジスタP11のフィンガー長a1は、トランジスタP1のフィンガー長A1よりも長く、トランジスタN11のフィンガー長b1は、トランジスタN1のフィンガー長B1よりも長い。トランジスタN11のフィンガー長b1は、トランジスタP1のフィンガー長A1よりも短く、a1>A1>b1>B1となっている。I/O部101とロジック回路部102との関係においては、同じ導電型のMOSトランジスタでは、ロジック回路部102を構成するMOSトランジスタのフィンガー長の方が、I/O部101を構成するMOSトランジスタのフィンガー長よりも長くなるように設定されている。

(もっと読む)

半導体基板および半導体装置

【課題】コストの上昇や、信頼性の低下を招かずにSOI構造を形成することと同様の効果を有する半導体基板及び半導体装置を提供する。

【解決手段】半導体からなる半導体基板であって、内部に空洞を有し、かつ前記空洞の内部に前記半導体からなる柱が存在し、前記空洞上の半導体基板の厚さをt、前記柱から最も近い前記半導体からなる領域と前記柱との間の距離をw、前記半導体のヤング率をE(N/μm2 )、前記空洞上の前記半導体基板にかかる荷重をP(N/μm2 )とした場合に、w≦t(E/0.0568P)1/4の条件を満たすことを特徴とする。

(もっと読む)

高耐圧半導体集積回路装置

【課題】SOI基板のトレンチ内の両端に形成された側面酸化膜に対して均等に電圧が加わる構成の集積回路装置を提供すること。

【解決手段】本発明の半導体集積回路装置は、素子形成領域下に第1の絶縁膜を有する基板と、前記第1の絶縁膜に達するように前記素子領域に形成されるシリコンのトレンチと、前記トレンチの側壁に形成される第2の絶縁膜と、前記トレンチに埋め込んだ多結晶シリコン上に形成される第3の絶縁膜とを具備し、第3の絶縁膜の膜厚を第1の絶縁膜の膜厚で除した値を特定の範囲にすることにより、トレンチ内の両端に形成された酸化絶縁膜に対して均等に電圧が加わる。

(もっと読む)

集積回路およびその形成方法(標準的直交回路のためのハイブリッド配向構造)

【課題】 標準的直交回路のためのハイブリッド配向構造のためのデバイス及び方法を提供する。

【解決手段】 本発明の実施形態の集積回路は、第1結晶配向を有する第1領域及び第2結晶配向を有する第2領域を含むハイブリッド配向基板(600)を備える。第1領域の第1結晶配向は、第2領域の第2結晶配向に平行でも垂直でもない。集積回路は、第1領域上の第1型デバイス(620)及び第2領域上の第2型デバイス(630)をさらに備え、ここで第1型デバイス(620)は、第2型デバイス(630)に平行又は垂直であり、第1型デバイス(620)は、互いに直交する第1電流(621)及び第2電流(622)を含み、第1(621)及び第2(622)電流のキャリア移動度は互いに等しい。具体的には、第1型デバイスはp型電界効果トランジスタ(PFET)を含み、第2型デバイスはn型電界効果トランジスタ(NFET)を含む。

(もっと読む)

半導体素子の製造方法及び半導体素子

【課題】SBSI法によりSOIトランジスタを形成する場合に、支持体の側面開口部と平行な向きからのイオン注入に対しては支持体によりSOIトランジスタのチャネル領域がマスクされてしまうため斜めイオン注入を行っても不純物イオンはSOIトランジスタのチャネル領域には到達しない。そのため、例えばチャネル幅を広くとれる構造として、SOIトランジスタのチャネルの方向と支持体とを平行に配置した場合、寄生トランジスタの影響を抑制することが困難となり、SOIトランジスタのリーク電流が大きくなってしまうという問題点があった。

【解決手段】SOIトランジスタのチャネル部周縁部を開口し、中央部へのイオン注入を防ぐための第1不純物添加阻止層を形成した後イオン注入法を用いてチャネル部周縁部に生じる寄生トランジスタの閾値を上昇させて寄生トランジスタ起因のリーク電流を抑制する。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】SOI構造とバルク構造とが混載された半導体基板上に形成された半導体装置を、チップサイズを増大させずに得る。

【解決手段】半導体基板10を所定の深さまでエッチングして得られた第1の領域にエピタキシャル成長にて形成され、半導体基板10の底面からの高さが半導体基板10の表面の高さと実質的に同一である半導体層60と、半導体基板10と半導体層60との間に埋め込まれた埋め込み絶縁層240と、半導体層60内の各々の素子領域間、及び、半導体層60と半導体基板10との間、を水平面内で素子分離する素子分離体と、を有する半導体基板10上に形成された半導体装置。

(もっと読む)

61 - 80 / 116

[ Back to top ]