Fターム[5F048CC08]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 保護回路の構成 (4,292) | MOS (642)

Fターム[5F048CC08]の下位に属するFターム

2以上のMOS (303)

Fターム[5F048CC08]に分類される特許

1 - 20 / 339

ESD保護回路およびこれを備えた半導体装置

半導体装置

【課題】 過電流検出による保護と、温度検出による保護とを、好適に行うことが可能な半導体装置を提供する。

【解決手段】 半導体基板を有する半導体装置であって、半導体基板が、メイン素子領域と、メイン素子領域よりも小さい電流が流れるサブ素子領域を有しており、サブ素子領域が、半導体基板を平面視したときに半導体基板の中心と重なる位置に形成されており、半導体基板上であって、半導体基板を平面視したときにサブ素子領域と重なる位置に、温度検出素子が形成されている。

(もっと読む)

半導体集積回路装置

【課題】半導体集積回路装置において、I/Oセルの高さを低減すると同時に幅の増大を防ぐことでI/Oセルの占める領域の面積を削減すること。

【解決手段】レベルシフタ回路、I/Oロジック回路およびI/Oバッファ回路を含むI/Oセルがコア領域の周囲に配置された半導体集積回路装置であって、I/Oロジック回路が配置されたI/Oロジック領域、および、I/Oバッファ回路が配置されたI/Oバッファ領域は、I/Oセルに対するパッドが配置された領域と重なり合うとともに、コア領域の辺に平行な方向に互いに並んで配置されている。

(もっと読む)

半導体装置

【課題】信頼性に優れた半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、入力電圧ラインと誘導性負荷との間に接続される第1のスイッチング素子と、誘導性負荷と基準電圧ラインとの間に並列接続される第2のスイッチング素子とを備えている。0<(第2のスイッチング素子の閾値電圧)<(第2のスイッチング素子の内蔵ダイオードのオン電圧)である。第2のスイッチング素子のゲート電圧が基準電位の場合に、第1のスイッチング素子と第2のスイッチング素子との接続点の電位が、−(第2のスイッチング素子の閾値電圧)より大きくなると第2のスイッチング素子はオフし、接続点の電位が、−(第2のスイッチング素子の閾値電圧)より小さくなると第2のスイッチング素子はオンする。

(もっと読む)

静電気検出回路

【課題】本発明は、静電気検出回路を提供することを目的とする。

【解決手段】本発明の静電気検出回路は、電源線と接地線との間に直列に接続されているレジスター及びスイッチユニットを備え、前記電源線に静電気が存在する場合、前記スイッチユニットはオンされて、前記レジスターの両端に検出電圧が生じ、前記検出電圧は、静電気保護回路を動作させて静電気を除去するか、又は制御回路を動作させてデータを保存する。

(もっと読む)

半導体装置

【課題】静電気放電が印加されたときの熱破壊を抑制すること。

【解決手段】半導体装置1の半導体活性層16には、n型領域23とp型領域26とn型の埋込み領域30が形成されている。n型領域23は、カソード電極Kに電気的に接続している。p型領域26は、アノード電極Aに電気的に接続している。埋込み領域30は、半導体活性層16のうちのp型領域26の裏面側の少なくも一部を含むように形成されており、p型領域26の裏面に接触しているとともに、不純物濃度が半導体活性層16の不純物濃度よりも濃い。

(もっと読む)

半導体装置

【課題】低消費電力化及び回路面積の削減を図れるようにした半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、電源端子と接地端子の間に接続されたMOSトランジスタと、MOSトランジスタのドレインとゲートの間に接続された第1のダイオードと、MOSトランジスタのドレインとゲートの間に第1のダイオードと互いの順方向が逆向きに直列に接続された第2のダイオードと、MOSトランジスタのドレインとゲートの間に第1及び第2のダイオードと直列に接続されたキャパシタとを備えている。

(もっと読む)

半導体集積回路

【課題】保護素子とガードリング領域との間のウィークスポットが破壊される危険性を軽減する。

【解決手段】半導体集積回路は、静電保護回路の保護素子Mn2を形成するために、第1導電型の半導体領域P−Wellと第2導電型の第1不純物領域Nと第1導電型の第2不純物領域Pにより形成されたガードリングGrd_Rngを具備する。第1不純物領域Nは、長辺と短辺を有する長方形の平面構造として半導体領域の内部に形成される。ガードリングは、第1不純物領域Nの周辺を取り囲んで半導体領域の内部に形成される。第1不純物領域Nの長方形の平面構造の短辺には、ウィークスポットWk_SPが形成される。長方形の長辺と対向するガードリングの第1部分では、複数の電気的コンタクトが形成される。長方形の短辺に形成されるウィークスポットと対向するガードリングの第2部分では、複数の電気的コンタクトの形成が省略される。

(もっと読む)

半導体装置

【課題】異なる電源系統を含む半導体装置において、静電気による破壊から出力回路を保護する保護素子を備えた半導体装置の提供。

【解決手段】半導体装置は、第1の電源電圧と第1の接地電圧からなる第1の電源系統と、第2の電源電圧と第2の接地電圧からなる第2の電源系統と、第2の電源系統から電源供給を受ける出力回路と、第1の電源系統から電源供給を受け、出力回路を駆動する信号を出力する第1の駆動回路と、第1の接地電圧と第2の接地電圧との間に接続された第1の保護回路と、一端が、出力回路の出力ノードに接続され、他の一端が、第1の接地電圧に接続されている第1の保護素子と、を備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】高耐圧トランジスタの低濃度不純物拡散層がコンタミネーションから保護されて、半導体装置の特性を安定化できるようにする。

【解決手段】基板1の上に、ゲート絶縁膜3a及びゲート電極4aを順次形成し、ゲート電極4aをマスクとして基板1に不純物注入を行うことにより、基板1の上部におけるゲート電極4aの側方に低濃度不純物拡散層5aを形成する。続いて、ゲート電極4aの上から該ゲート電極4aの側方を通って低濃度不純物拡散層5aの上の一部までを連続して覆うように不純物拡散抑制膜7aを形成する。続いて、ゲート電極4a及び不純物拡散抑制膜7aをマスクとして基板1に不純物注入を行うことにより、基板1の上部におけるゲート電極4aの側方に、低濃度不純物拡散層5aよりも不純物濃度が高い高濃度不純物拡散層8aを形成する。その後に、不純物拡散抑制膜7aを残存させた状態で基板1に対して加熱処理を行う。

(もっと読む)

窒化物半導体装置

【課題】ダイオード等の保護素子の外付けによる部品点数の増加及び占有面積の増大を抑えた、双方向に高いアバランシュエネルギー耐量を有する窒化物半導体装置を提供する。

【解決手段】半導体基板10は、第1のn型領域12A、第2のn型領域12Bとともにトランジスタ11を構成する。半導体基板10の裏面には、裏面電極13が接合され、また、半導体基板10の上には、HFET21が形成されている。HFET21は、AlGaN層23A及びGaN層23Bを備える半導体層積層体23と、第1のオーミック電極24A、第2のオーミック電極24B、第1のゲート電極25A、第2のゲート電極25Bにより構成されている。第1のオーミック電極24Aと第1のn型領域12A、第2のオーミック電極24Bと第2のn型領域12Bはそれぞれ電気的に接続されている。

(もっと読む)

半導体装置

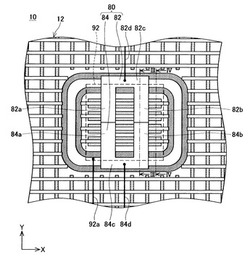

【課題】半導体装置の信頼性を向上させる。

【解決手段】スイッチング用のパワーMOSFETと、そのパワーMOSFETよりも小面積でかつそのパワーMOSFETに流れる電流を検知するためのセンスMOSFETとが1つの半導体チップCPH内に形成され、この半導体チップCPHはチップ搭載部上に導電性の接合材を介して搭載され、樹脂封止されている。半導体チップCPHの主面において、センスMOSFETが形成されたセンスMOS領域RG2は、センスMOSのソース用のパッドPDHS4よりも内側にある。また、半導体チップCPHの主面において、センスMOS領域RG2は、パワーMOSFETが形成された領域に囲まれている。

(もっと読む)

半導体装置

【課題】横型IGBTのコレクタ領域側にPN接合によりアバランシェダイオードをさらに設けることにより、ESD保護回路の面積および製造コストを減少させ、かつ、直流電流が重畳した場合にも素子破壊を防止するESD保護回路を含む半導体装置を提供する。

【解決手段】外部電圧を受ける第1のノードと、接地電圧を受ける第2のノードと、第1および第2のノードの間に並列に接続される保護回路および被保護素子を備え、保護回路は、エミッタが第2のノードに接続される横型IGBTと、アノードが横型IGBTのコレクタに接続され、カソードが第1のノードに接続されるアバランシェダイオードと、第1および第2のノードの間に接続され、横型IGBTのゲートに接続されるクランプ駆動回路とを含む。

(もっと読む)

金属酸化物半導体出力回路およびそれを形成する方法

【課題】金属酸化物半導体(MOS)出力回路とその形成方法の提供。

【解決手段】第一パッド61と、ゲート、第一の供給電圧に電気的接続のソース、ドレインを含む基板で第一型の第一MOSトランジスタ62と、ゲート、制御信号を受信する構成のソース、第一MOSトランジスタのゲートに電気的接続のドレイン、本体を含む基板で第一型と反対の第二型の第二MOSトランジスタ65と、バイアス信号を受信する構成のゲート、第二供給電圧に電気的接続のドレイン、第二MOSトランジスタのソースに電気的接続のソース、第一参照電圧に電気的接続の本体を含む基板で第一型の第三MOSトランジスタ66とを含み、第二MOSトランジスタの本体は第三MOSトランジスタのソースに電気的接続、一時的な信号イベントの第一パッド上の受信の場合、第二MOSトランジスタのドレインから第二供給電圧まで第二MOSトランジスタの本体を流れる電流を妨げる集積回路。

(もっと読む)

信号伝達装置および撮像表示システム

【課題】静電気からの保護をより確実に行うことが可能な信号伝達装置等を提供する。

【解決手段】信号伝達装置は、信号の入力動作および出力動作のうちの少なくとも一方の動作を行う複数の画素と、画素に接続された1または複数の信号線を含む複数の配線と、複数の配線のうちの一の信号線と他の一の配線との間に配設され、第1トランジスタおよび容量素子を有する1または複数の静電気保護回路と、静電気保護回路に接続された第1制御線とを備えている。静電気保護回路では、第1トランジスタのゲートが、第1制御線と直接もしくは間接的に接続され、第1トランジスタにおけるソースおよびドレインのうちの一方が、一の信号線および容量素子の一端に接続されると共に、他方が他の一の配線に接続され、容量素子の他端が、第1トランジスタのゲートに接続されている。

(もっと読む)

半導体装置、半導体パッケージ、および半導体装置の製造方法

【課題】信頼性の高い半導体装置を提供する。

【解決手段】N型基板10と、N型基板10の一面側に設けられたP型ウェル40と、P型ウェル40に設けられたP型高濃度不純物領域42と、P型ウェル40に設けられたN型のソース・ドレイン領域を有するMOSトランジスタ20と、N型基板10の一面側に設けられ、かつ一方がP型高濃度不純物領域42と電気的に接続し、他方が接地されているソース・ドレイン領域を有するMOSトランジスタ30と、を備える。

(もっと読む)

保護回路

【課題】低圧回路10を保護しつつ、かつ、低圧回路10の動作を継続させる保護回路100を提供する。

【解決手段】PチャネルMOSトランジスタMP1は入力電源Vinと低圧回路10との間に設けられている。第1ツェナーダイオードZ1のカソードは、入力電源VinとPチャネルMOSトランジスタMP1のソースとの間に接続されている。第1ツェナーダイオードZ1のアノードは、分岐ノードN1で分岐され、一方は抵抗R1を介して接地されている。分岐ノードN1で分岐された他方は、PチャネルMOSトランジスタMP1のゲートに接続されている。第2ツェナーダイオードZ2のカソードは、低圧回路10とチャネルMOSトランジスタMP1のドレインとの間に接続されている。第2ツェナーダイオードZ2のアノードは、接地されている。

(もっと読む)

ガードバンドセル及びガードバンド

【課題】電源供給が遮断されるIO領域が存在する場合でも、ランダムロジック領域内でのラッチアップの発生を防止するガードバンドセル及びガードバンドを提供すること。

【解決手段】本発明の一態様に係るガードバンドセル11は、NウェルNW1を有する。また、本発明の一態様に係るガードバンドセル11は、NウェルNW1の上に形成された、Nウェル層と同じ導電型であるN型ガードバンド拡散層NGB1を有する。N型ガードバンド拡散層NGB1は、十分な低抵抗の配線により、ランダムロジック領域2の電源電位と接続される。

(もっと読む)

半導体装置及びDC−DCコンバータ

【課題】耐久性が高い半導体装置及びDC−DCコンバータを提供する。

【解決手段】実施形態に係る半導体装置は、高電位側電源電位に接続するための第1の配線と、前記高電位側電源電位に接続するための、前記第1の配線とは別の第2の配線と、前記第1の配線に一端が接続され、他端が出力端子に接続されるスイッチングトランジスタと、前記高電位側電源電位と前記低電位側電源電位との間で前記スイッチングトランジスタと並列に接続される保護素子とを備える。前記保護素子は、前記第1の配線に接続される、第1のp形半導体領域と、前記第2の配線に接続される、前記第1のp形半導体領域に接したn形半導体領域と、前記n形半導体領域に接し、前記第1のp形半導体領域から離隔し、前記低電位側電源電位に接続するための配線に接続される第2のp形半導体領域と、を有する。

(もっと読む)

過電流保護回路

【課題】入力電源電圧の動作保証範囲が大きいとしても当該電圧変動の影響を抑制して正常に過電流保護を図るようにした過電流保護回路を提供する。

【解決手段】支持基板10が第1半導体層11および第2半導体層12を絶縁層13で挟んで構成されている。第1半導体層11上には絶縁膜14を介してフィールドプレート抵抗膜20が形成されている。可変電流源ISが、ゲート電極19からドレイン電極17にかけて絶縁膜14上に沿って形成されたフィールドプレート抵抗膜20(フィールドプレート抵抗R1およびR2)に生じるノードN1の電圧に応じて出力電流値を変更してセンス抵抗Rsの検出電圧V2を補正する。

(もっと読む)

1 - 20 / 339

[ Back to top ]