Fターム[5F048DA00]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 製造方法 (5,886)

Fターム[5F048DA00]の下位に属するFターム

1MOSソース・ドレインとの同時形成 (180)

2以上の要素の同時形成(ソース、ドレインを除く) (166)

イオン注入時ゲート保護層(最外レジストを除く) (203)

ゲート側壁(サイドウォール) (5,329)

Fターム[5F048DA00]に分類される特許

1 - 8 / 8

歪み材料を有する半導体デバイス

歪み材料を有する半導体デバイスが開示される。特定の実施形態では、半導体デバイスは、第1ドレインと第1ソースとの間に第1ゲートを含む第1セルを含む。半導体デバイスはまた、第1セルに隣接する第2セルを含む。第2セルは、第2ドレインと第2ソースとの間に第2ゲートを含む。半導体デバイスはさらに、第1ソースと第2ソースとの間にシャロートレンチ分離領域を含む。第1ソースおよび第2ソース上の第1量の歪み材料は、第1ドレインおよび第2ドレイン上の第2量の歪み材料より多い。  (もっと読む)

(もっと読む)

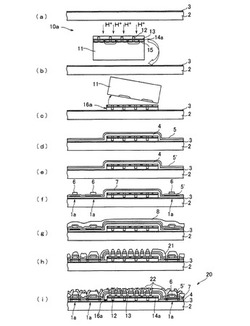

半導体装置の製造方法

【課題】非単結晶Si薄膜と単結晶Si薄膜デバイスとを形成し、高性能なシステムを集積化した半導体装置の製造方法を提供する。

【解決手段】絶縁基板2上に、単結晶Si薄膜トランジスタ16aと非単結晶Si薄膜トランジスタ1aとが形成された半導体装置20の製造方法において、表面に酸化膜、ゲートパターン、不純物イオン注入部が形成された後に平坦化されており、所定の深さに所定の濃度の水素イオンが注入された水素イオン注入部15を備えた単結晶Si基板10aを熱処理によって絶縁基板2上に接合し、さらに水素イオン注入部15において熱処理により劈開剥離した後、非晶質Si薄膜5を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 フルシリサイド化したデュアルゲート構造を有する半導体装置において、ゲート電極の安定性を高めることによって半導体装置の信頼性を向上させる。

【解決手段】 N型MISトランジスタ形成領域のゲート電極となるNiSi膜110Aを形成すると共にP型MISトランジスタ形成領域のゲート電極となるNi3 Si膜110Bを形成する。素子分離領域101上つまりシリサイド化防止膜106の下には、未反応のN型多結晶シリコン膜103Aが、NiSi膜110AとNi3 Si膜110Bとの間の相互拡散を防止する導電性拡散防止領域として残存する。

(もっと読む)

半導体装置の製造方法

【課題】

しきい値電圧調整のためのイオン注入工程や半導体ウェハ表面に付着した異物を除去するための純水リンス処理を省略することなく、ゲート酸化膜の絶縁破壊耐圧の歩溜りの低下やゲート酸化膜の信頼性の低下といった不具合を改善する。

【解決手段】

レジストマスク14を形成してイオン注入を行なった後、レジストマスク14を除去して半導体ウェハ2表面に対して少なくとも純水リンスを含む洗浄処理を行なう。洗浄処理後、半導体ウェハに対して熱処理を施して、純水リンスの際の静電破壊によって劣化したゲート酸化膜10,12を回復させる。

(もっと読む)

半導体装置およびその製造方法

【課題】 p型MOSトランジスタおよびn型MOSトランジスタのオン電流を共に増加可能とすると共に、コンタクトの不良発生を防止する半導体装置およびその製造方法を提供する。

【解決手段】 シリコン基板11の第1領域13pに形成されたp型MOSトランジスタ14と、第2領域13nに形成されたn型MOSトランジスタ15と、第2領域13nには、シリコン基板11および素子分離領域12の一部の表面とゲート積層体34を覆う引っ張り応力を有する第2応力制御膜38と、第1領域13pのシリコン基板11および素子分離領域12の一部の表面とゲート積層体23を覆うと共に、第2領域の第2応力制御膜38を覆う、圧縮応力を有する第1応力制御膜26が形成される。第1応力制御膜26の膜厚t1、圧縮応力の大きさP1、第2応力制御膜38の膜厚t2、圧縮応力の大きさP2として、t1×P1<t2×P2の関係を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】 多電源のMOSトランジスタが搭載された半導体装置においてホットキャリアに対する信頼性とNBTIに対する信頼性とを両立させる。

【解決手段】 高耐圧用のnチャネル型MOSトランジスタの第1のゲート絶縁膜(厚いゲート絶縁膜)は、半導体基板との界面に窒素濃度ピークを有する。高耐圧用のpチャネル型MOSトランジスタの第2のゲート絶縁膜(厚いゲート絶縁膜)、高速駆動用のnチャネル型MOSトランジスタの第3のゲート絶縁膜(薄いゲート絶縁膜)及び高速駆動用のpチャネル型MOSトランジスタの第4のゲート絶縁膜(薄いゲート絶縁膜)はそれぞれ、対応するゲート電極の近傍のみに窒素濃度ピークを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】 High−k膜を用い電気的膜厚の異なるゲート絶縁膜を同じ半導体基板表面に高い再現性の下に高精度にしかも簡便に形成する。

【解決手段】 シリコン基板1のnウェル層2表面部が素子分離領域3で区画され、周辺回路部のMISFETでは、膜厚4〜6nmのベース酸化膜4およびその改質層である窒化層4a、High−k膜5およびその改質層である窒化層5aの積層膜で成る第1ゲート絶縁膜6が形成され、内部回路部のMISFETでは、膜厚1nm程度の下地膜12およびその改質層である窒化層12a、上記High−k膜5およびその改質層である窒化層5aの積層膜で成る第2ゲート絶縁膜13が形成される。High−k膜5は、HfSiOx、ZrSiOx、HfAlOxあるいはZrAlOxの絶縁膜が好適となる。

(もっと読む)

半導体装置の製造方法

【課題】

しきい値電圧調整のためのイオン注入工程や半導体ウェハ表面に付着した異物を除去するための純水リンス処理を省略することなく、ゲート酸化膜の絶縁破壊耐圧の歩溜りの低下やゲート酸化膜の信頼性の低下といった不具合を改善する。

【解決手段】

シリコン基板2の表面にゲート酸化膜を形成する際や、レジストマスクを除去した後などは、シリコン基板2の表面の清浄化を行なう。シリコン基板2の清浄化は、純水リンス処理と各種洗浄液を用いた洗浄とを組み合わせて行なわれるが、特に、シリコン基板2の表面にゲート酸化膜が形成され、ゲート酸化膜が表面に露出した状態である場合では、シリコン基板2の表面に純水リンス処理を施した後の洗浄では洗浄液としてフッ酸を含む溶液を用いない。

(もっと読む)

1 - 8 / 8

[ Back to top ]