Fターム[5F048DA01]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 製造方法 (5,886) | 1MOSソース・ドレインとの同時形成 (180)

Fターム[5F048DA01]の下位に属するFターム

2MOSのガードリング (2)

2MOSのチャネルストッパ (9)

1又は2MOSのゲート(多結晶Si) (37)

2MOSのウェル (21)

バイポーラのコレクタ (26)

バイポーラのベース (28)

バイポーラのエミッタ (41)

Fターム[5F048DA01]に分類される特許

1 - 16 / 16

拡散抵抗素子およびその製造方法

【課題】ノイズおよび抵抗バラツキが小さな拡散抵抗の製造方法を提供することを目的とする。

【解決手段】半導体基板の表面付近にp型拡散層114を形成する工程と、拡散抵抗体となるp型拡散層114の第1領域の表面上に、層間絶縁膜とは異なる絶縁膜であって当該第1領域の表面を保護するカバー膜125を形成する工程と、カバー膜125を形成する工程の後、カバー膜125の前記第1領域に接する第2領域に前記第1領域よりも高い濃度で拡散抵抗体のコンタクト部となるp型拡散層116を形成する工程とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの耐圧を向上し得る半導体装置及びその製造方法を提供することにある。

【解決手段】半導体基板10内に形成された第1導電型の第1の不純物領域32、46と、半導体基板内に形成され、第1の不純物領域に隣接する第2導電型の第2の不純物領域34、48と、第2の不純物領域内に形成された第1導電型のソース領域30a、44aと、第1の不純物領域内に形成された第1導電型のドレイン領域30b、44bと、ソース領域とドレイン領域との間における第1の不純物領域内に、第2の不純物領域から離間して埋め込まれた、二酸化シリコンより比誘電率が高い絶縁層14と、ソース領域とドレイン領域との間における第1の不純物領域上、第2の不純物領域上及び絶縁層上に、ゲート絶縁膜22を介して形成されたゲート電極24a、24bとを有している。

(もっと読む)

半導体装置の製造方法

【課題】ポリシリコン抵抗体の上に急速熱酸化処理により形成され、シリサイド化ブロック用酸化膜の一部として用いる熱酸化膜の膜厚が多種のポリシリコン抵抗体間でばらつくことにより、ポリシリコン抵抗体が部分的にシリサイド化されることを回避する。

【解決手段】多種のポリシリコン抵抗体全てにおいて、急速熱酸化処理によりポリシリコン抵抗体上に生成される熱酸化膜の膜厚と、ポリシリコン抵抗体を含む非シリサイド化領域に形成された保護酸化膜の膜厚との和が、シリサイド化ブロック用酸化膜としてのブロック性能を確保するために必要な膜厚以上となるように、保護酸化膜の膜厚を決定する。多種のポリシリコン抵抗体間で急速熱酸化処理により生成される熱酸化膜の膜厚に差が生じる場合でも、熱酸化膜と保護酸化膜とをシリサイド化ブロック用酸化膜として用いることにより、充分なブロック性能を確保することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】 アバランシェ耐量が高く、保護する高耐圧トランジスタと同製造工程を用いて形成できる高耐圧ESD保護ダイオードを提供する。

【解決手段】 カソード領域8を構成するN型低濃度半導体基板1とアノード領域7を構成するP型低濃度拡散領域14から形成されるPN接合部の基板表面上に、ゲート酸化膜12を形成し、ゲート酸化膜12とフィールド酸化膜4にまたがって設けられたゲート電極13をゲートプラグ28を介してアノード電極20と電気的に接続することを特徴とする構造により、アバランシェ降伏時にPN接合における電界が緩和し、高アバランシェ耐量を得る。またフィールド酸化膜4の長さを変化させることで、耐圧を調整できる。

(もっと読む)

可変容量ダイオード、半導体装置及びその製造方法

【課題】容量変化比の大きな可変容量ダイオード及び当該可変容量ダイオードを備えた半導体装置を提供することを目的とする。

【解決手段】半導体基板1の表面上に可変容量ダイオードを構成するP−層7及びN+層8、MOSトランジスタを構成するソース層10及びドレイン層11を形成する。次に、N+層8,ソース層10及びドレイン層11を露出させるコンタクトホール13,14を有する層間絶縁膜12を形成する。次に、コンタクトホール13内で露出したN+層8を被覆するレジスト層15を形成する。次に、コンタクトホール14を介して高濃度のN型不純物イオンをソース層10及びドレイン層11に注入してN++層16を形成する。この際、不純物イオンがN+層8に注入されないようにする。次に、コンタクトホール13,14内にカソード電極17,金属配線18を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】抵抗素子の占有面積を広げずに抵抗素子の抵抗値を上げることができることができる半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、絶縁膜2上に形成された複数の抵抗素子4bと、絶縁膜2上及び複数の抵抗素子4b上に形成された第2の絶縁膜8と、第2の絶縁膜8に埋め込まれ、複数の抵抗素子4bの両端部それぞれ上に位置する複数の導電プラグ9bと、第2の絶縁膜8上に形成され、複数の導電プラグ9bを介して複数の抵抗素子4bを直列に接続する配線10bとを具備する。半導体基板1に形成され、ポリシリコンからなるゲート電極4aを有するトランジスタを具備していてもよい。ゲート電極4abの表層はシリサイド化されており、ポリシリコン抵抗4bの表層はシリサイド化されていないのが好ましい。

(もっと読む)

MOSトランジスタ集積素子及び製造方法

【目的】高耐圧化及びサイズの縮小化が容易であり、また製造TATが短く低コストのMOSトランジスタ集積素子及び製造方法を提供する。

【解決手段】 高耐圧MOSトランジスタの形成領域に第1の低濃度拡散層を形成する第1ステップと、高耐圧MOSトランジスタの形成領域及び低耐圧MOSトランジスタの形成領域を分離する分離トレンチ及び上記高耐圧MOSトランジスタのゲートトレンチを同時に形成する第2ステップと、低耐圧MOSトランジスタの形成領域にプレート型ゲート電極を形成する第3ステップと、低耐圧MOSトランジスタの形成領域に第2の低濃度拡散層を形成する第4ステップと、を有している。

(もっと読む)

BiCDMOS構造及びその製造方法

【課題】 DMOS電力回路、CMOSデジタル論理回路、及びコンプリメンタリバイポーラアナログ回路の全てを単一の集積化された回路チップ上に実現するBiCDMOS構造及びその製造方法を提供することにある。

【解決手段】 基層内に下向きに延出し、且つ基層の上に配置されたエピタキシャル層内に上向きに延出し、かつエピタキシャル層の上側主面の下に配置された埋め込み絶縁領域と、エピタキシャル層内のみに配置され、かつ埋め込み絶縁領域の上側主面から上向きに延出した埋め込みウェル領域と、エピタキシャル層内に配置され、かつエピタキシャル層の上側主面からエピタキシャル層内に下向きに延出し、かつ埋め込みウェル領域の上側主面に接触する下側主面を備えたウェル領域とを有し、バイポーラトランジスタがウェル領域内に形成され、MOSトランジスタがウェル領域外のエピタキシャル層の上側主面に形成される。

(もっと読む)

BiCDMOS構造及びその製造方法

【課題】 DMOS電力回路、CMOSデジタル論理回路、及びコンプリメンタリバイポーラアナログ回路の全てを単一の集積化された回路チップ上に実現するBiCDMOS構造及びその製造方法を提供することにある。

【解決手段】 基層内に下向きに延出し、且つ基層の上に配置されたエピタキシャル層内に上向きに延出し、かつエピタキシャル層の上側主面の下に配置された埋め込み絶縁領域と、エピタキシャル層内のみに配置され、かつ埋め込み絶縁領域の上側主面から上向きに延出した埋め込みウェル領域と、エピタキシャル層内に配置され、かつエピタキシャル層の上側主面からエピタキシャル層内に下向きに延出し、かつ埋め込みウェル領域の上側主面に接触する下側主面を備えたウェル領域とを有し、バイポーラトランジスタがウェル領域内に形成され、MOSトランジスタがウェル領域外のエピタキシャル層の上側主面に形成される。

(もっと読む)

半導体装置

【課題】SOIデバイスにおいて、SOI層が薄膜化されてもPN接合ダイオードやバイポーラトランジスタにおけるPN接合面積を大きくすることができる半導体装置を得ること。

【解決手段】P型半導体基板1上に埋込み酸化膜層2と半導体膜3Pが順に積層されたSOI基板上に、MOSトランジスタ10NとPN接合ダイオード30が形成される半導体装置であって、PN接合ダイオード30は、埋込み酸化膜層2と半導体膜3Pを除去して得られる半導体基板1上の領域に成長したエピタキシャル層中に、P型高濃度拡散層32PとN型高濃度拡散層33Nを形成してなる。

(もっと読む)

半導体装置及びその製造方法

【課題】 微細化してもリーク電流の増大及び不純物領域の抵抗の上昇を防止できるツェナーダイオード構造及びその製造方法を提供する。

【解決手段】 ツェナーダイオードは、pn接合を生じるように形成されたn型半導体層2並びにp型半導体層3及び4と、n型半導体層2とp型半導体層3及び4とのpn接合部を覆う絶縁膜5と、n型半導体層2と電気的に接続するカソード電極配線6aと、p型半導体層4と電気的に接続するアノード電極配線6bとを備えている。p型半導体層3及び4からなるp型半導体領域は、第1の拡散深さ及び第1のピーク濃度を持つ第1のp型不純物濃度分布と第1の拡散深さよりも浅い第2の拡散深さ及び第1のピーク濃度よりも高い第2のピーク濃度を持つ第2のp型不純物濃度分布とを重ね合わせた不純物濃度分布を有する。第1のp型不純物濃度分布のpn接合部での濃度は第2のp型不純物濃度分布のpn接合部での濃度よりも高い。

(もっと読む)

半導体製造装置の製造方法及び半導体装置

【課題】 CMOSプロセスに容易に組み込むことができ、小面積でも比較的大電流が流せると共に低リーク性能に優れるダイオードを有する半導体装置の製造方法及び半導体装置を提供する。

【解決手段】 P型基盤11に複数のウェル領域を形成する際、その一つをダイオード用ウェル領域(N型)121dとする。次に、反転防止層161の形成と同時にダイオード用ウェル領域121d内にP型のダイオードベース領域162を形成する。その後、フィールド酸化膜19を形成する。Nチャネル型やPチャネル型のMOSFETのソース/ドレイン領域の形成時と同一の工程でN型の第1電極用拡散層221及び第2電極用拡散層222、P型の第3電極用拡散層23を形成する。第1電極用拡散層221に接続される配線を形成してカソード端子KTとし、第2電極用拡散層222と第3電極用拡散層23が共通接続される配線を形成してアノード端子ATとする。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜の破壊耐圧よりも低い接合耐圧を有するpn接合ダイオードを形成し、これを用いた保護回路によりMOSトランジスタのゲート絶縁膜破壊を防止する。

【解決手段】回路保護用のpn接合ダイオード素子は、p型半導体基板21に形成されたpウェル領域23と、pウェル領域23に接してp型半導体基板21の上部に設けられたn型拡散層24とから構成されている。pウェル領域23は、基板表面において、隣接するn型拡散層24との間でpn接合界面を形成する。このpn接合界面でのp型、n型の不純物濃度は各々C2,C1であり、これらはn型拡散層24の底面におけるpウェル領域23の不純物濃度C3よりも高いため、接合耐圧は通常のpn接合に比べて低下する。このpn接合ダイオード素子を保護素子として入出力回路に接続することで、保護素子として用いることができる。

(もっと読む)

フラッシュメモリ素子の製造方法

【課題】ジャンクジョンブレークダウン電圧(JBV)の低下なしで電流誘導能力を向上させることが可能なフラッシュメモリ素子の製造方法を提供する。

【解決手段】高電圧PMOSトランジスタ領域および低電圧素子領域を有する半導体基板上に多数のゲートを形成する段階と、前記高電圧PMOSトランジスタ領域のゲート両側半導体基板内に低濃度p型イオン注入領域を形成する段階と、前記高電圧PMOSトランジスタ領域に高濃度BF2イオンを注入して前記低濃度p型イオン注入領域内に高濃度p型イオン注入領域を形成する段階と、前記高電圧PMOSトランジスタ領域および低電圧素子領域に低濃度のn型不純物イオンを注入する段階とを含む。

(もっと読む)

半導体装置

【課題】LDD構造のトランジスタ素子の特性に悪影響を与えることなく同一基板上に高抵抗体素子を形成する。

【解決手段】シリコン基板1にNウェル領域3、素子分離酸化膜5、ゲート酸化膜7、ポリサイドゲート電極9、低濃度拡散領域17,21を形成した後、シリコン基板1上全面にCVD酸化膜を形成し、さらにその上に抵抗値制御のための不純物としてBF2を導入した高抵抗体素子パターン25を形成し、CVD酸化膜のエッチバックを行なってサイドウォールスペーサ15a及びCVD酸化膜パターン15bを形成し、高抵抗体素子パターン25の両端側に低抵抗領域29を形成して抵抗体領域27を形成する。

(もっと読む)

半導体装置及びその製造方法

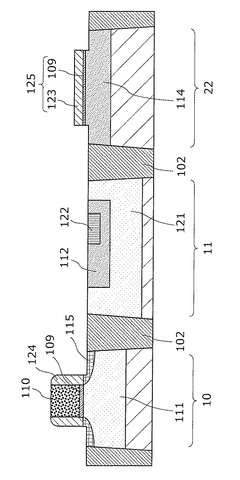

【課題】 SOI部の素子に対して閾値電圧の制御及び短チャネル効果の改善を比較的簡単に行うことのできる素子構造及びその製造方法を提供する。

【解決手段】 半導体装置10は、支持基板13と、前記支持基板上に設けられ、5−10nmの厚さを有する埋め込み絶縁膜14と、前記埋め込み絶縁膜上に設けられたシリコン層15と、前記シリコン層に設けられたMOSFET11と、前記MOSFET11の下部にあって前記支持基板13中に局所的に設けられたトリプルウエル領域17、18とからなる。

(もっと読む)

1 - 16 / 16

[ Back to top ]