Fターム[5F048DA04]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 製造方法 (5,886) | 1MOSソース・ドレインとの同時形成 (180) | 1又は2MOSのゲート(多結晶Si) (37)

Fターム[5F048DA04]に分類される特許

1 - 20 / 37

半導体装置の製造方法および半導体装置

【課題】互いに異なる特性を備える複数の電界効果トランジスタを同一基板上に有する半導体装置の製造歩留まりを向上させる。

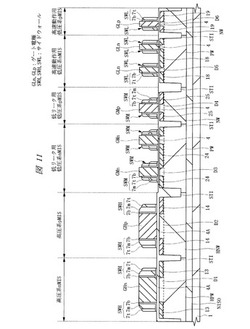

【解決手段】異方性のドライエッチングと等方性のウェットエッチングまたは等方性のドライエッチングとを組み合わせることにより、互いにサイドウォール長の異なる3種類のサイドウォールSWL,SWM,SWHを形成する。異方性のドライエッチングの回数を減らすことにより、配置密度の高い第3nMIS領域および第3pMIS領域において、隣り合うゲート電極GLnとゲート電極GLnとの間、隣り合うゲート電極GLnとゲート電極GLpとの間、および隣り合うゲート電極GLpとゲート電極GLpとの間の半導体基板1の削れを防止することができる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において工程数の削減を図ること。

【解決手段】領域HVp、LVn、LLnに第1〜第3のゲート電極36a〜36cを形成する工程と、領域LVnを覆い、かつ、領域HVpと領域LLnを露出するマスクパターン40を形成する工程と、マスクパターン40をマスクにしたイオン注入でp型ソースドレインエクステンション41とp型ポケット領域42を形成する工程と、マスクパターン40をマスクにしたイオン注入でn型ソースドレインエクステンション45を形成する工程と、領域HVpと領域LLnを覆い、かつ、第2の領域LVnを露出するマスクパターン52を形成する工程と、マスクパターン52をマスクにしてインジウムをシリコン基板1にイオン注入し、p型ポケット領域54を形成する工程とを有する半導体装置の製造方法による。

(もっと読む)

MOSトランジスタおよびその製造方法、半導体集積回路装置

【課題】MOSトランジスタのチャネル領域に、基板上に形成した応力膜からより効率的に応力を印加する半導体装置の構造及びその製造方法を提供する。

【解決手段】MOSトランジスタは、n型またはp型のソース・ドレイン領域21e〜hと、素子分離領域21Iからチャネル領域に向かって延在し、ソース・ドレイン領域21e〜hを覆って形成された、引張応力、圧縮応力のいずれかである応力膜27A、27Bを備える。応力膜27A,27Bは、ゲート電極23A,23Bの側壁面に沿って、ただし側壁面からは隙間32A〜Dを介して形成される。ソース・ドレイン領域21e〜hがn型である場合、応力膜の応力は引張応力であり、ソース・ドレイン領域21e〜hがp型である場合、応力膜の応力は圧縮応力である。

(もっと読む)

高誘電率のゲート絶縁膜を有する半導体装置及びそれの製造方法

【課題】本発明はゲート構造物として高誘電率を有する物質として、高誘電率を有する物質からなるゲート絶縁膜を含む半導体装置及びその製造方法に関する。

【解決手段】半導体装置及びその製造方法において、基板上に形成され、ハフニウムシリコン酸化物含有固体物質を含むゲート絶縁膜パターンと前記ゲート絶縁膜パターン上に形成される第1ゲート導電膜パターンを含むゲート構造物及び前記ゲート構造物と隣接する基板の表面部位に配置されており、n型不純物がドーピングされたソース/ドレイン領域を含むことを特徴とする。

(もっと読む)

半導体集積回路装置の製造方法

【課題】低抵抗で、かつ接合リーク電流の少ないCoシリサイド層を形成することのできるサリサイドプロセスを提供する。

【解決手段】Co純度が99.99%以上で、FeおよびNiの含有量が10ppm以下、より好ましくはCo純度が99.999%の高純度Coターゲットを用いたスパッタリング法によってウエハの主面上に堆積したCo膜をシリサイド化することにより、MOSFETのゲート電極(8n、8p)、ソース、ドレイン(p+型半導体領域13、n+型半導体領域14)の表面に低抵抗で接合リーク電流の少ないCoSi2層(16b)を形成する。

(もっと読む)

半導体装置の製造方法

【課題】異なる直流電流増幅率(hfe)を有する複数のバイポーラトランジスタを混載した半導体装置を、簡易且つ工程数が少なく得られる半導体装置の製造方法を提供すこと。

【解決手段】第2バイポーラトランジスタ20のエミッタ領域25又はその周囲上であって、当該エミッタ領域25におけるコンタクト領域25Aの周辺上にダミー層52を形成することで、その後、層間絶縁層53の厚みを厚層化することができるため、第2バイポーラトランジスタ20のエミッタ領域25では第1バイポーラトランジスタ10のエミッタ領域15に比べコンタクト深さを浅くしてコンタクトホール54が形成される。これにより、第1バイポーラトランジスタ10と第2バイポーラトランジスタ20との直流電流増幅率(hfe)を変更できる。ダミー層52の形成は第2バイポーラトランジスタ20のベース領域26、コレクタ領域27であってもよい。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】同一の半導体基板上に数種類のトランジスタを簡易なプロセスによって形成する半導体装置の製造方法の提供。

【解決手段】LDMOS領域100とオフセットドレインMOS領域200とに、同時に、第2導電型の第1ウェル30を形成する工程と、LDMOS領域100の第1ウェル30と、CMOS領域100とに、同時に、第1導電型の第2ウェル32を形成する工程と、CMOS領域300に、第2導電型の第2ウェル34を形成する工程と、オフセットドレインMOS領域200に第1導電型のオフセット層22を形成する工程とを含み、第1ウェル30は、第2ウェル32,34よりも深いウェルであり、第2ウェル32,34は、高エネルギーイオン注入法によって形成されたレトログレードウェルである、半導体装置の製造方法。

(もっと読む)

半導体素子及びその製造方法

【課題】高い電圧で作動が可能なトランジスター、中間電圧で作動が可能なトランジスター及び低い電圧で作動が可能なトランジスターが集積された半導体チップを提供する。

【解決手段】半導体素子は、第1導電型不純物が注入された第1領域111を含む半導体基板110と、第1領域111上に第1活性領域及AR1び第2活性領域AR2を定義して配置される素子分離膜120と、第1活性領域AR1に第1間隔で相互離隔されて、第2導電型不純物が注入されて形成される第1LDD領域151と、及び第2活性領域AR2に前記第1間隔より狭い第2間隔で相互離隔されて、第2導電型不純物が注入されて形成される第2LDD領域152を含む。

(もっと読む)

半導体素子とその作製法

二重ゲート電極(60,50)及びそれを形成する方法を述べた。第1の金属/シリコンのゲート積層と第1のゲート誘電体(40)とが第1のドープされた領域の上に形成される。金属/ゲート積層(60,50)は第1のゲート誘電体(40)上の金属部(50)と、金属部(50)上の第1のゲート部(60)とからなる。シリコンゲート(60)と第2のゲート誘電体(40)は第2のドープされた領域の上に形成される。一実施例において、第1と第2のゲート部はP+にドープされたシリコン・ゲルマニウムであり、金属部はTaSiNである。他の実施例において、第1と第2のゲート部はN+にドープされたポリシリコンであり、金属部はTaSiNである。図5は概要を示す。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 2種類以上の電源電圧に対応するように複数のMOSFETを同一半導体基板上に混載する半導体装置において、微細化を進めても高性能を維持することが可能なゲート構造を提供する。

【解決手段】 半導体基板1に形成され、高誘電体材料を用いたゲート絶縁膜9を備えたMOSFETと高誘電体材料を含まないゲート絶縁膜10を備えたMOSFETを有し前記高誘電体材料を用いたゲート絶縁膜を備えたMOSFETのゲート電極がシリサイドもしくは金属で構成され、前記高誘電体材料を含まないゲート絶縁膜を備えたMOSFETのゲート電極が多結晶又は非晶質シリコンもしくはシリコンゲルマニウムから構成されている。1つの半導体基板に混載された低電圧動作MOSFET及び高電圧動作MOSFETの各々に最適なゲート電極を提供することが可能となり微細化を進めて素子性能低下を避ける。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 電流のリークが生じにくい半導体装置を提供する。

【解決手段】 半導体基板1に形成された素子分離膜2と、高電圧駆動トランジスタのゲート酸化膜3aと、ゲート酸化膜3a上に形成されたゲート電極4aと、半導体基板1に形成され、低電圧駆動トランジスタのソース及びドレインとして機能する不純物領域7bと、半導体基板1上、素子分離膜2a,2b上及びゲート電極4a上それぞれに形成された第1のエッチングストッパー膜9と、第1のエッチングストッパー膜9上に形成され、不純物領域7bの上方に位置する第2のエッチングストッパー膜10と、第1のエッチングストッパー膜9上、及び第2のエッチングストッパー膜10上に形成された絶縁膜11と、絶縁膜11に形成され、不純物領域7b上に位置する接続孔11bとを具備する。

(もっと読む)

半導体装置とその製造方法

【課題】

酸化シリコンより誘電率の高い高誘電率絶縁膜を有する半導体装置を提供する。

【解決手段】

半導体装置の製造方法は、(a)シリコン基板の活性領域表面にSiOまたはSiONの界面層を形成し、(b)界面層上方に酸化シリコンより高い誘電率を有するHfSiON等の高誘電率のゲート絶縁膜を形成し、(c)ゲート絶縁膜上方にポリシリコンのゲート電極を形成し、(d)高誘電率のゲート絶縁膜形成前後の少なくとも一方で、基板表面をパッシヴェーション処理し、(e)少なくともゲート電極、高誘電率のゲート絶縁膜をパターニングして絶縁ゲート電極構造を形成し、(f)絶縁ゲート電極構造両側の活性領域にソース/ドレイン領域を形成する。

(もっと読む)

半導体装置、半導体集積回路装置および半導体装置の製造方法

【課題】 1つの半導体装置を複数種の電源電圧に対応させる。

【解決手段】 ソース領域4に隣接する領域に、ソース領域4とドレイン領域5の間に形成されるチャネル領域6と同導電型のポケット領域7を形成してチャネル濃度を下げるために、ソース領域4とドレイン領域5の間の領域を、不純物濃度がソース領域4側で高くドレイン領域5側で低い非対称の濃度プロファイルにする。これにより、ドレインバイアスを印加した時のインパクトイオン化によって生じる電流を低減し、ホットキャリアに起因する特性劣化を抑えてホットキャリア耐性を向上させ、複数種の電源電圧に対応させる。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】 CMOSを基板上に有する半導体集積回路装置において、pMOSトランジスタにおいてSiGe混晶層よりなる圧縮応力発生源を、基板中、前記pMOSトランジスタのチャネル領域に可能な限り近接させて配置し、同時にnMOSトランジスタにおいて、ソース/ドレイン拡散領域の間に充分な距離を確保してリーク電流の発生を抑制する。

【解決手段】 pMOSトランジスタのゲート電極側壁絶縁膜を、HF耐性を有する膜により形成し、pMOSトランジスタの素子領域に前記p型SiGe混晶層がエピタキシャル成長するトレンチを、前記pMOSトランジスタのチャネル領域に近接して形成すると同時に、nMOSトランジスタ領域においては、ゲート電極の側壁絶縁膜の外側にさらに別の側壁絶縁膜を形成し、基板中にイオン注入により形成されるn型ソース/ドレイン領域の間に充分な距離を確保する。

(もっと読む)

半導体装置およびその製造方法

【課題】 SALICIDE技術を容易に適用することが可能な半導体装置およびその製造方法を提供する。

【解決手段】 半導体装置1は、半導体基板11に形成された一対の拡散層21と、一対の拡散層21に挟まれた領域上に形成されたゲート電極23と、ゲート電極23の側面に形成された一層以上の絶縁膜25と、絶縁膜35を挟んでゲート電極23側面に形成されたサイドウォール26と、拡散層21の上部であって絶縁膜25下およびサイドウォール26下を含まない領域に形成された高濃度拡散層24とより構成された高耐圧MOSFET20を有する。絶縁膜25は例えば窒化シリコンで形成される。サイドウォール26は例えば酸化シリコンで形成される。

(もっと読む)

半導体装置の製造方法

不純物のゲート絶縁膜突き抜けを抑制できると共にソース/ドレイン領域の容量増大、リーク電流増大を抑制できる半導体装置の製造方法を提供する。 半導体装置の製造方法は、n型ウェル内にn型閾値調整領域を有する半導体基板上にゲート絶縁膜を介して、ゲート電極を形成し、低い加速エネルギで、p型不純物をイオン注入してゲート電極両側の半導体基板内にエクステンション領域を形成し、ゲート電極の側壁上に、サイドウォールスペーサを形成し、ゲート電極内で実質的異常テーリングを生じない低いドーズ量、比較的高い加速エネルギで、p型不純物をイオン注入して閾値調整領域より深いp型ソース/ドレイン領域を形成し、半導体基板に原子をイオン注入し、ゲート電極とソース・ドレイン領域の上層をアモルファス化し、高ドーズ量で、p型不純物をイオン注入し、ソース/ドレイン領域内に高濃度領域を形成し、イオン注入した不純物を活性化する。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能を向上させることが可能な技術を提供する。

【解決手段】ゲート構造20及びオフセットスペーサ5a,5bを覆って半導体基板1上に下層膜8、中層膜9及び上層膜10を順に形成する。下層膜8及び上層膜10は、LPCVD法を用いてTEOSを分解することにより形成されるシリコン酸化膜である。そして、下層膜8、中層膜9及び上層膜10を部分的に除去して半導体基板1を露出させ、ゲート構造20の側面上に下層膜8、中層膜9及び上層膜10を含むサイドウォールスペーサをオフセットスペーサ5aを介して形成する。

(もっと読む)

半導体装置及びその製造方法

Si基板(11)の表面にpウェル(12)を形成し、素子分離絶縁膜(13)を形成する。次に、全面に薄いSiO2膜(14a)を形成し、その上に希土類金属(例えばLa、Y)及びAlを含有する酸化膜を絶縁膜(14b)として形成する。

更に、絶縁膜(14b)上にポリSi膜(15)を形成する。その後、例えば1000℃程度の熱処理を行うことによって、SiO2膜(14a)と絶縁膜(14b)とを反応させ、希土類金属及びAlを含有するシリケート膜を形成する。即ち、SiO2膜(14a)及び絶縁膜(14b)を単一のシリケート膜とする。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 製造工程の短縮が可能なBiCMOS型半導体装置の製造方法を提供する。

【解決手段】 エピタキシャル層12を形成したシリコン基板11表面に、素子分離領域15で分離されたバイポーラ/MOSトランジスタとなる領域を形成し、シリコン基板11表面に絶縁膜41を形成する工程と、エミッタ及びソース/ドレイン用の開口42を形成する工程と、これらのトランジスタ領域にポリシリコン膜を形成し、n型のPを導入する工程と、絶縁膜41の開口42及びその周辺部にあるポリシリコン膜にn型のAsを選択的に導入する工程と、絶縁膜41上のポリシリコン膜を残してエミッタ電極51、開口42のポリシリコン膜を残してソース/ドレイン電極52及びゲート電極53を形成する工程と、半導体基板11を熱処理して、n型不純物をベース領域23及びウェル領域33に拡散させて、エミッタ領域25及びソース/ドレイン領域32を形成する工程とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】 本発明は、ゲート電極の空乏化を抑制すると共に、シリサイドの高抵抗化を防止することができる半導体装置及びその製造方法を提供する。

【解決手段】 ゲート絶縁膜上に、所定の半導体材料とゲルマニウムとを含む膜を形成するステップと、膜を酸化することにより、ゲート絶縁膜上に、当該膜よりもゲルマニウム濃度が高くかつ膜厚が薄い第1の膜を形成すると共に、第1の膜上に酸化膜を形成するステップと、酸化膜を除去するステップと、第1の膜上に、半導体材料を含み、第1の膜よりもゲルマニウム濃度が低い第2の膜を形成するステップと、第2の膜及び第1の膜にエッチングを行うことにより、ゲート電極を形成するステップとを備えることを特徴とする。

(もっと読む)

1 - 20 / 37

[ Back to top ]