Fターム[5F058AG07]の内容

絶縁膜の形成 (41,121) | 有機絶縁膜形成後の処理 (1,322) | プラズマ処理(後処理) (74)

Fターム[5F058AG07]に分類される特許

41 - 60 / 74

還元性雰囲気下における絶縁膜の硬化

【課題】低誘電率の多孔質物質含有膜を提供すること。

【解決手段】Si、C、O、H及びSi-CH3種を含み、かつ少なくとも1つの含Si構造形成物質と少なくとも1つの含C細孔形成物質とを含む複合膜を基板表面の少なくとも一部分に形成する工程; 該複合膜及び該複合膜を活性化学種に暴露して前記含C細孔形成物質を少なくとも部分的に改質し、その際、形成されたままの状態の皮膜中のSi-CH3種の少なくとも90%(FTIRにより測定)を暴露工程後も皮膜中に残す工程を含む多孔質絶縁膜形成方法。

(もっと読む)

絶縁膜形成用組成物およびその製造方法、ならびにシリカ系絶縁膜およびその形成方法

【課題】半導体素子などにおける層間絶縁膜として好適に用いることができる絶縁膜形成用組成物およびその製造方法、ならびに前記絶縁膜形成用組成物を用いたシリカ系絶縁膜およびその形成方法を提供する。

【解決手段】絶縁膜形成用組成物は、(A)成分;下記一般式(1)で表される化合物および下記一般式(2)で表される化合物の群から選ばれた少なくとも1種のシラン化合物と、(B)成分;下記一般式(3)で表される構造を有するカルボシランとを加水分解縮合して得られた加水分解縮合物と、有機溶媒と、を含む。R1aSi(OR2)4−a ・・・・・(1) R3b(R4O)3−bSi−(R7)d−Si(OR5)3−cR6c ・・・(2)

・・・・・(3)

(もっと読む)

薄膜トランジスタの製造方法および薄膜トランジスタならびに表示装置

【課題】本発明は、量産に適し、低コストで製造可能な薄膜トランジスタの製造方法および薄膜トランジスタならびにこれを用いた表示装置を提供する。

【解決手段】基板11上に有機半導体層14、ゲート絶縁膜15、ゲート電極16をこの順に積層してなる薄膜トランジスタ10の製造方法において、印刷法により、ゲート絶縁膜15上にゲート電極材料をパターン塗布する工程と、熱処理を行うことで、パターン塗布されたゲート電極材料を乾燥固化してなるゲート電極16を形成することを特徴とする薄膜トランジスタの製造方法および薄膜トランジスタならびにこの薄膜トランジスタを用いた表示装置である。

(もっと読む)

制御された気孔を形成するための材料及び方法

【課題】基材の内部に空隙を形成するための方法を提供する。

【解決手段】基材を用意する工程;少なくとも1つの犠牲材料前駆体の堆積によって犠牲材料を堆積する工程;複合層を堆積する工程;該複合層中のポロゲン材料を除去して多孔質層を形成する工程;及び積層基材を除去媒体と接触させて前記犠牲材料を実質的に除去し、前記基材の内部に空隙を与える工程を含み、前記少なくとも1つの犠牲材料前駆体が、有機ポロゲン、シリコン、極性溶媒に可溶な金属酸化物、及びそれらの混合物からなる群より選択される方法が提供される。

(もっと読む)

ポロゲン、ポロゲン化された前駆体および低誘電率をもつ多孔質有機シリカガラス膜を得るためにそれらを使用する方法

【課題】低い誘電率および改良された機械的性質、熱的安定性および化学的耐性を有する多孔質有機シリカガラス膜を提供する。

【解決手段】式SivOwCxHyFz(ここで、v+w+x+y+z=100%、vは10〜35原子%、wは10〜65原子%、xは5〜30原子%、yは10〜50原子%、およびzは0〜15原子%)で表わされる多孔質有機シリカガラス膜を製造する。オルガノシランおよびオルガノシロキサンからなる群より選ばれる前駆体ならびにポロゲンを含むガス状試薬を真空チャンバに導入し、ガス状試薬にエネルギーを加え、ガス状試薬の反応を生じさせて基体上に予備的な膜を堆積させる。その予備的な膜は細孔を持ち、誘電率が2.6未満である多孔質膜を得るために、実質的にすべてのポロゲンを除去される。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体メモリを構成するキャパシタセルの形成工程において、高精度に拡大された表面積を有するキャパシタセルを形成する。

【解決手段】半導体基板100上にシリコン酸化膜104aとSiCwHxOyNz(w>0、x≧0、y>0、z≧0)で表される有機無機ハイブリッド膜104bとを交互に堆積して積層膜104を形成する工程と、積層膜104に開口部106を形成する工程と、積層膜104の開口部106側面に露出したSiCwHxOyNz(w>0、x≧0、y>0、z≧0)で表される有機無機ハイブリッド膜104bの所定部分を酸化層108に変換する工程と、酸化層108を選択的に除去して、積層膜104の開口部106側面に凹凸109を形成することを含む。

(もっと読む)

膜、膜形成用組成物及び該膜を有する電子デバイス

【課題】電子デバイスなどに用いられる、低誘電率であるとともに、耐熱性、機械的強度に優れた膜、該膜を提供できる膜形成用組成物、該膜を有する電子デバイスを提供する。

【解決手段】アダマンタン、ビアダマンタン、ジアマンタン、トリマンタン、テトラマンタンのカゴ型構造を有するモノマーの重合体よりなり、ラマン分光測定において、ラマンシフト300〜3100cm-1の領域において最も強度が高いピークが690〜800cm-1に存在する膜、該膜を形成する膜形成用組成物、さらには該膜を有する電子デバイス。

(もっと読む)

半導体装置とその製造方法

【課題】 半導体装置の保護膜に蓄積する負の電荷によって、半導体基板内の電荷バランスが崩れ、半導体装置の耐圧が低下してしまう。本発明は、簡便な方法を利用して、前記課題を解決することを目的としている。

【解決手段】 半導体装置10は、回路素子が作り込まれている半導体基板35と、その半導体基板35上に形成されている絶縁性の保護膜46を備えている。保護膜46の表面47には、水酸基(OH)が結合している。これにより、保護膜46の表面47は、水滴との接触角が40°以下になっている。

(もっと読む)

Xランプヒーター付き真空反応チャンバ

基板を電子ビーム処理する方法及び装置が提供される。真空チャンバ、該真空チャンバと連通する少なくとも1つの熱電対アセンブリ、上記真空チャンバと連通する加熱装置、及びその組み合せを備えた電子ビーム装置が提供される。一実施形態において、真空チャンバは、電子源を備え、該電子源は、高電圧源に接続されたカソードと、低電圧源に接続されたアノードと、基板支持体とを備えている。別の実施形態では、真空チャンバは、アノードと基板支持体との間に置かれたグリッドを備えている。一実施形態では、加熱装置は、第1の平行なライトアレイ及び第2のライトアレイを備え、これら第1の平行なライトアレイ及び第2のライトアレイは交差する。一実施形態では、熱電対アセンブリは、窒化アルミニウムで作られた温度センサを備えている。 (もっと読む)

絶縁膜の形成方法及び絶縁膜の形成装置

【課題】均一に空孔を形成できる絶縁膜の形成方法及び絶縁膜の形成装置を提供する。

【解決手段】1,3,5−トリメチル1,3,5−トリビニルシクロトリシロキサン(V3D3)とイソプロピルアルコール(IPA)とをチャンバ12内に供給し、プラズマによりこれらを励起してこれらの化合物の分子状の活性種を発生させる。これらの活性種を基板の表面近傍で反応させ、例えば、IPA分子を含む厚さ50nmの絶縁膜の薄膜を形成する。さらに、アンモニアガスを用いたプラズマ処理により、薄膜中に含まれるIPA分子を選択的に脱離させて、厚さ方向に均一な空孔を形成する。この成膜工程と空孔形成工程とを複数回繰り返して、所定厚さで、且つ、均一に空孔が形成された絶縁膜を得ることができる。

(もっと読む)

絶縁膜の製造方法

【課題】 耐吸湿性、機械強度等の膜特性が良好な絶縁膜の製造方法、さらに該製造方法を用いて得られる絶縁膜に関し、さらには該絶縁膜を有する電子デバイスを提供する。

【解決手段】 カゴ型構造を有する化合物を含む膜形成用組成物を用いて塗膜を形成する工程、および、水酸基と反応可能な化学種を用いて前記塗膜中の水酸基を反応させる工程を具備することを特徴とする絶縁膜の製造方法、それを用いて得られる絶縁膜、およびそれを有する電子デバイス。

(もっと読む)

最新のLow−k材料のための紫外線硬化法

【課題】最新のLow−k材料のための紫外線硬化法の提供。

【解決手段】改善された弾性率及び材料硬度を有する低誘電率材料。このような材料の製造方法は、誘電材料を準備すること、及び、該材料を紫外線(UV)硬化させて、UV硬化誘電材料を製造することを含む。UV硬化は、改善された弾性率及び材料硬度を有する材料をもたらす。改善は、それぞれ、典型的には、50%より大きいか、又は約50%である。UV硬化誘電材料は、所望により、UV後処理され得る。UV後処理は、LIV硬化誘電材料と比べて、材料の誘電率を低下させ、更に、改善された弾性率及び材料硬度を維持する。UV硬化誘電体は、更に、炉での硬化法よりも、硬化において、より低い総熱量を示し得る。

(もっと読む)

補強層を設けることによって低k誘電体内に埋め込まれる銅含有線を形成するための技術

銅含有金属で満たされるトレンチ(104)の3つの側壁(1055)に補強層(105)を設けることによって、少なくとも或る程度まで、低k誘電体材料(102)が熱機械的に閉じ込める度合いが弱いことを補償することができ、それによりエレクトロマイグレーション効果を低減し、それゆえ、銅に基づく金属線と共に低k誘電体材料(102)を含むメタライゼーション層を有する複雑な半導体デバイスの寿命を延ばすことができる。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】銅配線と、その上部の接続プラグとのコンタクト箇所の信頼性を向上させる。

【解決手段】CoWPからなるキャップメタル34の上部に、キャップメタル窒化層35を設ける。キャップメタル34およびキャップメタル窒化層35の膜厚は、たとえば1nm〜100nmとする。キャップメタル34の膜厚に対するキャップメタル窒化層35の膜厚の比は、たとえば0.1〜1とする。また、SiOC膜14aの上には、SiOC膜14aの表面が窒化したSiOCN層16が形成されている。SiOCN層16は、表面に窒素が偏析した領域からなる層であって、その厚みは、たとえば1nm〜100nmとする。

(もっと読む)

高度な低誘電率の有機シリコン・プラズマ化学気相堆積膜

【課題】 良好な電子特性及び機械的特性を示す、多孔質の低k又は超低k誘電体膜を提供すること。

【解決手段】 約3.0未満の誘電率と、より度合いが大きい結晶結合相互作用と、従来技術のSiCOH誘電体と比べて、より多くのメチル末端基などの炭素と、より少ないメチレン、−CH2−架橋基とを有する、共有結合三次元ネットワーク構造において、Si、C、O及びHの原子(以下、「SiCOH」)を含む多孔質低k又は超低k誘電体膜が提供される。SiCOH誘電体は、約1.40未満のCH3+CH2伸縮についてのピーク面積と、約0.20未満のSiH伸縮についてのピーク面積と、約2.0より大きいSiCH3結合についてのピーク面積と、約60より大きいSi−O−Si結合についてのピーク面積とを含むFTIRスペクトルと、約20%より大きい多孔度とを有するものとして特徴付けられる。

(もっと読む)

絶縁膜の形成方法、多層構造の形成方法および半導体装置の製造方法

【課題】 Low−k絶縁膜を効率的に形成する。

【解決手段】 Low−k材料を溶媒中に分散させて形成した前駆体溶液を下地層等の上にスピンコートし、その塗膜に対して溶媒沸点付近の温度でおよそ数分間加熱しベーク処理を行う(ステップS1〜S3)。そして、そのベーク処理後の塗膜上に、CVD法を用いてSiC等でバリア膜を形成した後、その際のCVD装置から取り出すことなくそのCVD装置を用いてバリア膜越しに水素プラズマ処理を行う(ステップS4,S5)。

(もっと読む)

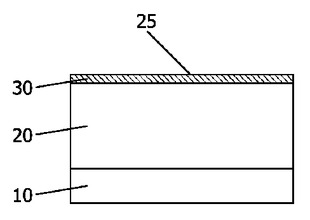

半導体デバイスの製造方法

本発明は、半導体デバイスの製造方法に関するものである。この方法では、半導体デバイスは、基板(10)を具え、この基板(10)は、表面(25)を有する低−kの前駆物質層(20)で覆われている。この工程の後、部分硬化工程が行われ、前記低−kの前駆物質層(20)の表面(25)またはその近くに緻密層(30)が形成される。この緻密層(30)は、保護層(30)として作用することができる。前記低−kの前駆物質層(20)は、未硬化、または部分的に硬化された状態で適用できる特性を有する材料の群から選択される。この方法の主な利点は、前記緻密層(30)が、前記低−kの前駆物質層(20)自体から形成されるため、別個の保護層(30)を低−kの前駆物質層(20)に設ける必要がない点である。したがって、前記緻密層(30)は、前記低−kの前駆物質層(20)に対して良好な接着性を有する。  (もっと読む)

(もっと読む)

表面疎水化方法、ならびに半導体装置およびその製造方法

【課題】その後の加工プロセスとの整合性を有し、絶縁層の表面をより簡便にかつ効率良く疎水化することができ、かつ、絶縁層のより深い領域を疎水化することができる表面疎水化方法、ならびに半導体装置およびその製造方法を提供する。

【解決手段】絶縁層20を加熱により活性化する工程と、(A)反応性シラン化合物および(B)有機溶媒を含む表面疎水化用組成物を前記絶縁層の表面に接触させる工程とにより、前記絶縁層の表面に疎水性膜を形成する疎水化処理方法および前記疎水性膜を含む半導体装置。

(もっと読む)

多孔質低−k材料用の無弗素プラズマ硬化方法

改良された弾性率および材料硬度を有する低誘電率多孔質材料。このような多孔質材料を作る方法では、無弗素プラズマ硬化された多孔質誘電材料を製造するために、多孔質誘電材料を用意し、無弗素プラズマガスを用いて、プラズマ硬化する。この多孔質誘電材料の無弗素プラズマ硬化により、改良された弾性率および材料硬度、ならびに同等の誘電率を有する材料が製造される。弾性率の改良は、一般に、約50%以上である。 (もっと読む)

配線構造の製造方法

【課題】簡単に絶縁膜を形成することができ、効率良く配線構造を形成することができる配線構造の形成方法を提供すること。

【解決手段】シリコンウエハ11上に反応溶液を塗布する。反応溶液を塗布したシリコンウエハを縦型炉に投入して塗布膜を焼成する。絶縁膜12に対して酸素プラズマ処理を施す。絶縁膜12上にAlをスパッタリング法により被着してAl膜13を形成する。Al膜13上にレジスト膜14を形成して、フォトリソグラフィー法によりパターニングして開口部14aを形成する。レジスト膜14をマスクとしてその開口部14aに露出しているAl膜13に対して塩素プラズマ処理を施してAl膜13をエッチングする。その後、レジスト膜14を除去する。

(もっと読む)

41 - 60 / 74

[ Back to top ]