Fターム[5F064BB06]の内容

ICの設計・製造(配線設計等) (42,086) | ICの機能 (7,082) | デジタル信号処理 (4,646) | 論理ゲート (2,166) | ノア (196)

Fターム[5F064BB06]に分類される特許

1 - 20 / 196

スタンダードセル、および、半導体集積回路

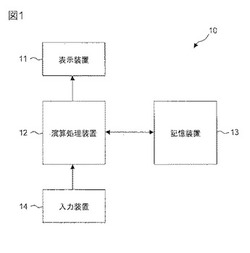

レイアウト装置及びレイアウト方法

【課題】クロックツリーにおけるクロックスキューの調整において、精度の確保とデューティ保持とを両立させる。

【解決手段】レイアウト装置(10)において、MOSトランジスタ1段で形成された第1セルと、MOSトランジスタ複数段で形成された第2セルとがライブラリ化されたテーブルを設ける。また、上記レイアウト装置には、上記第1セルと上記第2セルとの組み合わせによるコンビネーションチェーンを上記クロックツリーに挿入することで、上記クロックツリーにおける異なるクロック系統間のクロックスキューを調整可能な演算処理部(12)を設ける。上記コンビネーションチェーンによってクロックスキューの調整を行うことで、個々の第1セルでの遅延誤差が伝播されるのを抑制し、遅延計算における遅延誤差の低減を図る。また、第1セルはMOSトランジスタ1段で形成され、そこで論理反転されるため、デューティ保持の観点で有利とされる。

(もっと読む)

論理回路の故障検出方法、テスト回路挿入方法、テスト回路挿入装置および半導体集積回路

【課題】 論理ゲートの一方の入力を含む信号パスの遅延故障と、論理ゲートの他方の入力を含む信号パスの遅延故障とを、1つの制御点により検出する。

【解決手段】 第1および第2ユーザロジックと、第1ユーザロジックの出力に接続される第1入力を有する第1論理ゲートと、第1論理ゲートの出力に接続された第3ユーザロジックと、第2ユーザロジックと第1論理ゲートとの間に挿入された制御点とを有する。制御点は、第1または第3ユーザロジックの第1スキャンフリップの1つのデータ出力がデータ入力に接続された第2スキャンフリップフロップと、一対の入力が第2スキャンフリップフロップのデータ出力および第2ユーザロジックの出力にそれぞれ接続され、出力が第1論理ゲートの第2入力に接続された第2論理ゲートとを有する。

(もっと読む)

半導体集積回路及び半導体集積回路の設計方法

【課題】半導体集積回路の回路面積を小さくする。

【解決手段】被試験回路2の観測対象の複数の信号線TA1〜TA4上の観測点TP1〜TP4を複数の入力端子に接続し、複数の信号線TA1〜TA4を伝搬する値の、論理積、論理和、否定論理積、または否定論理和の何れかを演算し、複数の信号線TA1〜TA4の何れかを伝搬する値に応じた出力値を出力する論理回路(NOR回路3,NAND回路4)を設けることで、複数の観測点をEOR回路を用いて共用する半導体集積回路より回路面積を小さくできる。

(もっと読む)

半導体装置

【課題】高品質な半導体装置を提供する。

【解決手段】第1の絶縁膜111、第1の電極112、第2の絶縁膜113、及び第2の電極114を含むゲート構造を有するメモリセルMCが複数設けられた記憶部11と、少なくとも外部100からのデータを受信し、記憶部にデータを供給する端子15と、第1の絶縁膜、第1及び第2の電極とを含むゲート構造を有し、電流経路の一端に第1の電圧が印加される第1導電型の第1のトランジスタ16a、一端が第1のトランジスタの電流経路の他端に接続され、他端が端子に接続される第1の抵抗素子16b、一端が端子及び第1の抵抗素子の他端に接続される第2の抵抗素子16c及び、ゲート構造を有し、電流経路の一端が第2の抵抗素子の他端に接続され、電流経路の他端に第2の電圧が印加される第2導電型の第2のトランジスタ16dを含む第1の回路16と、を備える。

(もっと読む)

集積回路

【課題】電力消費量の増大を抑制しつつ、タイミング信号のスキューを低減する。

【解決手段】主クロック分配回路は、タイミング信号を複数の主タイミング信号に分岐して分配する。副クロック分配回路は、タイミング信号の分配が指示された場合にはタイミング信号を複数の副タイミング信号に分岐して分配する。最小遅延タイミング信号出力部は、複数の主タイミング信号のいずれかと複数の副タイミング信号のいずれかとのうち先に分配された信号を最小遅延タイミング信号として出力する。同期動作回路は、最小遅延タイミング信号に同期して動作する。測定部は、複数の主タイミング信号のいずれかの遅延のばらつきを示す値を測定する。クロック分配回路制御部は、測定された値の示す前記ばらつきが前記所定値以上であるときに副分配回路に前記タイミング信号の分配を指示する。

(もっと読む)

半導体装置

【課題】少しの設計方法の変更で設計できる、一層低消費電力化した半導体装置の実現。

【解決手段】複数の電源供給領域23と、複数の電源供給領域に供給する電源の電圧を切り替える複数の電源切替ユニットSWA,SWBと、を有し、複数の電源供給領域に含まれる回路要素を組み合わせて少なくとも1つの機能ブロックが形成され、少なくとも1つの機能ブロックは、内部に異なる電圧で動作する回路要素を含む半導体装置。

(もっと読む)

半導体集積回路

【課題】半導体集積回路において消費電力を低減するとともに、ノイズの発生を低減する。

【解決手段】半導体集積回路は、複数のDFFを有し、その少なくとも1つが冗長回路とされる。半導体集積回路が通常動作モードである際に、ANDゲート1によって冗長回路であるDFF3−3に印加されるクロック信号を停止する。冗長回路へのクロック信号が停止されると、当該冗長回路においてクロック信号が停止された状態における冗長回路のドレイン−グランド間容量よりもその容量を増加させる。

(もっと読む)

LSIのレイアウトパターン表示装置および表示方法

【課題】レイアウトパターン上で、直観的に回路素子を認識可能とし、回路素子間の信号の流れの把握を容易にする。

【解決手段】レイアウトパターン表示部400により、格納部200,300内に格納されているブロック/セルという階層構造をもったデータを展開して、画面上にレイアウトパターンを表示する。条件設定部800には、セル枠決定に用いる特定のレイヤーを示す情報がセル枠決定条件として設定されており、セル枠決定部600は、個々のセルについて、当該特定のレイヤーに収録されている図形を抽出し、抽出した図形の論理和図形を形成し、この論理和図形の外接矩形をセル枠として求める。端子図形生成部500は、求めたセル枠とセル間配線との交差位置に端子図形を生成する。レイアウトパターン表示部400は、セル枠と端子図形をレイアウトパターン上に重畳表示する。

(もっと読む)

半導体集積回路,および,半導体集積回路の検査方法

【課題】故障検査のために観測用フリップフロップ回路を配置することなく,故障検査を可能とする半導体集積回路,その検査方法を提供する。

【解決手段】第2の論理回路51の試験の際に試験モードを示す制御信号TSMが,故障検査用回路41に入力され,この試験モードに対応するテスト値が,論理回路51に入力されると,故障検査用回路41により,論理回路51の出力論理が,論理回路13に対応するフリップフロップ回路14に入力される。さらに,通常モード時に,論理回路13の出力論理が,故障検査用回路41により,論理回路13に対応するフリップフロップ回路14にそのまま入力される。

(もっと読む)

半導体装置および判定方法

【課題】ヒューズの切断または非切断をより正しく判定することが可能な半導体装置および判定方法を提供する。

【解決手段】半導体装置は、ヒューズの切断または非切断の判定を行う半導体装置であって、多数のヒューズと、多数のヒューズのうち切断状態である切断ヒューズの数が所定の切断閾値を超える場合には、ヒューズの切断を示す切断信号を出力し、切断ヒューズの数が切断閾値よりも小さい場合には、ヒューズの非切断を示す非切断信号を出力する判定回路と、を含む。

(もっと読む)

論理回路

【課題】電源電位の供給が遮断されたときでも論理回路の切り替え状態の保持が可能で、電源投入後の論理ブロックの起動時間が短く、低消費電力化が可能な、否定論理積(NAND)回路および否定論理和(NOR)回路を容易に切り替えることができる論理回路を提供する。

【解決手段】酸化物半導体を有するトランジスタを介して、ノードへの電荷保持状態を切り替えることによって、否定論理積(NAND)回路および否定論理和(NOR)回路を容易に切り替えることができる。当該トランジスタにはワイドバンドギャップ半導体である酸化物半導体材料を用いることによって、トランジスタのオフ電流を十分に小さくできるため、ノードに保持した電荷の状態を不揮発とすることができる。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】消費電力を抑えることができる、プログラムユニットを用いた半導体装置を提供する。また、信頼性の高い、プログラムユニットを用いた半導体装置を提供する。さらに集積度の高い、プログラムユニットを用いた半導体装置を提供する。

【解決手段】PLD等のロジックセル間の接続構造を変更する機能を有する半導体回路において、ロジックセル間を接続や切断、あるいはロジックセルへの電源の供給を、オフ電流またはリーク電流が小さい絶縁ゲート電界効果型トランジスタを用いたプログラムユニットによって制御する。プログラムユニットにはトランスファーゲート回路を設けてもよい。駆動電圧を下げるため、プログラムユニットには容量素子を設けて、その電位をコンフィギュレーション時と動作期間とで異なるものとしてもよい。

(もっと読む)

半導体集積回路のチップサイズ見積もり装置、及び半導体集積回路のチップサイズ見積もり方法

【課題】精度よく簡便にチップサイズを見積もることができる、半導体集積回路のチップサイズ見積もり装置、及び半導体集積回路のチップ見積もり方法を提供する。

【解決手段】回路の機能の実現に最小限必要なゲート数である最小機能ゲート数を入力する入力部1と、セルライブラリごとに所定の動作速度の達成に必要となるゲート数と前記最小機能ゲート数との比率である性能考慮ゲート数係数が予め設定された設定値保持部21と、前記最小機能ゲート数と前記性能考慮ゲート数係数とから算出されるゲート数を用いて前記回路の総面積を見積もる計算部22と、を備えたことを特徴とする。

(もっと読む)

クロックツリー生成方法、クロックツリー生成プログラム、記録媒体、およびクロックツリー生成装置

【課題】外部電源電圧が変動した場合でも、安定に動作する半導体装置を実現することが可能なクロックツリー生成方法を提供する。

【解決手段】プログラム5のCTS部8は、電源領域Aから電源領域Bにクロック信号CLK1,CLK2を伝達する経路L1,L2を設け、電源領域A内の経路L1,L2にそれぞれアンカーバッファB1,B2を配置し、遅延回路D1,D2を電源領域B内の経路L1,L2にそれぞれ配置し、遅延回路D3,D4をアンカーバッファB1,B2の入力ノード側の経路L1,L2にそれぞれ配置する。したがって、外部電源電圧VDD1,VDD2が変動した場合でも、クロック信号CLK1,CLK2の遅延時間は同じになる。

(もっと読む)

セル・ライブラリから選択された信号スキュー調整セルを備えた集積回路

【課題】 少なくとも1つのデジタル論理セルおよび少なくとも1つのスキュー調整セルを有するデジタル回路機構を備えた集積回路を提供すること。

【解決手段】 スキュー調整セルは、集積回路のデジタル回路機構における信号のスキューを所望の量に調整するように構成される。デジタル論理セルおよびスキュー調整セルはセル・ライブラリから選択される。

(もっと読む)

回路設計検証装置および回路設計検証方法

【課題】回路シミュレーション用のネットリストに基づいて、当該回路のファンアウトを計算できるようにすること。

【解決手段】回路設計検証装置は、半導体素子レベルの回路シミュレーション用のネットリストを、論理を構成する複数の駆動回路に分割するネットリスト分割部と、前記複数の駆動回路のそれぞれに含まれるMOSトランジスタのゲート長およびゲート幅からゲートサイズを算出するゲートサイズ算出部と、前記複数の駆動回路のそれぞれによって駆動される後段の素子の負荷容量を算出する負荷容量算出部と、算出されたゲートサイズおよび算出された負荷容量に基づいて、前記複数の駆動回路のそれぞれに対するファンアウトを算出するファンアウト算出部と、を備えている。

(もっと読む)

I/O積層体を含むシステム及びこのシステムを製造する方法

【課題】入出力(I/O)積層体を含むシステムを提供する。

【解決手段】入出力(I/O)積層体を含むシステム及びこのシステムを製造する方法が記述されている。一実装において、本方法は、I/O素子を含むと共に論理素子を含まないI/Oダイを積層するステップを有する。又、一実装において、本方法は、I/Oダイに対して集積回路ダイを積層するステップを更に含む。集積回路は、論理素子を含み、且つ、I/O素子を含まない。集積回路ダイからI/Oダイを分離することにより、それぞれのダイの独立的な開発や従来のダイのものとの比較におけるI/OダイのI/O基板上のI/O素子用の相対的に大きな空間などの様々な利益が得られる。空間の増大により、多数の論理素子を集積回路ダイの基板の同一の表面積内に収容する集積回路ダイの新しいプロセス世代が可能となる。

(もっと読む)

半導体集積回路の設計方法及び半導体集積回路の設計支援装置

【課題】論理回路の面積縮小化を実現しつつ、設計TATの短縮を可能とする技術を提供する。

【解決手段】複合論理マクロセルを、基本マクロセルに置き換えて面積の総和を抽出し、その面積の総和と複合論理マクロセルの面積とを比較して面積縮小化に有効となる複合論理マクロセルを選択する。その選択された複合論理マクロセルにフラグを設定する。フラグを設定したマクロセルと同等の論理を論理情報から検索する論理構造検索処理を行い、置換対象となる基本マクロセルにフラグを設定する。置換対象のフラグを設定した基本マクロセルを、フラグ設定した複合論理マクロセルに置き換える等価論理置換処理を行う。

(もっと読む)

半導体集積回路及び電源電圧適応制御システム

【課題】フリップフロップを備える半導体集積回路において、エラーフリップフロップを効率的に検出する。

【解決手段】半導体集積回路は、冗長フリップフロップを含む複数のフリップフロップと、セレクタ部と、エラー検出部とを備える。セレクタ部は、再構成情報に応じて選択フリップフロップを選択し、入力端子に入力されたデータが選択フリップフロップのそれぞれによって出力端子に出力されるようにデータの流れを切り替える。テストモード時、フリップフロップはスキャンチェーンを構成し、そのスキャンチェーンにはスキャンデータが入力される。そして、エラー検出部は、それぞれのフリップフロップの入出力に基づいてエラーフリップフロップを検出し、当該エラーフリップフロップが選択フリップフロップから除外されるように再構成情報を作成する。

(もっと読む)

1 - 20 / 196

[ Back to top ]