Fターム[5F064EE10]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 配線パターン (7,249) | 配線幅 (593) | 電流に応じた配線幅 (112)

Fターム[5F064EE10]に分類される特許

1 - 20 / 112

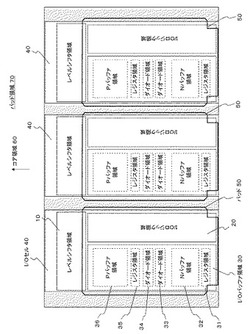

半導体集積回路装置

【課題】半導体集積回路装置において、I/Oセルの高さを低減すると同時に幅の増大を防ぐことでI/Oセルの占める領域の面積を削減すること。

【解決手段】レベルシフタ回路、I/Oロジック回路およびI/Oバッファ回路を含むI/Oセルがコア領域の周囲に配置された半導体集積回路装置であって、I/Oロジック回路が配置されたI/Oロジック領域、および、I/Oバッファ回路が配置されたI/Oバッファ領域は、I/Oセルに対するパッドが配置された領域と重なり合うとともに、コア領域の辺に平行な方向に互いに並んで配置されている。

(もっと読む)

半導体装置

【課題】配線におけるエレクトロマイグレーション耐性を向上させる。

【解決手段】ソース領域42、ソース領域44およびドレイン領域46を有するP型MOSFET40と、ソース領域52、ソース領域54およびドレイン領域56を有し、かつP型MOSFET40と隣接するN型MOSFET50と、ドレイン領域46およびドレイン領域56に接続するドレイン電極と、ドレイン電極と接続し、かつドレイン電極上に設けられた複数のビア10と、を備え、P型MOSFET40とN型MOSFET50は、インバータ回路を構成しており、ドレイン電極は、ビア10を介しては、インバータ回路の出力信号配線30と接続し、他には接続していない。

(もっと読む)

半導体集積回路の設計方法、設計プログラム

【課題】半導体集積回路の設計において、EM検証結果がNGとなる確率を低減する。

【解決手段】半導体集積回路の設計方法は、(A)設計対象回路のネットリスト中のネットに仮の寄生容量及び0個以上の仮の寄生抵抗が付加された寄生RC付きネットリストを作成するステップと、(B)寄生RC付きネットリストを用いて回路シミュレーションを行い、ネットにつながるそれぞれの素子端子の電流である素子端子電流及び仮の寄生容量の電流である寄生容量電流を算出するステップと、(C)寄生容量電流をそれぞれの素子端子に分配することによって、素子端子電流の値を変更するステップと、(D)変更後の素子端子電流に基づいて、ネットに関する配線幅制約を算出するステップと、を含む。

(もっと読む)

半導体電力増幅器

【課題】ビアホールの数を少なくしてもループ発振などの特性劣化が生じにくい半導体電力増幅器を提供する。

【解決手段】半導体電力増幅器は、ゲート電極Gと、ドレイン電極Dと、前記ゲートフィンガー電極に対向して配置されるソースフィンガー電極横手方向の両サイドに引き出される2つのソース電極Sと、を有するユニットFETと、前記ユニットFETが、前記ソース電極間を結ぶ略直線方向に複数個並列配置され、隣り合うユニットFET間に存在する2つのソース電極の両方を共通して高周波グランド面と接続する第1の接地インダクタンス値を有する第1のビアホール18Kと、隣り合うユニットFETが存在しない側のソース電極上に配置され、接地インダクタンスを等しくするために前記高周波グランド面に接続する第2の接地インダクタンス値を有する第2のビアホール18Dと、を有する。

(もっと読む)

半導体集積回路の配線設計検証方法

【課題】検証に要する時間をより短縮できる半導体集積回路の配線設計検証方法を提供する。

【解決手段】設計仕様(S7)に基づいてユーザが回路図(S8)に入力した各配線部の最大許容電流値Imaxと、電流密度Jと、配線膜厚hとを抽出し、これらに基づいて各配線部の最小配線幅情報Wmin(S12)を求める。またレイアウトのデータ(S1)から、各配線部に対応する配線経路の情報を付した配線経路ネットリスト(S4)と、各配線部について配線幅情報を付した配線幅ネットリスト(S6)とを作成し、配線経路ネットリストにおける各配線経路について各配線部の最小配線幅情報Wminを付したものと、配線幅ネットリストにおいて対応する配線部の配線幅情報とを比較して、各配線部に流れる電流が許容されている電流値以下か否かを検証する(S13)。

(もっと読む)

集積回路装置のレイアウト方法、レイアウト装置、プログラム及び情報記憶媒体

【課題】少ない工数で、短期間に集積回路装置のレイアウト設計が可能な集積回路装置のレイアウト方法、レイアウト装置、プログラム及び情報記憶媒体等を提供する。

【解決手段】マクロセルを用いた集積回路装置のレイアウト方法は、配置位置の変更が可能な第1のマクロセル又は該第1のマクロセルの第1の電源配線とチップに配置される第2の電源配線との重なりを検出する重なり検出ステップと、重なり検出ステップにおいて重なりが検出されたとき、第1の電源配線及び第2の電源配線を共有電源配線に置換する電源配線置換ステップとを含む。

(もっと読む)

半導体装置

【課題】隣接する2つのトランジスタ同士が接続された構成を有し、省スペースと電流集中による信頼性の低下の抑制とを両立させた半導体装置を実現できるようにする。

【解決手段】半導体装置は、第1のトランジスタ101と接続された第1のバス111、第2のトランジスタ102と接続された第2のバス112と、第1のバス111と第2のバス112との間に形成され、第1のバス111と第2のバス112とを接続するバス間配線121とを備えている。バス間配線121は、第1のバス111における第2のバス112と対向する辺の一部及び第2のバス112における第1のバス111と対向する辺の一部と接続されている。第1のコンタクトパッド131は、第1のバス111の一部と接続され、第2のコンタクトパッド132は、第2のバス112の一部と接続されている。

(もっと読む)

半導体装置

【課題】電源ノイズを一層効果的に解消する技術を提供する。

【解決手段】半導体装置1は、所定動作を実行するための内部回路6と、内部回路6に対して高電位電圧を供給するための電源ライン7と、内部回路6に対して低電位電圧を供給するためのグラウンドライン8と、ウェハテスト用電極パッド9と、ウェハテスト用電極パッド9を内部回路6に接続するための電気線10と、電気線10を内部回路6に対して非導通状態にすると共に、電気線10を電源ライン7とグラウンドライン8のうち何れか一方に対して選択的に導通状態とする接続切替部11と、を備える。

(もっと読む)

半導体装置

【課題】複数の電圧レベルの電源電圧が供給される入出力バッファ回路に対して、従来よりも少ない電源配線スペースで十分な電源供給を可能にする。

【解決手段】半導体装置3において、入出力バッファ回路BFは電圧レベルの変換を行なう。第1の電源配線HVLは、入出力バッファ回路BFの第1の回路部分HCと接続され、第1の回路部分HCに第1の電源電圧VCC1を供給する。第2の電源配線LVLは、入出力バッファ回路BFの第2の回路部分LCと接続され、第2の回路部分LCに第2の電源電圧VCC2を供給する。複数のスイッチ部SWは、第3の電源配線SVLに沿った複数箇所にそれぞれ設けられる。複数のスイッチ部SWの各々は、内部回路10から出力された制御信号に応じて、第1および第2の電源配線HVL,LVLのうち選択された一方の電源配線と第3の電源配線SVLとを接続する。

(もっと読む)

半導体集積回路および電源配線方法

【課題】信号配線リソースを確保しながら、チップ中心部のIRドロップを少なくすることのできる半導体集積回路および電源配線方法を提供する。

【解決手段】実施形態の半導体集積回路は、チップ内に等間隔で配線される下層電源配線1と直交する方向に所定の間隔で配線される上層電源配線が、下層電源配線との接続用のビア3が配線中央部にのみ配置された上層電源配線2Aと、配線中央部を除く領域に上層電源配線2Aへの配置個数よりも多数のビア3が配置された上層電源配線2Bとの対により構成され、上層電源配線2Aの上層電源配線2Bに対する配線幅の比が、配線中央部を除く領域では、上層電源配線2Aの上層電源配線2Bに対する供給電流比の逆数であり、配線中央部では、供給電流比の逆数よりも大きい。

(もっと読む)

レイアウト設計装置、レイアウト設計方法、及びプログラム

【課題】シミュレーションを実行することなく、最適な配線幅の取得を行えるようにすることにより、シミュレーションの複数回実行による処理時間増大を防ぐ。

【解決手段】レイアウト設計装置は、フリップチップ構造の半導体集積回路のRDL(パッド−I/O端子間)配線処理において、I/Oセルの所要電流量と配線長に適した配線幅を取得するためのテーブルをライブラリ化して保持する手段と、パッドとI/Oセルの位置関係から配線に必要な距離を算出する手段と、パッドとI/Oセル端子間の配線に必要な距離とI/Oセルの所要電流量と前記テーブルから適切な配線幅を取得する手段とを有することを特徴とする。

(もっと読む)

半導体集積回路の設計方法

【課題】 半導体集積回路の電源EM及びスタティックIRドロップの解析と電源補強設計を改善する。

【解決手段】 一つの実施形態の半導体集積回路の設計方法では、電源配線のEM解析を行い、EM解析でEMエラーが発生した場合、EMエラーとなるレイヤ及び座標をチェックしてリストを格納し、半導体集積回路の抵抗網を抽出し、EMエラーとなるレイヤ及び座標を含む抵抗セグメントを全て削除してIRドロップ値が許容値を満足するかの第1の判定を行い、記第1の判定でIRドロップ値が許容値を満足する場合、EMによって半導体集積回路が動作不良とならない抵抗セグメントをレイアウトデータから削除する。

(もっと読む)

半導体装置

【課題】 配線に対するエレクトロマイグレーションの影響を排除する点で、従来の構造は十分とはいえない。

【解決手段】 半導体基板の上に第1の配線が配置されている。半導体基板の上であって、第1の配線とは異なる高さに第2の配線が配置されている。第1のビアが、第1の配線と第2の配線とを高さ方向に接続する。第2のビアが、高さ方向に関して第1のビアとは反対側において第1の配線に接続される。第1の配線は、第1のビアとの接続点から基板面内の第1の方向に延在し、第2のビアは、第1のビアよりも第1の方向にずれた位置に配置されており、第2のビアは、高さ方向に電流を流す電流路として作用しない。

(もっと読む)

配線構造

【課題】クラックからの水分侵入に起因する金属配線端面の腐食防止、あるいは金属配線端面の腐食が生じている場合でも該腐食が液晶表示装置を駆動する液晶表示部分を構成するゲート線等の金属配線にまで到達することを防止する技術を提供する。

【解決手段】基板の上に、複数の金属配線が同一平面上に形成され、金属配線の上に絶縁膜が形成された積層構造を有し、切り出し加工により切断端面が露出している第1の金属配線を有する配線構造であって、

第1の金属配線の線幅をX(μm)、

第1の金属配線の長さをY(μm)としたとき、

(1)若しくは(2)、および/または下記(3)の要件を満足することを特徴とする配線構造。

(1)X≦20μm

(2)X>20μmのときは、Y≧10X−160、

(3)第1の金属配線の切断端面から、第1の金属配線に隣接する第2の金属配線までの間において、第1の金属配線は絶縁膜の存在しない領域Zを有する。

(もっと読む)

半導体装置の電源配線レイアウト方法及び電源配線レイアウト装置

【課題】IRドロップ違反を解消しつつ、半導体集積回路の大型化を抑制することができる半導体装置の電源配線レイアウト方法。

【解決手段】半導体集積回路の電源配線レイアウト方法。電源配線を、複数のノードと、互いに隣接するノード間に配置された複数の要素抵抗と、を含む解析モデルとしてモデル化し、回路シミュレーションにより各複数のノードにおける電圧値を求める。電圧値にIRドロップ違反がある場合、IRドロップ違反が最大となるノードへ流れ込む電流経路を探索し、複数の要素抵抗のうち、電流経路に含まれる要素抵抗からボトルネック要素抵抗を選択し、その抵抗値を変更する。

(もっと読む)

半導体装置の電源配線レイアウト方法及び電源配線レイアウト装置

【課題】基板ノイズ違反を解消しつつ、半導体集積回路の大型化を抑制することができる半導体装置の電源配線レイアウト方法。

【解決手段】アナログ回路とデジタル回路とが混載された半導体集積回路の電源配線レイアウト方法。電源配線を、複数のノードと、それぞれが互いに隣接するノード間に配置された複数の要素抵抗と、を含む解析モデルとしてモデル化し、回路シミュレーションにより各複数のノードにおける電圧値を求め、アナログ回路のノードの電圧値に基板ノイズ違反がある場合、デジタル回路のノードのうち当該アナログ回路のノードへ流れ込む電流量が最大となる最大電流ノードを探索し、デジタル回路において最大電流ノードへ流れ込む電流経路を探索し、複数の要素抵抗のうち、電流経路に含まれる要素抵抗からボトルネック要素抵抗を選択し、ボトルネック要素抵抗の抵抗値を変更する。

(もっと読む)

エレクトロマイグレーション検証装置

【課題】検証精度を高めることのできるエレクトロマイグレーション検証装置を提供する。

【解決手段】前記複数の矩形図形が段差状に接続されている部分をオフセット接続部として識別し、前記オフセット接続部を示すオフセット接続部データを生成する、識別部と、前記オフセット接続部データに基づいて、前記オフセット接続部における最小配線幅を算出し、前記最小配線幅を示す最小幅データを生成する、最小幅算出部と、前記オフセット接続部を流れる電流値と、前記最小配線幅とに基づいて、前記オフセット接続部における電流密度を算出し、算出された電流密度を示す電流密度データを生成する、電流密度算出部と、前記電流密度データに基づいて、前記電流密度を予め設定された基準値と比較し、比較結果に基づいて、エレクトロマイグレーションが発生するか否かを判定する、判定部と、を具備する。

(もっと読む)

半導体集積回路及びその制御方法

【課題】従来技術の半導体集積回路では、電源遮断領域において発生する電圧降下等を抑制することができないという問題があった。

【解決手段】本発明にかかる半導体集積回路は、高電位側電源ライン14及び低電位側電源ライン15と、部分電源ライン13a,13bと、高電位側電源ライン14と部分電源ライン13aとの間に設けられた電源スイッチSWA1〜SWAmと、部分電源ライン13aと低電位側電源ライン15との間に設けられた内部回路12aと、高電位側電源ライン14と部分電源ライン13bとの間に設けられた電源スイッチSWB1〜SWBnと、部分電源ライン13bと低電位側電源ライン15との間に設けられた内部回路12bと、部分電源ライン13a,13b間に設けられ、電源スイッチSWA1〜SWAm,SWB1〜SWBnがオンの場合にオンに制御される電源スイッチSWX1〜SWXpと、を備える。

(もっと読む)

半導体装置

【課題】電源配線やグランド配線に流れる電流の周波数が上がってもインピーダンスが上がるのを抑えられる半導体装置を提供すること。

【解決手段】トランジスタ20、21の近傍に配線された電源配線11a及びグランド配線11cを備え、電源配線11a及びグランド配線11cは、それぞれ、分割した構造となっており、所定間隔をおいて一方向に配線された複数本の分割配線11a、11cよりなる。

(もっと読む)

半導体集積回路装置

【課題】電源遮断時にそれ以前の情報を保持する低消費電力モードにおいてその復帰を高速にする。その一つに従来のデータ保持型フリップフロップを用いることが考えられるが、そのためにセルを大きくする等の面積オーバーヘッドが生じるのは望ましくない。

【解決手段】電源遮断時のデータ保持のための電源線は一般の電源幹線よりも細い配線にて形成する。望ましくは、データ保持回路の電源を信号線扱いとして、自動配置配線時に配線することである。そのために、セルにはあらかじめ上記データ保持回路用電源のための端子を通常の信号線と同様に設けて設計しておく。[効果]セルに余分な電源線のレイアウトが不要となり省面積化が図られるとともに、既存の自動配置配線ツールにより設計が可能となる。

(もっと読む)

1 - 20 / 112

[ Back to top ]