Fターム[5F064EE13]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 配線パターン (7,249) | メッシュ状、格子状配線 (332) | 格子点 (103)

Fターム[5F064EE13]に分類される特許

1 - 20 / 103

スタンダードセル、および、半導体集積回路

半導体装置の設計方法及び半導体装置の製造方法

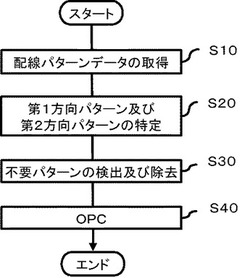

【課題】半導体装置の歩留まりが低下することを抑制する。

【解決手段】配線パターンを示す配線パターンデータを取得する(ステップS10)。次いで、配線パターンデータを解析して、第1方向パターン及び第2方向パターンを特定する(ステップS20)。第1方向パターンは、第1の方向に延伸するパターンであり、第2方向パターンは、第1の方向に直交する方向に延伸するパターンである。次いで、第1方向パターと第2方向パターンの交点を検出する。そして、この交点から延伸するパターンのうち、ビア、コンタクト及び他のパターンのいずれにも接続していないパターンを不要パターンとして検出し、検出した不要パターンを除去する(ステップS30)。そしてその後、設計した配線パターンに対して光近接効果補正を行う(ステップS40)。

(もっと読む)

半導体装置

【課題】配線間の影響を抑制することができる多層配線を有する半導体装置を実現する。

【解決手段】本発明の実施形態における半導体装置は、下層の配線層に第1の方向に沿って形成された信号配線11と、下層の配線層と絶縁膜を介して配置される上層の配線層に第1の方向と交差する第2の方向に沿って形成された基準電位配線13と、 上層の配線層に基準電位配線13に沿って近接して形成されたシールド線14a、14bと、を有し、信号配線11と基準電位配線13の交差部15cにおいて基準電位配線13とシールド線14a、14bとの距離が他の部分に比べてより狭くなっていることを特徴とする。

(もっと読む)

レイアウト設計装置、レイアウト設計方法およびレイアウト設計プログラム

【課題】マクロの全端子で配線が引き出し可能かを判定できるレイアウト設計装置、レイアウト設計方法およびレイアウト設計プログラムを提供する。

【解決手段】記憶部11は内部にマクロを含んだ多層回路の階層レイアウトの設計データを記憶する。チャネル数算出部13は設計データに基づいて、マクロの各端子から所定の配線層まで配線を引き出すために使用可能なチャネル数を端子毎に算出する。経路算出部15は算出したチャネル数の少ない端子から順に、端子から所定の配線層まで配線を引き出すための経路を算出する。経路判定部16はマクロの全ての端子について引き出し経路を算出できたか否かを判定する。

(もっと読む)

半導体装置

【課題】複数の回路ブロックの特性を正確に一致させる。

【解決手段】例えば、端子31A,31Bと、これら端子間に設けられた回路110A,110Bを備える。回路110Aは端子31Aに接続され、端子31Aから端子31Bへ向かって配置されたセル120A,130A,140Aを含む。回路110Bは端子31Bに接続され、端子31Bから端子31Aへ向かって配置されたセル120B,130B,140Bを含む。セル120A,120Bのレイアウトは、形状、サイズ及び向きがトランジスタレベルで同一である。セル130A,130B及びセル140A,140Bのレイアウトは、形状及びサイズが同一であり、トランジスタの向きが180°相違している。これにより各セルを対称配置しつつ、センシティブなセル120A,120Bにおいては電流方向の違いによる特性差が生じない。

(もっと読む)

半導体集積回路のチップサイズ見積もり装置、及び半導体集積回路のチップサイズ見積もり方法

【課題】精度よく簡便にチップサイズを見積もることができる、半導体集積回路のチップサイズ見積もり装置、及び半導体集積回路のチップ見積もり方法を提供する。

【解決手段】回路の機能の実現に最小限必要なゲート数である最小機能ゲート数を入力する入力部1と、セルライブラリごとに所定の動作速度の達成に必要となるゲート数と前記最小機能ゲート数との比率である性能考慮ゲート数係数が予め設定された設定値保持部21と、前記最小機能ゲート数と前記性能考慮ゲート数係数とから算出されるゲート数を用いて前記回路の総面積を見積もる計算部22と、を備えたことを特徴とする。

(もっと読む)

半導体装置

【課題】半導体装置の電源線および接地線の高抵抗化を抑制する。

【解決手段】第1の方向に延伸された第1の回路セル列及び第2の回路セル列と、第1の方向に延伸され、第1の回路セル列上に配置され、第1の電源線には第1の電源電位が供給される、第1及び第2の電源線と、第1の方向に延伸され、第2の回路セル列上に配置され、第2の電源電位が供給される第3の電源線と、第2の電源線と第3の電源線との間に接続され、導通状態において第2の電源線と第3の電源線とを接続して第3の電源線から第2の電源線に第2の電源電位を供給し、非導通状態において第2の電源線と第3の電源線とを電気的に切り離す第1のトランジスタと、第1の回路セル列に配置され、第1の電源線から供給される第1の電源電位と第2の電源線から供給される第2の電源電位との間の電源電圧で動作する第1の回路素子とを備える。

(もっと読む)

不揮発プログラマブルロジックスイッチ

【課題】 誤動作を防ぐとともに、サイズが小さい不揮発プログラマブルロジックスイッチを提供すること。

【解決手段】 本発明の実施形態による不揮発プログラマブルロジックスイッチは、制御ゲートが第1の配線に接続され、第1のソースドレイン端が第2の配線に接続され、電荷を蓄積する膜を有する第1のメモリセルトランジスタと、制御ゲートが前記第1の配線に接続され、第3のソースドレイン端が前記第1のメモリセルトランジスタの第2のソースドレイン端に接続され、第4のソースドレイン端が第3の配線に接続され、電荷を蓄積する膜を有する第2のメモリセルトランジスタと、前記第1のメモリセルトランジスタの前記第2のソースドレイン端と前記第2のメモリセルトランジスタの前記第3のソースドレイン端にゲート電極が接続されたパストランジスタと、前記パストランジスタのウェルに基板電圧を印加する第1の基板電極を有する。

(もっと読む)

可変遅延回路およびその制御方法

【課題】信号の遅延量を微調整可能な可変遅延回路を提供する。

【解決手段】可変遅延回路において、N個の可変論理回路を用いてN段のセレクタが直列接続される。1段目のセレクタSL1の2つの入力端子に信号が入力される際、入力信号が通過する2つの信号経路D1には経路差d1が存在している。また、2段目のセレクタSL2の2つの入力端子に信号が入力される際、入力信号が通過する2つの信号経路D2には、経路差d2が存在している。信号が通過する当該経路の組み合わせは、セレクタSLの段数に基づき、N段であるため2nとおりの信号経路の組み合わせが生じる。すなわち、2nとおりの切替信号R1〜Rnの組み合わせに基づいて2nとおりの信号経路が選択される。2nとおりの信号経路の組み合わせに基づく配線経路差に基づいて信号遅延量を調節する。

(もっと読む)

半導体集積回路のレイアウト設計方法、レイアウト設計装置及びレイアウト設計プログラム

【課題】長さが均一で直線的な配線を配置することができる半導体集積回路のレイアウト設計方法、レイアウト設計装置及びレイアウト設計プログラムを提供すること。

【解決手段】半導体集積回路のレイアウト設計方法は、第1の配線ピッチで配線を行う高速配線処理と、第1の配線ピッチより狭い第2の配線ピッチで配線を行う通常配線処理と、を有する。高速配線処理は、所定の高速バス配線上の複数のネットを第1の配線ピッチで略平行、かつ、略等長となるように自動配線を行う。通常配線処理は、高速配線処理より前に実行されない。

(もっと読む)

集積回路デバイス

【課題】プロセス寸法の縮小に伴う光相互作用の予測品質の低下を抑止する。

【解決手段】ゲートレベル仮想格子の、連続的に隣接して配置された少なくとも3本の仮想ラインのそれぞれは、その上に定義された少なくとも1つの線形導電体形状を有し、ゲートレベル仮想格子の少なくとも3本の仮想ラインの第1の仮想ラインは、その上に定義され、第1の終端−終端間スペーシングで分離された2つの線形導電体セグメントを有し、ゲートレベル仮想格子の少なくとも3本の仮想ラインの第2の仮想ラインは、その上に定義され、第2の終端−終端間スペーシングで分離された他の2つの線形導電体セグメントを有し、第1の仮想ラインに沿って測定された第1の終端−終端間スペーシングの寸法は、第2の仮想ラインに沿って測定された第2の終端−終端間スペーシングの寸法に等しく、ゲートレベル仮想格子の仮想ラインは、いかなる導電体形状によっても占有されない。

(もっと読む)

半導体集積回路のレイアウト設計方法

【課題】半導体集積回路のレイアウト設計において、幅が広い第1の配線と幅が狭い第2の配線との間に無駄なスペースが発生することによる配線性の悪さを改善する。

【解決手段】このレイアウト設計方法は、回路情報に基づいて、レイアウト領域において複数の横ラインと複数の縦ラインとが交差する格子点上に、複数の回路素子の接続点を配置するステップ(a)と、回路情報及び複数の回路素子の配置に基づいて、いずれかの横ライン又は縦ラインの位置を始点として、第1の方向に格子間隔よりも大きい所定の幅を有する第1の配線を配置するステップ(b)と、ステップ(b)において配置された第1の配線に第1の方向と反対の第2の方向において隣接する横ライン又は縦ライン上に、最小幅を有する第2の配線を配置するステップ(c)とを含む。

(もっと読む)

配線基板の配線経路決定方法及び半導体装置の配線経路決定方法

【課題】設計時間とコンピュータ資源の消費とを抑えつつ、配線性を向上させることができる配線方法を提供する。

【解決手段】始点から、第1の配線形成用格子を連続的になぞって、複数の第1の交点のうちから選択された1つの第1の選択済交点まで、追加配線を伸ばすステップと、設計済配線及び設計済ビアの位置に基づいて、第1の配線層上に追加ビアを配置することができる第1のビア配置可能領域と、第2の配線層上に追加ビアを配置することができる第2のビア配置可能領域とを算出するステップと、第1の選択済交点を下面の領域内のいずれかの位置に含む追加ビアを、下面が第1のビア配置可能領域に含まれ、且つ、上面が第2のビア配置可能領域に含まれるように配置するステップと、追加ビアから、第2の配線形成用格子を連続的になぞって、終点まで追加配線を伸ばすステップとを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】プロセスマージンを大きく取れる配線配置構造を提供する。

【解決手段】基板上に形成された複数の第1配線6を含む第1配線層と、第1配線層上に形成され、第1配線6に接続された複数のビアコンタクト10を含むコンタクト層と、コンタクト層上に形成され、ビアコンタクト10に接続された複数の第2配線14を含む第2配線層とを備える半導体装置において、コンタクトピッチは、第1配線6の最小配線ピッチ、又は、第2配線14の最小配線ピッチ、よりも大きくなるようにする。

(もっと読む)

半導体集積回路設計装置、半導体集積回路設計方法及びプログラム

【課題】メガマクロブロックとの重なりが少ないクロック構造を広い解空間において効率良く探索できるようにすること。

【解決手段】チップ情報に含まれるチップ領域を覆う格子を設定する格子設定部と、チップ領域の中心から格子の各セルの中心へクロック信号を分配するクロック構造であってチップ領域を格子に含まれるセルの境界に沿って縦方向又は横方向に2分割することを再帰的に繰り返すことにより生成されたクロック構造を構成する線分の候補を候補線分として生成する候補線分生成部と、チップ領域の分割方向及び分割順序を節点及び枝として有する2分木を生成する2分木生成部と、候補線分に設定された重みの総和である目的関数が最小となるように2分木の各節点の分割方向を選択する分割方向選択部と、各節点の分割方向が選択された2分木によって表されるクロック構造を生成するクロック構造生成部と、を有する。

(もっと読む)

半導体回路の設計装置および設計方法

【課題】配線のしやすさを損なうことなく、ビアの不良による歩留まりの低下を抑制可能な半導体回路の設計装置および設計方法を提供する。

【解決手段】半導体回路の設計方法は、論理回路を構成するセルの配置およびセル間の配線を行い、複数箇所にビアが設けられる配線を含むレイアウトパターンを生成するステップ(ステップS1、S2)と、ビアから、配線上の信号を受信するレシーバセルまでの負荷容量をビア毎に算出するステップ(ステップS4)と、ビアごとの、負荷容量に基づいて、負荷容量が大きいビアを優先的に低抵抗のビアに置換するステップ(ステップS6、S7)を備える。

(もっと読む)

半導体集積回路、半導体集積回路の設計方法及びプログラム

【課題】半導体集積回路において、シールド配線を配置することで配線間のクロストークの影響を削減するとともに、配置したシールド配線の電位を安定化させること。

【解決手段】半導体集積回路の設計方法は、コンピュータが、半導体集積回路の配線パターンにおいて、配置済の信号配線に対して複数のシールド配線を配置する工程と、前記複数のシールド配線のそれぞれを電源配線に接続する工程と、前記複数のシールド配線を相互に接続する工程と、前記複数のシールド配線のうちの電源配線に接続されていないものを除去する工程と、を含む。

(もっと読む)

半導体集積回路のレイアウト装置及びレイアウト方法

【課題】集積度の高い半導体集積回路の場合でもレイアウト設計における配線に係る時間を短縮する。

【解決手段】半導体集積回路のレイアウト方法は、回路構成要素の配置された領域へ配線を実施後に、予め設定された条件よりも配線が混雑する配線混雑箇所を抽出するステップと、配線混雑箇所を含む領域に、配線の実施が禁止される複数の配線禁止領域を生成するステップと、複数の配線禁止領域を迂回して配線を実施するステップと、迂回して配線を実施した後に、複数の配線禁止領域を削除するステップと、複数の配線禁止領域を削除した後に、再配線を実施するステップとを具備する。複数の配線禁止領域を生成するステップは、配線層毎に、配線の混雑に対応した領域内に配線禁止領域を発生させる割合に基づいて、複数の配線禁止領域の大きさ及び間隔を算出するステップと、算出結果に基づいて、領域に複数の配線禁止領域を生成するステップとを備える。

(もっと読む)

プログラマブル論理集積回路

【課題】 異なったLVTTL I/O規格に対して互換性を持つように集積回路の各I/Oを個別に再構成する回路を提供する。

【解決手段】 上述課題は1つのI/O電源電圧のみを用いて達成でき、この電圧は特定の用途に要求されるI/O電圧のうち最も高いものである。回路はI/Oセルの出力電圧を、適合されるべきLVTTL規格のVOHよりも高く最高VIHよりも低くなるように調節することによって動作する。I/Oセルは、I/O電源電圧とパッドの間に接続されるプルアップトランジスタと、該パッドの電圧と対応の規格に応じた基準電圧とを差動増幅する差動増幅器と、差動増幅器の出力信号と出力制御信号とにプルアップトランジスタを選択的にオン状態とするロジックゲートを備える。各I/Oセルは別個に再構成可能であるため、任意のI/Oを任意のLVTTL仕様に適合させることができる。

(もっと読む)

自動配置配線方法及び自動配置配線プログラム

【課題】配線リソースを確保した上で、マクロ間隔を最小にすることができる自動配置配線方法及び自動配置配線プログラムを提供する。

【解決手段】マクロ3、4の配置、セル5、6、7、8の配置及び配線のレイアウトを自動で行う自動配置配線方法であって、マクロ3、4及びセル5、6、7、8の配置及び配線のレイアウトを行った後、マクロ3とマクロ4との間のスリット状の処理領域9内の配線グリッドの交点の数と処理領域9内において必要な配線リソースとに基づいて、マクロ3とマクロ4とのマクロ間隔を算出し、当該マクロ間隔を満たすように、マクロ3とマクロ4との少なくとも一方を移動させる自動配置配線方法。

(もっと読む)

1 - 20 / 103

[ Back to top ]