Fターム[5F064HH07]の内容

ICの設計・製造(配線設計等) (42,086) | 設計、製造における計算機技術 (6,629) | ソフトウェア(プログラム)関係 (5,214) | CAD (1,938) | 対話式 (93)

Fターム[5F064HH07]に分類される特許

1 - 20 / 93

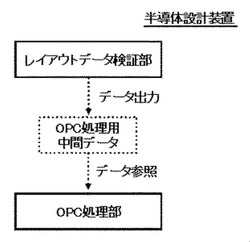

半導体設計装置、半導体設計方法及びプログラム

【課題】レイアウトデータの検証を行うLVS処理やDRC処理と、OPC処理には、プログラムの実装に重複(冗長)な処理が存在する。そこで、これらの処理を、統合することも考えられる。しかし、そのような統合を実際に行えば、プログラムの変更が大規模になり、半導体設計装置のコストを上昇させてしまう。そのため、既存のリソースを有効活用しつつ、OPC処理の処理スピードを向上させた半導体設計装置が、望まれる。

【解決手段】半導体設計装置は、半導体集積回路のレイアウトデータの検証を行うレイアウトデータ検証部と、レイアウトデータ検証部が生成するOPC処理用中間データを用いて、OPC処理を行うOPC処理部と、を備えている。

(もっと読む)

テスト回路、集積回路、及び、テスト回路のレイアウト方法

【課題】 より簡易な設計手法で作製可能なテスト回路を提供する。

【解決手段】 テスト回路100は、基板と、基板上に形成された配線部及び被試験デバイス部10とを備える構成とする。テスト回路100では、被試験デバイス本体のパターン形成面内における回転中心位置Oと複数の接続電極13a〜13dのそれぞれとを結ぶ直線L1の延在方向が、配線21の延在方向に対して所定の角度で傾いている。さらに、被試験デバイス本体及び複数の接続電極13a〜13dをパターン形成面内で90度回転させた際にも、複数の接続電極13a〜13d及び複数の配線21〜24間の接続が維持されるような位置に複数の接続電極13a〜13dが配置される。

(もっと読む)

半導体装置の設計支援装置、設計支援プログラム及びレイアウト情報生成方法

【課題】従来の設計支援装置により生成したインダクタは、周囲の回路の影響により特性ずれが生じる問題があった。

【解決手段】本発明の設計支援装置は、生成対象のインダクタに接続される接続対象回路領域の第1、第2の接続端子の位置情報を回路設計情報から生成されるフロアプラン結果から得て、インダクタを他の回路と接続する第3、第4の接続端子を、第1の接続端子と第3の接続端子との間及び第2の接続端子と第4の接続端子との間が最短の配線によって接続可能な位置に設定する端子位置設定部10と、第3、第4の接続端子の位置を基準としてインダクタの配線パターンを生成し、当該配線パターンに基づきインダクタのレイアウト情報を生成するパターン生成部13と、を有する。

(もっと読む)

クロック経路抽出装置

【課題】タイミング検証におけるクロック系統の解析時間を短縮することのできるクロック経路抽出装置を提供する。

【解決手段】実施形態のクロック経路抽出装置1は、クロック経路探索部11が、RTL記述データ100を解析し、指定されたモジュールのクロック端子からクロック生成起点までのクロック経路を探索し、クロック経路抽出部12が、クロック制御情報200にもとづいて無効クロック経路を除外し、有効クロック経路のみを抽出する。さらに、クロック系統図生成部13が、クロック生成起点のクロック周波数情報300にもとづいて、クロック周波数が同一である有効クロック経路を有する複数のモジュールを、クロック周波数ごとに1つのブロックに集約し、そのブロックおよびクロック生成起点をそれぞれ図形で表し、その図形間を1本のクロック線で結んだクロック系統図を生成する。

(もっと読む)

設計支援装置及び設計支援方法

【課題】設計効率の向上を図ること。

【解決手段】設計支援装置10は、既存の半導体集積回路に含まれる機能マクロの情報と、機能マクロ間の接続情報を含むアーキテクチャ情報が品種毎に管理されたデータベースから、作成する半導体集積回路に搭載する機能マクロを含む品種を検索する。そして、設計支援装置10は、検索により得られた品種のアーキテクチャ情報を前記データベースから抽出し、作成する半導体集積回路のアーキテクチャ情報と、抽出した前記品種のアーキテクチャ情報を比較し、設計する半導体集積回路のアーキテクチャ情報に類似するアーキテクチャ情報の品種を抽出する。

(もっと読む)

設計支援装置、制御方法および制御プログラム

【課題】配線の効率化を図ること。

【解決手段】設計支援装置1は、表示部2に接続されており、記憶部1aと、選択部1bと、配置部1cと、判断部1dと、配線部1eと、確定部1fとを有している。記憶部1aは、回路の論理接続情報と配置対象のセルのセル情報を記憶する。選択部1bは、記憶部1aに記憶されたセル情報のうち、配置対象のセルのセル情報を選択する。配置部1cは、入力された座標に基づき、選択されたセル情報のセルの仮の配置を行う。判断部1dは、配線モードであるか否かを判断する。配線部1eは、判断部1dが配線モードであると判断した場合、仮の配置がされたセルに接続する配線について仮の配線を行う。確定部1fは、セルの配置位置の確定に基づいて、配線されたセルの仮の配線の配置位置を確定する。

(もっと読む)

遅延解析プログラム,遅延解析装置および遅延解析方法

【課題】多入力セルにおいて同時スイッチングが発生している可能性の有無を高速に判定し、同時スイッチングを考慮した遅延要因の解析を高精度かつ高速に行なえるようにする。

【解決手段】遅延試験時に信号が伝播した活性化パスが複数存在する場合、抽出部11により2以上の活性化パスが入力されている多入力セルが抽出される。抽出された多入力セルについて、判定部12により、2以上の活性化パスにおける各信号の多入力セルへの入力タイミングに基づき、多入力セルにおいて同時スイッチングが発生している可能性の有無が判定される。そして、解析部13により、判定部12による判定結果および遅延試験の結果に基づき、同時スイッチングの発生状況が遅延要因の一つとして解析される。

(もっと読む)

フロアプランデータ生成装置及び方法

【課題】チップの設計期間を短縮する。

【解決手段】CPU1は、設計対象の回路を構成するセルのうち、所定のサイズより大きいセルサイズを有するセルのみの回路情報をゲートレベルで記述した簡易ネットリスト43と、所定のサイズより大きいセルサイズを有するセルのみの仕様データを含むセルリスト44とを用いてフロアプランを行い、仮フロアプランデータ47を生成する。CPU1は、ユーザによって回路全体のフロアプランが行われるときに、回路を構成するセルの仕様データである全体ライブラリ42と、回路を構成するセルの回路情報をゲートレベルで記述した全体ネットリスト45と、仮フロアプランデータ47と、簡易ネットリスト43を全体ネットリスト45に整合させるためのセルリスト44とを出力する。

(もっと読む)

半導体装置の製造方法

【課題】 ソース領域側だけに不活性イオン注入領域が形成される非対称型SOI電界効果トランジスタを容易に実現する半導体装置の製造方法を提供する。

【解決手段】 イオン注入前にトランジスタが形成される半導体層のゲート電極について対称構造をなす2つの電極のいずれか一方をソース又はドレインとして指定する電極指定データを予め保持する設計工程と、電極指定データに応じてソース領域側だけのイオン注入を可能にするためのイオン注入用マスクを製作するマスク製作工程と、対称をなす2つの電極を有する半導体層表面にフォトレジストを塗布しイオン注入用マスクを用いて露光してフォトレジストの少なくともソース領域に対応する部分を除去するレジスト形成工程と、レジスト形成工程の実行後、イオン注入用マスクに対応して残されたフォトレジストを有する半導体層表面からイオンを注入する工程と、を備える。

(もっと読む)

T−コイル回路網設計を生成する方法およびT−コイル回路網

T−コイル回路網を備える回路設計を生成する方法の1つの実施形態は、インダクタのインダクタンスおよびT−コイル回路網の寄生ブリッジ容量を決定するステップ(305−340)を含み得る。寄生ブリッジ容量は、T−コイル回路網の出力に結合された負荷の寄生容量に依存する負荷容量基準と比較され得る(345,355)。T−コイル回路網の出力に結合された回路設計の静電放電(ESD)保護の量、または、T−コイル回路網のインダクタのパラメータが、寄生ブリッジ容量と負荷容量基準との比較に従って、選択的に調整され得る(350,360)。インダクタのインダクタンスと、静電放電保護の量と、インダクタの巻線の幅とを特定可能な回路設計が出力され得る(365)。  (もっと読む)

(もっと読む)

レイアウト検証方法及びレイアウト検証装置

【課題】レイアウトデータのシールドについて精度良く検証する検証装置を提供すること。

【解決手段】検証装置は、レイアウトデータ30の被シールド配線パターンに対して検索領域を設定する。検証装置は、検証領域において、被シールド配線パターン、シールド配線パターン及びその他配線パターンを除く領域に複数の矩形領域を設定する。検証装置は、複数の矩形領域のうち被シールド配線パターンに接触する矩形領域を基にして、矩形領域を合成して合成領域を生成する。検証装置は、合成領域と接触するシールド配線パターン及びその他の配線パターンの情報に基づいて、抽出結果データDeを生成する。検証装置は、生成した抽出結果データDe及び制御カード21に基づいて、レイアウトデータ30のシールドが正常に行われているかを判定する。

(もっと読む)

設計支援装置、設計支援方法及び設計支援プログラム

【課題】設計支援装置、設計支援方法及び設計支援プログラムにおいて、LSIの配線の解析及び設計変更を容易に行うことを目的とする。

【解決手段】半導体装置の物理設計を行う設計支援装置において、表示装置と、配線を前記表示装置に表示する際に、各配線の消費電力に関する要素に基づく強調表示と、各配線の設計変更の難易度に関する要素に基づく強調表示の少なくとも一方を前記表示装置に表示させる演算処理装置を備えるようにする。

(もっと読む)

設計支援プログラム、設計支援装置、および設計支援方法

【課題】クロックゲーティング回路の配置位置に依存しない適切なクロックパスを配線し、クロックスキューの調整の容易化を図ること。

【解決手段】設計支援装置400は、第1のレイアウトデータ200の中から選択されたクロックゲーティング回路の出力先FFを特定部401により特定し、クロックゲーティング回路が削除されてクロックツリーが構築された第2のレイアウトデータ410を取得部402により取得し、第2のレイアウトデータ410内の特定されたFFごとに、FFの出力元のクロックバッファを探索部405により探索し、特定されたFFの中から探索されたクロックバッファごとに出力先FF群を選択部406により選択し、FF群ごとにクロックバッファの配置位置情報を出力部407により出力する。

(もっと読む)

半導体集積回路の設計装置および設計方法

【課題】総和電流と瞬時電流とを共に低減可能な半導体集積回路の設計装置および半導体集積回路の設計方法を提供する。

【解決手段】半導体集積回路の設計装置は、配置部1と、タイミング解析部2と、クロックライン配線部3と、ロジック配線部4と、ライブラリ5と、設定値取得部6とを備えている。タイミング解析部2が、各フリップフロップF0〜Fnのタイミングウィンドウを算出し、タイミングウィンドウに基づいて各フリップフロップF0〜Fnを駆動するクロックの遅延時間を適切に設定するため、半導体集積回路の総和電流および瞬時電流の少なくとも一方を必要に応じて低減できる。また、ユーザの設定に応じて、総和電流または瞬時電流のいずれかを特に優先して低減させることも可能である。

(もっと読む)

半導体集積回路装置の設計方法およびプログラム

【課題】タイミング検証における収束時間を短くしてレイアウト設計の効率化を図る。

【解決手段】ハードマクロとハードマクロを跨ぐ通過用配線とを含み、ハードマクロ内に含まれる複数の交点セル配置領域に関し、通過用配線が交点セル配置領域間を繋ぐ第1の配線と交点セル配置領域内を第1の配線に接続可能となるように繋ぐ第2の配線とを含んで構成される半導体集積回路装置における設計方法である。この設計方法は、全ての交点セル配置領域に関して第1の配線のみを配線した場合(図7のステップS23)のハードマクロにおける第1のタイミング検証を行うステップ(図7のS25)と、全ての交点セル配置領域に関して第2の配線を第1の配線に最大限接続するようにさらに配線した場合(図7のステップS26)のハードマクロにおける第2のタイミング検証を行うステップ(図7のS27)と、を含む。

(もっと読む)

半導体集積回路におけるセルデータ生成方法、及び、半導体集積回路の設計方法

【課題】基本セルから変更セルに置き換える場合、変更セルの周囲のセルや配線も考慮して半導体集積回路を設計すること。

【解決手段】本発明では、基本セルを表すデータ、及び、基本セルとは論理が異なるセル群を表すデータを生成する(S11)。ここで、セル群の外形及び配線パターンの位置は、基本セルの外形及び配線パターンの位置と同一である。基本セルの配線パターン、及び、セル群の配線パターンは、通過配線を禁止する領域(OBS;Obstruction)を表す通過配線禁止部を含んでいる。設計変更が行われるときに、前記基本セルは、セル群のうちの、設計変更に対応する変更セルに置き換えられる。次に、基本セルを表すデータ、及び、セル群を表すデータをライブラリ20に格納する(S12)。

(もっと読む)

レイアウト検証装置、レイアウト装置、レイアウト検証方法、レイアウト検証プログラム、及び配線形成方法

【課題】シミュレーション結果に基づいて不良部分を検出する手法を用いた場合であっても、端子の位置を固定したまま配置配線データの修正を可能とする。

【解決手段】プリミティブセル群と前記プリミティブセル群に接続される接続配線との位置を示す配置配線データに基づいて、マスクに描かれるマスクパターンを示すマスクデータを取得し、前記マスクデータに基づいて前記マスクパターンの位置を検証し、エラー部分を検出する検証手段と、前記エラー部分に基づいて修正ヒント情報を生成し、前記配置配線データを修正する配置配線手段に対して前記修正ヒント情報を通知する修正ヒント作成手段とを具備し、前記修正ヒント作成手段は、前記プリミティブセル群に含まれる端子群の位置を示す端子情報を取得し、前記端子情報に基づいて、前記端子の位置が前記配置配線手段により変更されないように、前記修正ヒント情報を生成する。

(もっと読む)

レイアウト設計方法および半導体集積回路

【課題】パッド律則とコア律則を意識しないレイアウト設計を容易に実現し、半導体集積回路の面積の縮小化とコストの低減化を図ること。

【解決手段】レイアウト設計装置300は、設計対象回路の回路情報の入力を入力部301により受け付け、入力された回路情報に含まれているコアの領域が確保された設計対象回路のレイアウト情報を生成部302が生成する。生成されたレイアウト情報上のコアの領域以外の領域に、回路情報に含まれているI/O回路をレイアウト部303により配置および配線する。回路情報に含まれているパッドの配置可能領域を決定部308により作成したレイアウト情報上に決定する。必要配置数分のパッドの総面積が配置可能領域の面積を超えない最大の大きさに、パッドの面積を最適化部309により最適化する。最適化されたパッドを配置部310により配置可能領域に配置する。

(もっと読む)

配線パターン生成装置、配線パターン生成プログラム、および、半導体装置の製造方法

【課題】限られた大きさの配線領域であっても、当該配線領域の形状とパッド位置との関係を考慮することで、当該配線領域に対する配線パターンの自動生成を良好に行えるようにする。

【解決手段】配線パターンを自動生成に必要な情報を取得する情報取得手段4aと、前記情報取得手段4aが取得した各情報を基に、接続対応関係にあるパッド同士の位置関係によって、前記各パッドを複数のパッド群にグループ分けするグループ分け手段4bと、前記グループ分け手段4bがグループ分けした複数のパッド群についての処理優先順を決定する優先順決定手段4cと、前記優先順決定手段4cが決定した処理優先順に従いつつ、前記パッド群毎に個別に、当該パッド群で接続対応関係にあるパッド同士の間を導通させる配線のレイアウトパターンを決定する配線処理手段4dと、を備えて配線パターン生成装置を構成する。

(もっと読む)

配線パターン生成装置、配線パターン生成プログラム、および、半導体装置の製造方法

【課題】配線のレイアウトパターンを決定する際の処理モードを適宜選択し得るようにして、配線パターンの自動生成を良好に行えるようにする。

【解決手段】配線パターンを自動生成に必要な情報を取得する情報取得手段4aと、前記情報取得手段4aが取得した各情報に基づき、接続対応関係にあるパッド同士の間を導通させる配線のレイアウトパターンを決定するとともに、当該レイアウトパターンの決定を予め規定された互いに異なる複数の処理モードのいずれかに対応して行う配線処理手段4bと、前記配線処理手段4bが対応する処理モードを選択し、その選択結果を前記配線処理手段4bに指示するモード選択手段4cと、を備えて配線パターン生成装置を構成する。

(もっと読む)

1 - 20 / 93

[ Back to top ]