Fターム[5F067AA02]の内容

IC用リードフレーム (9,412) | 目的、効果 (1,630) | 積層化、素子の相互接続 (75)

Fターム[5F067AA02]に分類される特許

1 - 20 / 75

半導体装置およびその製造方法

【課題】第1リードフレームと第2リードフレームとの間に搭載部品が3個のみ挟み込まれてなる半導体装置において、第1〜第3搭載部品と第2リードフレームとが未接合となることを抑制することができる半導体装置およびその製造方法を提供する。

【解決手段】搭載部品30〜50におけるはんだ31〜51、35〜55が配置される部位の中心を搭載部品30〜50の中心点30a〜50aとしたとき、3個の搭載部品30〜50のそれぞれの中心点30a〜50aを結ぶ線分にて三角形100が構成される状態で3個の搭載部品30〜50を挟み込む。

(もっと読む)

マルチチップ用複合リードフレーム及び半導体装置

【課題】リードフレーム中心部の上下に半導体チップを搭載する複合リードフレーム構造において、金属基板と有機材料基板という異質な2種類の支持基板のリードを接合する際に予め必要となる事前処理や種々の不都合の排除を目的としたもので、マルチチップ対応の新規な複合リードフレームの構造の提供することを目的とした。

【解決手段】リードフレーム中心部の上下に異なる半導体チップを搭載するためのリードフレーム1であって、少なくとも、一方の半導体チップに対応するための該半導体チップに向かうインナーリード群11と、別の半導体チップに対応するための該半導体チップに向かうインナーリード群12と、前記いずれかのインナーリード群の端部に固定されて支持される絶縁性樹脂シート14からなる半導体チップ用アイランドと、を備えることを特徴とするマルチチップ用複合リードフレームである。

(もっと読む)

半導体装置およびその製造方法

【課題】厚み寸法の増大を抑えつつ平面寸法を小さくした半導体装置およびその製造方法を提供することを課題とする。

【解決手段】半導体装置10は、リードフレームRMの主面側MFに搭載された回路素子Dと、リードフレームRMの裏面側BFに搭載されたインダクタ12と、回路素子Dおよびインダクタ12を樹脂封止する樹脂体14と、を備えている。回路素子Dには、モノリシック集積回路であるMIC18が含まれる。

(もっと読む)

導体部の短絡防止構造

【課題】溶接の際に発生する溶接スパッタによる導体部の短絡を防止することができる導体部の短絡防止構造を提供する。

【解決手段】モールド本体3には、複数の導体2の一部分を露出させるとともに、複数の導体2の露出部分と溶接される複数の接続導体4aを有する搭載部品4の少なくとも一部を収容するための部品収容部3aが形成されている。溶接の際に飛散する溶接スパッタを落下させる開口部3cが部品収容部3aに貫通して形成されている。

(もっと読む)

パワー素子パッケージモジュール及びその製造方法

【課題】パワー部及び制御部に対して、別々に1次パッケージング工程を施してから、両パッケージを連結して単一のパワーモジュールとして形成する。

【解決手段】第1の基板11上に、第1のリードプレーム13と該第1のリードプレーム13と通電される制御チップ15とが実装され、第1の基板11に制御チップ15と通電される第1の結合部11a、13aが形成され、第1の結合部11a、13aと第1のリードフレーム13の外部連結部とが外部へ露出するように個別にモールド形成された制御ユニット10と、第2の基板31上に、第2のリードフレーム33と該第2のリードフレーム33と通電されるパワーチップ35とが実装され、第2の基板31にパワーチップ35と通電される第2の結合部31a、33a、33bが形成され、第2の結合部31a、33a、33bと第2のリードフレーム33の外部連結部とが外部へ露出するように個別にモールド形成されたパワーユニット30とを含む。

(もっと読む)

積層された集積回路を有する集積回路パッケージおよびそのための方法

【課題】集積回路パッケージ内に集積回路チップを積層する改良された方法を提供する。

【解決手段】改良された方法は、集積回路パッケージ内の集積回路密度を増大することを可能にしつつ、得られる集積回路パッケージは薄く、かつ低プロファイルである。これら改良された方法は、特に集積回路パッケージ内で同一サイズ(かつしばしば同一機能)の集積回路チップを積層するために特に有用である。そのような集積回路パッケージの一例は、リードフレームの片側面または両側面上に積層された複数の類似のサイズのメモリ記憶集積回路チップを備える不揮発性メモリ集積回路パッケージである。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】電気的特性がより向上した半導体装置の製造方法を提供すること。

【解決手段】封止金型5内で、第一の半導体素子1が搭載された第一の金属基板2の一部に、第二の半導体素子3が搭載された第二の金属基板4の一部を、接合材料6を介して押圧しつつ、封止金型5内にモールド樹脂10を充填させる充填工程と、モールド樹脂10を硬化するとともに、接合材料6を用いて第一の金属基板2の一部20と第二の金属基板4の一部41の間を接合する硬化接合工程とを備えた、半導体装置の製造方法である。

(もっと読む)

半導体装置及びその製造方法

【課題】体格の小型化を図るとともに、より確実に半導体チップ間の電位干渉を抑制しつつ製造工程を簡素化することのできる半導体装置及びその製造方法を提供する。

【解決手段】各ダイパッド(21,31)の一面上に、対応する半導体チップ(23,33)を搭載してなる構造体(11,12)の準備工程と、ダイパッド(21,31)が対向するようにリードフレーム(20,30)を保持した状態で、金型(100,101)内に樹脂を注入するモールド成形工程と、モールド成形工程後、タイバー(25,35)を除去する除去工程を備える。モールド成形工程では、対向方向において、第1半導体チップ(23)と第2半導体チップ(33)の間に電位干渉を生じない間隔を確保すべく所定厚さを有するスペーサ(14)を介して、第1リードフレーム(20)及び第2リードフレーム(30)を積層配置する。

(もっと読む)

半導体装置

【課題】電極端子とダイパッドとの接触を防止するとともに、電極端子にワイヤボンディングを確実に行うことができる。

【解決手段】受動部品15は、電極端子16、16の上下方向の高さが、素体部17の高さよりも高く形成されている。より詳しくは、電極端子16、16の断面積は、素体部17の断面積よりも若干大きく形成されている。これにより電極端子16、16の上部および下部が、素体部17よりも若干高くなるように(はみだすように)位置している。受動部品15は、素体部17が接着剤33を介して高位部28に基板面と略平行になるように固着されており、電極端子16、16の一部(下端部)は、凹部27、27内の空間にそれぞれ位置する。これにより、電極端子16、16とダイパッド21との間に所定の間隙が形成されている。

(もっと読む)

リードフレームおよび電子装置の製造方法

【課題】複数のリードフレームを備えた集合体を形成する場合、リードフレームのリード形状・配置が異なった場合、それぞれに対応したリードフレームを割り当てることが必要となる。そのため、例えば4種類のリードフレームを形成するには、4回の独立した製造工程を行うことが必要となる。そのため、リードフレームを形成するためのマスクも4種類必要となり、コスト的にも不利になるという課題がある。

【解決手段】基板90と、基板90の第1の領域121に形成された第1のリード群101からなる第1のリードパターンと、基板90の第2の領域122に形成された第2のリード群102からなる第2のリードパターンとを含み、前記第1のリードパターンと前記第2のリードパターンは異なる構成とした。これにより一枚の基板に複数のリードパターンを備えるリードフレームが可能となり、課題を解決できる。

(もっと読む)

半導体装置およびその製造方法

【課題】従来の半導体装置では、パッケージの平面サイズを縮小し、実装強度を向上させ難いという問題があった。

【解決手段】本発明の半導体装置では、アイランド7上に半導体素子10が固着され、アイランド7はリード4よりも樹脂パッケージ2の表面5側に配置される。そして、リード4の一部は、アイランド7や半導体素子10の下方に交差するように配置され、樹脂パッケージ2の裏面3側から露出する。この構造により、露出したリード4は、実装領域として用いられ、樹脂パッケージ2の平面サイズは縮小され、実装強度が向上される。

(もっと読む)

電子デバイスの製造方法およびリードフレーム

【課題】複数のリードフレームを重ねて用いる樹脂パッケージ成形工程において、注入された樹脂の流れ出し防止が可能な電子デバイスの製造方法を提供する。

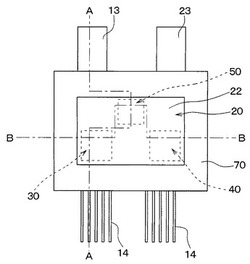

【解決手段】分割リードフレーム10に分割リードフレーム20を重ねて、1つのリードフレーム50を構成する。そのとき、分割リードフレーム10に設けられた第1のダムバー13に形成された突起部13aは、その端部が隣り合う分割リードフレーム20に設けられた第2のダムバー23と重なり合う。突起部13aは、重なり合った部分が上金型51と下金型52との間で挟み込まれ、この挟み込みの力で第2のダムバー23にめり込むようにリードフレームの厚さまで変形し、変形しなかった部分が第1のダムバー13と第2のダムバー23との間に配置される。

(もっと読む)

電子デバイスの製造方法及び電子デバイス

【課題】1つの樹脂パッケージ内に複数個の電子部品を配置する場合でも、樹脂パッケージの大型化を抑制できるようにした電子デバイスの製造方法及び電子デバイスを提供する。

【解決手段】第1の領域に第1の部分が位置する第1のリード、を有する第1のリードフレームを用意する工程と、前記第1のリードと第1の電子部品とを電気的に接続する工程と、前記第1の部分が前記第1の領域の外側に位置するように、前記第1のリードを屈曲させる工程と、第2のリードフレームが有する第2のリードの第2の部分が前記第1の領域に位置するように、前記第1のリードフレームに前記第2のリードフレームを重ねる工程と、前記第2のリードと第2の電子部品とを電気的に接続する工程と、を含む。

(もっと読む)

半導体装置及び半導体装置製造方法

【課題】回路素子やインダクタを複合一体化し、インダクタで発生する熱に対して放熱機能を有する半導体装置を提供する。

【解決手段】第1リード10と、第1リード10と分離配置された第2リード12と、第1リード10の表面に搭載されるインダクタLと、第2リード12に搭載され、第1リード10及び第2リード12のアウターリードにてインダクタLと電気的に接続される回路素子と、第1リード10の裏面と第2リードの素子搭載部裏面の一部を露出し、インダクタL及び回路素子を封止する第1封止体20とを備える。

(もっと読む)

半導体装置

【課題】封止品質を低下させることなく所望した平面トランスのゲインと電圧変動率を確保することができる半導体装置を提供すること。

【解決手段】本発明による半導体装置1は、一方のリードフレーム2と、他方のリードフレーム3と、一方のリードフレーム2の含む平面コイル4と他方のリードフレーム3の含む平面コイル5とにより挟持される絶縁薄膜6とを含むとともに、絶縁薄膜6が、平面コイル4、5の巻回中心の径方向外側から径方向内側に向けて封入樹脂を誘導する誘導手段を含むことを特徴とする。

(もっと読む)

半導体装置

【課題】リードフレームの上下両面に半導体チップを搭載するにあたって、上下面の半導体チップとリードフレームとの間および半導体チップ間を良好に接続する。

【解決手段】半導体装置はインナーリード部2と第1および第2のアウターリード部3、4とを備える回路基材(リードフレーム)1を具備する。インナーリード部2は複数のインナーリード5、6、7を有し、それらの少なくとも一部はチップ搭載領域X内を引き回されている。回路基材1の上下両面には第1および第2の半導体チップ8、9が搭載される。第1の半導体チップ8の電極パッド10の少なくとも一部はインナーリード7を介して第2の半導体チップ9の電極パッドと電気的に接続される。

(もっと読む)

半導体装置

【課題】半導体チップをダイパッド上に積層しリードにワイヤボンディングした半導体チップを積層する半導体装置において、下層側半導体チップを接着する接着剤の当該半導体チップの上面へのはみ出しを防止し、ワイヤボンディングの接続信頼性を向上させる。

【解決手段】ダイパッド21に積層した上層側の第2の半導体チップ12の少なくとも一側の端部が下層側の第1の半導体チップ11よりも外方へ突出しており、第2の半導体チップ12の突出端部を支持するアップセット部24がダイパッド21に設けられており、アップセット部24以外のダイパッド21は平坦である半導体装置とする。

(もっと読む)

リードフレーム型基板とその製造方法および半導体装置

【課題】リードフレームを用いて電子部品を内蔵した半導体装置を製作する場合、半導体素子の端子数の増大にも良く対応でき、且つ、部品配置の自由度が高い、部品内蔵のリードフレーム型基板とその製造方法およびそれを用いた半導体装置を提供する。

【解決手段】金属板の第1面に配線、第2面に接続用ポスト、それら以外の領域に電子部品が埋設されたプリモールド用樹脂層が有り、好ましくは電子部品実装状態では電子部品の高さが接続用ポストを越えないリードフレーム型基板、及び、その基板に半導体素子が実装され、基板と半導体素子がワイヤーボンディングされた半導体装置である。

(もっと読む)

積層リードフレーム及びその製造方法並びに半導体装置及びその製造方法

【課題】めっき層が形成されていない積層リードフレームにおける拡散接合条件に耐え得る積層リードフレームを提供する。

【解決手段】リードフレーム材と積層用リードフレーム材(導体板16と表外側端子17)にそれぞれ所定の形状加工をし、形状加工したリードフレーム材の上に積層用リードフレーム材を接合してなる積層リードフレームにおいて、銅又は銅合金からなるリードフレーム材の表面を、厚さ0.1μm以上の酸化銅層Cで被覆した。リードフレーム材に形成した酸化銅層によって、脆弱な酸化銅皮膜の形成を防ぎ、リードフレーム材と形成した酸化銅層の強固な密着性により、半導体装置の信頼性が向上する。

(もっと読む)

半導体装置及びその製造方法

【課題】パッケージの厚さを大きくすることなく、複数の半導体チップを同一パッケージ内に搭載することが可能な構造を有する半導体装置を提供する。

【解決手段】半導体装置は、ダイパット1と、半導体チップ4と、ダイパット2と、半導体チップ5とが、封止樹脂14によって封止されている。半導体チップ4の下面は、ダイパッド1に接続されており、半導体チップ5の下面における第1の部分が、ダイパッド2に接続されており、且つ、半導体チップ5の下面におけるダイパッド2に接続されていない第2の部分が、封止樹脂の材料とは異なる材料よりなる断熱材12を介して、半導体チップ4の上面と接続されている。

(もっと読む)

1 - 20 / 75

[ Back to top ]