Fターム[5F067BC03]の内容

IC用リードフレーム (9,412) | 外部リード (607) | 外部リードのプリント基板への取付け (178) | 位置決め (59) | リード長さが異なるもの(順次異なるもの) (7)

Fターム[5F067BC03]に分類される特許

1 - 7 / 7

電子部品の実装構造

【課題】実装時における位置ズレが生じる従来の電子部品の実装構造に対して、半田ブリッジの発生を防止しつつ、実装の際に角度ずれが小さいことが要求される電子部品の取り付け角度の精度を高められる電子部品の実装構造を目的とする。

【解決手段】電子部品の実装構造において、電子部品が略直方体形状の基体の側面から複数のリード端子を延出しており、複数のリード端子が基体の四隅の内少なくとも2個所に設けられたアライメント用リード端子とアライメント用リード端子を除く電気的に基体内の電子回路に接続される電極リード端子とからなり、アライメント用リード端子が電極リード端子より長く延出されており、複数の接続ランドがアライメント用リード端子と半田付けされるアライメント用接続ランドと電極リード端子と半田付けされる電極用接続ランドとからなり、アライメント用接続ランドの長さが電極用接続ランドの長さよりも長いことを特徴としている。

(もっと読む)

半導体装置及び実装構造

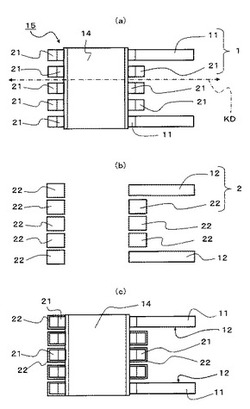

【課題】 複数の表面実装型リードを有する半導体装置及びその実装構造において、高速信号用リード及びパッドの容量成分を低減し、高速信号の伝送品質を向上させる。

【解決手段】 半導体装置10は複数の表面実装型リード20を含み、各リード20は、半導体装置10が配線基板30に実装されるときに配線基板30に接合される接合面を有する。リード20は、所定の高速信号用の第1のリード22と、その他のリードである第2のリード21とを含み、第1のリード21の接合面の面積は、第2のリード21の接合面の面積より小さい。配線基板30は、半導体装置10の複数のリード20の接合面に位置的に対応して、複数の実装パッド40を有する。配線基板30の複数のパッド40は、第1のリード22に接合される第1のパッド42と、第2のリード21に接合される第2のパッド41とを含み、第1のパッド42の面積は第2のパッド41の面積より小さい。

(もっと読む)

ICパッケージ

【課題】ICパッケージの接続ピンの相互間で識別を容易にする。

【解決手段】ICパッケージの接続ピンが、相互に形状が異なる第1及び第2の接続ピンを含み、第1の接続ピンの数と第2の接続ピンの数のリードピンの比率が約1:n(nは2以上の整数)である。

(もっと読む)

回路体

【課題】接続端子毎に溶接の条件を相違させる必要が生じない回路体を提供すること。

【解決手段】本発明による回路体1は、接続端子2a〜2f、3a〜3fを有する導電体2、3を、接続端子2a〜2d、3a〜3dの端部を露出して絶縁体5により被覆し、少なくとも一の組み合わせの接続端子の長さを相違させてなる回路体であって、当該組み合わせの接続端子のうち長い方の接続端子2a〜2dの絶縁体5により被覆する部分の長さを、短い方の接続端子3a〜3dの絶縁体5により被覆する部分の長さよりも長くすることを特徴とする。

(もっと読む)

電子部品取付構造

【課題】極性を有する電子部品を基板に挿通させる際の誤挿入を抑制するとともに、振動による位置ずれで生じる部品浮きや部品落下等を抑制することができる電子部品取付構造を得る。

【解決手段】電子部品1の本体部2から延びる複数本のリード線4,5を、それぞれ基板10に形成された挿通孔15,16に挿通させて、前記基板10に前記電子部品1を実装する電子部品取付構造において、前記複数本のリード線4,5のうちの一部のリード線を、先端側を根元側に向けて折り返した折返部8を有する屈曲リード線4とし、前記屈曲リード線4が前記挿通孔15に挿通された状態で、前記折返部8によって当該挿通孔15の内面15aを押圧するようにした。

(もっと読む)

撮像装置、撮像装置の組み立て方法

【課題】パッケージの4辺それぞれに複数のリードが並べて1組ずつ設けられた撮像素子を用いても、リードの挿入実装が容易に行える撮像装置、撮像装置の組み立て方法を提供する。

【解決手段】対向して配置された2組のリードの集合である第1のリード群(リード組12,13)について、第1のリード群と直交する方向において対向して配置された2組のリードの集合である第2のリード群(リード組14,15)よりもリードの長さを長くする。

(もっと読む)

半導体装置及びその製造方法、並びにリードフレーム

【課題】 コストを低減することができ、端子の多列化、多ピン化及び実装面積を低減することができる半導体装置及びその製造方法、並びにリードフレームを提供すること。

【解決手段】 半導体チップ2が内側リードフレーム3にマウントされ、内側リードフレーム3の周囲に外側リードフレーム4が設けられ、半導体チップ2が内側リードフレーム3及び外側リードフレーム4にそれぞれ接続されている、半導体装置及びその製造方法。半導体チップ2をマウントする内側リードフレーム3と、この内側リードフレーム3の周囲に設けられた外側リードフレーム4とからなり、内側リードフレーム3が絶縁材8によって支持されながら、支持材9によって支持された外側リードフレーム4の内側に配されている、リードフレーム。

(もっと読む)

1 - 7 / 7

[ Back to top ]