Fターム[5F067DF20]の内容

IC用リードフレーム (9,412) | ボンディング及びボンディングワイヤと内部リードの接触防止 (523) | ボンディングワイヤを用いないもの (37)

Fターム[5F067DF20]に分類される特許

1 - 20 / 37

半導体装置およびその製造方法

【課題】第1リードフレームと第2リードフレームとの間に搭載部品が3個のみ挟み込まれてなる半導体装置において、第1〜第3搭載部品と第2リードフレームとが未接合となることを抑制することができる半導体装置およびその製造方法を提供する。

【解決手段】搭載部品30〜50におけるはんだ31〜51、35〜55が配置される部位の中心を搭載部品30〜50の中心点30a〜50aとしたとき、3個の搭載部品30〜50のそれぞれの中心点30a〜50aを結ぶ線分にて三角形100が構成される状態で3個の搭載部品30〜50を挟み込む。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の信頼性低下を抑制する。

【解決手段】半導体装置1は、半導体チップ3が搭載された上面2a、封止体6から露出する下面、上面2aと下面との間に位置する複数の側面2c、を備えたタブ(チップ搭載部)2を有している。また、タブ2の複数の側面2cは、タブ2の下面に連なる部分2c1と、部分2c1よりも外側に位置し、タブ2の上面2aに連なる部分2c2と、部分2c2よりも外側に位置し、タブ2の上面2aに連なり、部分2c1、2c2と同一方向を向いた部分2c3とを有している。そして、平面視において、半導体チップ3の外縁は、タブ2の部分2c3と部分2c2との間に位置し、かつ、半導体チップ3とタブ2を接着固定する接着材の外縁は、半導体チップ3と部分2c2との間に位置する。

(もっと読む)

半導体装置およびその製造方法

【課題】バンプ電極の接合不良を改善することにより、半導体装置の製造歩留まりを向上させる。

【解決手段】半導体チップ3の表面に形成された複数のボンディングパッド4と複数のリード2とを複数のバンプ電極5を介してそれぞれ接続する半導体装置において、複数のリード2の上面を、平坦な面(最大高さ(Ry)=0)ではなく、最大高さ(Ry)が0μmよりも大きく、20μm以下の範囲(0μm<最大高さ(Ry)≦20μm)の粗さを有する半光沢状の面とする。

(もっと読む)

半導体装置

【課題】半導体チップからダイパッドへ効率良く放熱する半導体装置を実現できるようにする。

【解決手段】半導体装置は、ダイパッド121を含むリードフレーム102と、ダイパッド121のチップ搭載領域にダイボンド材132により接合された半導体チップ101とを備えている。チップ搭載領域は、半導体チップ101に間隔をおいて外嵌する第1の部分124aと、第1の部分124aよりもその壁面と半導体チップ101の側面との間隔が大きい第2の部分124bとを含む凹部124である。半導体チップ101の側面と凹部124の壁面との間にはダイボンド材132が充填されている。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体素子の固着に用いられる導電性固着材が半導体素子の外周に染み出すと、導電性固着材と封止樹脂の密着性が悪いため、封止樹脂とアイランドの密着性が劣化する問題がある。一方で、半導体素子の外周への導電性固着材の染み出しが全くないと、導電性固着材の濡れの状態が目視できない。

【解決手段】アイランドとアイランド主面に導電性固着材で固着される半導体素子と、半導体素子と電気的に接続されて一部が外部に導出するリードと、これらを一体的に被覆する封止樹脂とを備えている。アイランドの主面に、半導体素子の側辺に沿って帯状に溝を設ける。溝は半導体素子のコーナー部下方において不連続とする。導電性固着材はリフローで液状となった場合に溝で規制され、半導体素子の側辺からの染み出しを低減できる。溝が不連続な領域では若干量の導電性固着材を染み出させ、導電性固着材の濡れを視認可能とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 金属リボンの超音波ボンディングを行う際、アイランドの浮きを防止するため、ボンディング装置のクランパによってアイランドの周辺領域や、アイランド周囲に設けた吊りピンを押さえる必要がある。しかし、装置の小型化によって十分なアイランドの周辺領域が確保できない場合や吊りピンが設けられない場合には、アイランド側を押さえることができない問題がある。

【解決手段】 アイランドのリードと対向する辺に、リード端部と同じ高さでリード側に突出する複数の突起部を設ける。突起部とリード端部を同時にクランパで押圧することにより、吊りピンや、アイランド周囲の押さえ領域がない場合であっても、アイランドの浮きを防止できる。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の圧接型の半導体装置と比較して簡素な構造で半導体素子を位置決めすることができ、半導体素子の絶縁性及び耐圧性を確保しつつ、耐熱性に優れると共に製造コストが低減された半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置Sは、半導体素子9と、これを挟持するエミッタ端子1a、ゲート端子1b、及びコレクタ端子2aとの外周を覆うように硬化性樹脂3が付与されると共に、エミッタ端子1a、ゲート端子1b、及びコレクタ端子2a(電極端子)には、これらの電極端子を位置決めする係止部(窪み部1e,2e)が設けられることを特徴とする。

(もっと読む)

回路モジュール

【課題】外部の温度が変化しても樹脂封止体と回路パターン部とが剥がれることを防止できる回路モジュールを提供する。

【解決手段】回路モジュールとしての制御回路パッケージ6は互いの間隔をあけて設けられた導電性の二つの回路パターン部22a,22bと二つの回路パターン部22a,22b同士を接続した抵抗30と二つの回路パターン部22a,22bと抵抗30を埋設した樹脂封止体19を備えている。パターン部22a,22bは圧接端子に接続する直線状に延在した接続部40と抵抗30が取り付けられる部品取付部42と接続部40の幅方向の一方の縁に連なりかつ接続部40と部品取付部42との双方に連なっている幅狭連結部43を備えている。幅狭連結部43は部品取付部42と接続部40との双方よりも幅が狭い。

(もっと読む)

樹脂封止型半導体装置

【課題】半導体チップとリードとを板状の接続子によって電気接続する構成の樹脂封止型半導体装置において、リード及び接続子の相対的な位置決めを容易に行うことができ、かつ、電気的な信頼性の向上を図ることができるようにする。

【解決手段】リード4には、その上面41aから窪む窪み部43が形成され、接続子5には、窪み部43に挿入されて係合する接続突起部54が形成され、窪み部43の内面が、当該窪み部43の開口縁44からリード4の上面41aに対して傾斜する傾斜面45A,45Bを有し、接続突起部54を窪み部43に挿入した状態で互いに対向する窪み部43の内面及び接続突起部54の表面が、相互に対応する相似形状に形成されている樹脂封止型半導体装置を提供する。

(もっと読む)

リードフレーム及びリードタイプの電子部品

【課題】 電子デバイスをパッド部に搭載する際に高精度な位置決めを行うことができるリードフレーム及びリードタイプの電子部品を提供する。

【解決手段】電子デバイス4を搭載するための搭載面(X−Y平面)をそれぞれ備えた第1パッド部7、第2パッド部8及び第3パッド部9と、第1パッド部7から延設された第1リード端子1、第2パッド部8から延設された第2リード端子2、第3パッド部9から延設された第3リード端子3と、電子デバイス4を搭載する位置を決定するための位置決め部(例えば、切り欠き部71及び切り欠き部91)とを備えたものである。

(もっと読む)

リードタイプの電子部品及びリードフレーム

【課題】リードタイプの電子部品を配線基板に実装する際の熱によって電子部品の電気的な特性が劣化してしまうことを防止できるリードタイプの電子部品及びリードフレームを提供する。

【解決手段】隣接して配されたパッド部7、パッド部8及びパッド部9と、パッド部7、パッド部8及びパッド部9からそれぞれ同一方向に延設されたリード端子1、リード端子2及びリード端子3とを備えており、リード端子1、リード端子2及びリード端子3は、隣り合うリード端子間のピッチが狭い狭ピッチ部位(図中、領域D1で示す部位)と、隣り合うリード端子間のピッチが広い広ピッチ部位(図中、領域D3で示す部位)とをそれぞれ備え、前記狭ピッチ部位は、前記広ピッチ部位よりもパッド部7、パッド部8及びパッド部9側に配され、リード端子1、リード端子2及びリード端子3のうちの少なくとも1つのリード端子は、前記広ピッチ部位に第1突出片12,12を備えた。

(もっと読む)

樹脂封止型半導体装置およびその製造方法

【課題】低コストで信頼性上も有利な樹脂封止型半導体装置を提供する。

【解決手段】ダイパッド12を有する第1リードフレーム10と、インナーリード23a,23bを有する第2リードフレーム20を準備する。ダイパッド12の上に、半導体チップ30を搭載し、第2リードフレーム20を第1リードフレーム10の上に重ねる。インナーリード23a,23bの各先端部25a,25bと半導体チップ30の一部(電極)とを、超音波溶接などにより、接合する。その後、第1,第2リードフレーム10,20の積層体を金型にセットして、樹脂封止を行う。半導体チップ30とインナーリード23a、23bとが1つの接合部で直接接続されているので、接合の信頼性が高い。半導体チップ30とインナーリード23a、23bとの位置合わせが簡単で、製造コストも安い。

(もっと読む)

樹脂ケース及び樹脂ケース製造方法

【課題】半導体素子を収容する樹脂ケースの品質を向上させる。

【解決手段】樹脂ケース41内に表面が突出するように固定されたナット60と、少なくとも一部が折り曲げられ、樹脂ケース40内に一部が固定された外部接続用端子50と、を有した半導体装置1が提供される。半導体装置1では、樹脂ケース40と樹脂ケース41とが一体化している。また、当該半導体装置1では、予め折り曲げられた外部接続用端子50の一部が樹脂ケース40内に固定されているので、ナット60の表面と外部接続用端子50の一部とが密接している。

(もっと読む)

電子部品の製造方法

【課題】使用環境及び使用時間にかかわらず、電子部品の端子表面のめっき層からウィスカの発生を回避することができる電子部品の製造方法を提供する。

【解決手段】 βSn相を含むめっき層21が表面に被覆された端子20の一部を、接合材料30を介して基板10に接合する工程と、前記めっき層21を冷却して、該めっき層21に含まれるβSn相の少なくとも一部をαSn相に相転移させる工程と、前記相転移されためっき層22のうち、前記接合材料と未接触部分のめっき層を除去する工程とを含む。

(もっと読む)

回路部材および回路部材の製造方法

【課題】半導体装置のパッケージサイズにおけるチップの占有率を上げ、半導体装置の小型化に対応させ、同時に、半導体素子の高速化に対応できる半導体装置に用いられる回路部材とその製造方法を提供する。

【解決手段】半導体素子の端子と電気的に接続するための内部端子部131と、外部回路への接続のための外部端子部132と、前記内部端子部と外部端子部とを一体的に連結するリード部133とを有し、内部端子部と外部端子部とがその表裏に分け設けられ、内部端子部、リード部が薄肉に形成され、外部端子部は厚肉に形成された、端子部材を、複数個、それぞれ互いに独立して、且つ、各端子部材の内部端子部の端子面131Sを、同じ向きに一平面上そろえて配置し、更に、これらの外側で、前記リード部とは異なる接続リード134を介して外部端子部と一体連結して、全体を保持する外枠部135を備えている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】 組立に際して半導体素子の接続位置のバラツキによってのリークやショートなどの電気特性が損なわれるという問題をなくし、材料効率の向上を図り、低コストで信頼性の高い半導体装置を提供する。

【解決手段】第1リード端子の第1主面に接続された半導体素子の電極部にロール状のスプールから繰り出された帯状、未切断の金属の端部を直接超音波接合させその後中間部をアーチ形状に形成しの第2リード端子の第1主面とアーチ形状最終部とを直接超音波接合された後で前記金属片を切断し金属片を形成する製造方法で半導体素子の接続位置バラツキでの金属片の接続不良による不具合品の防止ができ、また半導体素子のサイズ等の変更に自在に対応できる。

(もっと読む)

半導体装置

【課題】製造歩留り、および、信頼性の低下を抑制しながら、更なる多ピン化、狭ピッチ化に対応することが可能な半導体装置を提供する。

【解決手段】この半導体装置は、上面上に複数の電極パッド2が設けられた半導体チップ1と、インナーリード部21bを含み、インナーリード部21bが半導体チップ1側となるように配された複数のリード端子21と、互いに絶縁分離された複数の配線層32を一主面上に有するシート状の配線部材30と、少なくとも、半導体チップ1、インナーリード部21bおよび配線部材30を封止する封止樹脂層40とを備えている。そして、半導体チップ1の電極パッド2とリード端子21のインナーリード部21bとは、配線部材30の配線層32を介して互いに電気的に接続されている。

(もっと読む)

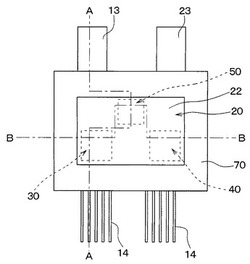

リードフレーム、半導体装置、及び半導体装置の製造方法

【課題】薄型の半導体装置を製造可能なリードフレームを提供すること。

【解決手段】本発明の一態様に係るリードフレームは、樹脂封止型の半導体装置に用いられるリードフレーム30であって、枠体部とリード部を有する第1リードフレーム10及び第2リードフレーム20を具備する。そして、第1リードフレーム10の枠体部12と、第2リードフレーム20の枠体部22を重ね合わせた際に、第1リードフレーム10のリード部11と、第2リードフレーム20のリード部21とが接触せず、かつ、第1リードフレーム10のリード部11を構成するインナーリード部13と、第2リードフレーム20のリード部21を構成するインナーリード部23とを同一面内に配置する。

(もっと読む)

積層型ダイパッケージ用の金属リードを含む、金属リードを有するマイクロ電子ダイパッケージ、ならび関連するシステムおよび方法

本明細書には、マイクロ電子ダイパッケージ、ダイパッケージの積層型システム、ならびにそれらの製造方法が開示される。ある実施形態では、積層されたパッケージのシステムは、底面と、第1の誘電性ケーシングと、第1の金属リードとを有する第1のダイパッケージと;第1のパッケージの底面に付着される上面と、側面を備える誘電性ケーシングと、第1の金属リードと整列されかつそれに向かって突き出し、ならびに外面と、側面の方を概ね向く内面部分とを含む、第2の金属リードとを有する第2のダイパッケージと;個々の第1のリードを個々の第2のリードに結合する金属はんだコネクタとを含む。さらなる実施形態では、個々の第2のリードは、「L」字型であり、かつ対応する個々の第1のリードに物理的に接触する。別の実施形態では、個々の第2のリードは、「C」字型であり、かつ第2のケーシングの側面に向かって突き出る、段になった部分を含む。  (もっと読む)

(もっと読む)

突起状バンプまたはボールを有する、封止されたリードフレームを特徴とする半導体デバイスパッケージ

【課題】突起状バンプまたはボールを有する、封止されたリードフレームを特徴とする半導体デバイスパッケージを提供する。

【解決手段】導電性バンプまたはボール206を介して、支持されたダイ202と電気的に導通するリードフレームを特徴とする半導体デバイスパッケージ200に関する。独立したダイパッド、およびダイパッドの縁部と、隣接する非一体化リードまたはピンとの間の水平方向の分離の必要性をなくすことにより、バンプ・オン・リードフレームプロセスにより製造されたパッケージの態様は、パッケージ専有面積におけるダイの利用可能なスペースを増大させ、多数のダイおよび/または多数の受動素子が、ダイパッドによって従来使われていたパッケージ内のスペースを占有することも可能にし得る。その結果、JEDECが指定する従来の小さな専有面積における完全なサブシステムに必要なダイと技術の組合せを可能にする。

(もっと読む)

1 - 20 / 37

[ Back to top ]