Fターム[5F083AD22]の内容

Fターム[5F083AD22]の下位に属するFターム

複数枚の横フィン型 (3)

Fターム[5F083AD22]に分類される特許

1 - 20 / 27

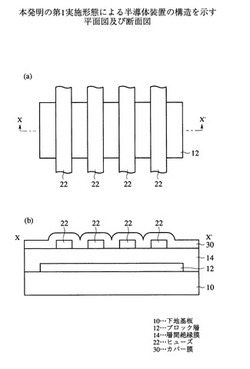

半導体装置の製造方法

【課題】高集積化が容易で製造コストが増加しないヒューズ回路を有する半導体装置の構造及びその製造方法、並びに、このようなヒューズの切断に適したレーザ装置を提供する。

【解決手段】下地基板10上に形成されたブロック層12と、ブロック層12上に形成された絶縁膜14と、絶縁膜14上に形成されたヒューズ22とにより半導体装置を構成する。ヒューズ22の下層部にブロック層12を設けることにより、レーザアブレーションによりヒューズを切断し、且つ、ブロック層12によってレーザアブレーションを制御性よく停止することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の高い半導体装置を提供する。

【解決手段】半導体基板101と、前記半導体基板の上方に設けられた、誘電体膜116を下部電極115と上部電極117とで挟んでなるキャパシタと、を備え、前記下部電極は、貴金属膜115aと、前記貴金属膜上に島状に複数形成された導電性酸化物膜115bと、を有する。

(もっと読む)

DRAMセル

【課題】リーク電流および消費電力を低減させることができるDRAMセルを提供する。

【解決手段】DRAMセルは、半導体材料からなり、主表面102を有する基板100と、主表面102に形成されたトランジスタ120と、トランジスタ120の上方に配置された金属層に形成されたキャパシタ140と、を備える。

(もっと読む)

容量素子の製造方法

【課題】下部電極を構成するシリコン膜の表面にシリコン結晶粒を成長させる工程を含む容量素子の製造方法において、熱処理の工程数を低減する。

【解決手段】容量素子の製造方法は、シリコンに不純物がドーピングされた不純物含有シリコン層92からなる下部電極94の表面にシリコン結晶粒93を成長させて、下部電極94の表面を粗面化する工程と、粗面化された下部電極94の表面に800℃以上の温度下でバリア層95を形成することにより、不純物含有シリコン層92を活性化する工程と、バリア層95の表面にタンタル酸化膜96を堆積して、バリア層95とタンタル酸化膜96とからなる容量絶縁膜97を形成する工程と、容量絶縁膜97の上に上部電極98を形成する工程とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】溝型トランジスタと高耐圧トランジスタのエクステンション領域の形成となるイオン注入工程を同一のフォトリソグラフィ工程中において行える製造方法の提供を目的とする。

【解決手段】溝型セルトランジスタ領域に溝を形成し、半導体基板上にゲート絶縁膜とゲート材料層を形成し、溝型セルトランジスタ領域と、高耐圧トランジスタ領域のエクステンション領域形成部とを露出させたフォトレジスト層を半導体基板上に形成し、溝型セルトランジスタ領域の半導体基板表面と高耐圧トランジスタ領域へイオン注入を行って各領域のエクステンション領域を形成した後、さらにゲートをパターニング後、溝型セルトランジスタ領域と高耐圧トランジスタ領域とをフォトレジスト層で覆って通常耐圧トランジスタ領域へイオン注入を行って該領域のエクステンション領域を形成する。

(もっと読む)

半導体装置

【課題】本発明は、COP構造を採用することなしにセル面積の縮小と強誘電体キャパシタ面積の増加を実現することを最も主要な特徴とする。

【解決手段】基板51と、拡散領域54Aと、その上に形成された層間絶縁膜55と、層間絶縁膜55に形成され、拡散領域54Aに通じるホール57A及び57Bと、ホール57A及び57B内に形成され、拡散領域54Aと電気的に接続された下部電極59と、下部電極59上に形成された強誘電体膜60と、強誘電体膜60上に形成された上部電極61とを有し、下部電極59、強誘電体膜60及び上部電極60でそれぞれ強誘電体キャパシタが構成されている。

(もっと読む)

半導体容量素子の構造とその製造方法

【課題】本発明の課題は、十分な強誘電体特性を有する半導体容量素子及びその製造方法を提供することにある。

【解決手段】上記のような課題は、強誘電体と下部電極界面を単一とすることにより達成される。すなわち、本発明に係る半導体容量素子は、所定の電極材料を複数積層して形成される下部電極と;前記下部電極の一部の側壁に形成されるサイドウォールと;前記下部電極上に形成される誘電体層と;前記誘電体層上に形成される上部電極とを備えている。

(もっと読む)

半導体記憶装置および半導体記憶装置の製造方法

【課題】強誘電体キャパシタを配線層に接続するための開口部を形成した場合においても、強誘電体キャパシタを水素から保護できるようにする。

【解決手段】コンタクトプラグ8aを介してソース層6aに接続された強誘電体キャパシタを層間絶縁層7上に形成し、SiH4−N2を主原料とした高密度プラズマCVDにてシリコン窒化膜からなる層間絶縁層15を強誘電体キャパシタ上に形成してから、上部電極13bおよびコンタクトプラグ8bにそれぞれ接続されたコンタクトプラグ16a、16bを層間絶縁層15に埋め込む。

(もっと読む)

半導体記憶装置および半導体記憶装置の製造方法

【課題】コンタクトプラグに接続される下部電極が形成される下地層の表面状態および結晶構造の均一性を向上させる。

【解決手段】バリア膜14、導電膜15、強誘電体膜16および導電膜17を導電膜13上に形成し、レジストパターン18をマスクとして導電膜17、強誘電体膜16、導電膜15、バリア膜14および導電膜13を順次エッチングし、層間絶縁層9を露出させることにより、開口部12の周囲の層間絶縁層9上にはみ出すようにして開口部12に埋め込まれたコンタクトプラグ13aを形成するとともに、コンタクトプラグ13a上に配置されたバリア膜14a/下部電極15a/容量絶縁膜16a/上部電極17aの積層構造を形成する。

(もっと読む)

半導体装置とその製造方法

【課題】高誘電率で薄膜化、均一化が可能であり、高性能なキャパシタ絶縁膜を有する半導体装置とその製造方法を提供する。

【解決手段】半導体基板上に形成されたトランジスタ13,14は、ゲート絶縁膜を介して形成されたゲート電極と、このゲート電極の両側に位置する半導体基板内に形成された第1、第2の拡散層とを有している。第1の電極15、16は、トランジスタの第1の拡散層に接続されている。第1の電極上に形成されたキャパシタ絶縁膜17は、拡散速度がCuより速く、Cuより酸素と反応しやすい物質を含有するシリコン酸化膜により形成されている。キャパシタ絶縁膜上に形成された第2の電極は、Cu層と、前記物質を含むCu層のうちの1つにより形成されている。

(もっと読む)

半導体メモリ素子の製造方法

【課題】半導体メモリ素子の製造方法を提供する。

【解決手段】基板200全面に形成された層間絶縁膜230上に位置するソース領域205上部に位置し、ゲートG12の伸張方向に伸び、層間絶縁膜の一部分だけをライン形状に露出させる自己整列フォトレジストマスクを利用し、ビットライン及びキャパシティ下部電極を半導体基板の活性領域に連結させるビットラインコンタクト連結体216a及び下部電極連結体228aを形成することにより、誤整列マージンを確保することができる技術と、ビットラインコンタクト連結体及び下部電極連結体それぞれを1回のマスク工程を利用して形成する半導体メモリ素子の製造方法。

(もっと読む)

誘電体メモリ及びその製造方法

【課題】 COB構造を有する誘電体メモリにおいて、スタックコンタクトにおける下部コンタクトプラグのコンタクト抵抗の安定化を図る。

【解決手段】 不純物拡散層104に接続する第1のコンタクトプラグ108の上方に形成された配線109を覆う第2の絶縁膜110を形成する工程と、第2の絶縁膜110上に第3の絶縁膜111を形成する工程と、第3の絶縁膜111上に第1の水素バリア膜112を形成する工程と、第1の水素バリア膜112上にキャパシタ118を形成する工程と、第1の水素バリア膜112における第1のコンタクトプラグ108の上方に存在している部分を選択的に除去した後、キャパシタ108に対して熱処理を行う工程とを備える。これにより、熱処理時に、第1のコンタクトプラグ108の上面が第2の絶縁膜110及び第3の絶縁膜111によって覆われているので、第1のコンタクトプラグ108の酸化及び消失を防止することができる。

(もっと読む)

半導体装置

【課題】 コンタクトプラグ形成時のCMPによって発生する絶縁膜へのスクラッチを起因としたキャパシタ下部電極間のブリッジを防止する。

【解決手段】 基板上に形成された下部電極105、容量絶縁膜及び上部電極107からなるキャパシタ108と、基板と下部電極105とを電気的に接続するコンタクトプラグ104とを備えた半導体装置であって、下部電極105は列状に複数配置し、隣り合う下部電極105の中心位置は、列方向と直交する方向に距離t1ずれて配置され、下部電極105の中心位置と、下部電極105におけるコンタクトプラグ104の中心位置は、隣り合う下部電極105と離れるように列方向と直交する方向(y方向)に距離t2ずれて配置されている。また、距離t1と距離t2との和は、列方向と直交する方向における下部電極105の寸法の1/2より大きくした。

(もっと読む)

半導体装置の製造方法

【課題】容量素子の下方にシリコン窒化膜からなる水素バリア膜を備えた半導体装置において、コンタクトプラグ形成工程で生じる密着層の剥離を防止する。

【解決手段】第1のシリコン酸化膜104、シリコン窒化膜105、及び第2のシリコン酸化膜106からなる積層膜に形成されたコンタクトホール107の内壁に、CVD法により、チタン膜及び窒化チタン膜からなる密着層108を形成する。次にCVD法により、コンタクトホール107内をタングステン又はポリシリコンからなる導電膜109aで充填し、CMP法により、第2のシリコン酸化膜106上の導電膜109a及び密着層108を除去する。続いてエッチバック法又はCMP法により、第2のシリコン酸化膜106を除去し、シリコン窒化膜105を露出させることにより、密着層108と水素バリア膜であるシリコン窒化膜との剥離を防止し、且つシリコン窒化膜へのスクラッチの発生を防ぐことができる。

(もっと読む)

電界効果トランジスタとその製造方法、及び半導体装置

【課題】ソフトエラーレートを向上させる電界効果トランジスタを提供すること

【解決手段】本発明による電界効果トランジスタ1は、第1の空洞51を有する基板10と、ゲート電極40と、拡散層60とを備える。ゲート電極40及び拡散層60は、基板10の表面に平行な面XYにおいて、第1の空洞51を囲むように形成される。チャネル領域70は、第1の空洞51の側面に位置し、基板10の表面に対して略垂直に形成される。

(もっと読む)

半導体装置

【課題】電極構造下方のプラグの酸化を抑制する半導体装置を提供する。

【解決手段】半導体基板(S)と、この半導体基板に形成されたトランジスタの活性領域(107)に接続した導電性プラグ(118)と、この導電性プラグの底面部及び側面部に被覆する金属シリサイド膜(117)と、前記導電性プラグ上に形成された電極構造(200)と、を備えている。

(もっと読む)

キャパシタ

【課題】スタック型キャパシタの下側電極の誘電体層形成時の酸化を防止する形成方法を提供する。

【解決手段】少なくとも一つの側壁を有する内側キャパシタ板60と、前記少なくとも一つの側壁に対してそれを被覆するように設けられる酸化バリア層70と、前記内側キャパシタ板上に設けられるキャパシタ誘電体板90と、前記キャパシタ誘電体板の上に設けられる外側キャパシタ板100とから成るキャパシタが開示される。発明の好適実施形態によれば、絶縁性誘電体層80が酸化バリア層70の上に設けられ、その絶縁性誘電体層は酸化バリア層とは異なる組成物からなっている。

(もっと読む)

半導体装置及びその製造方法

一又は複数のピクセルが形成される画素領域と、各ピクセルからの出力信号を記憶する一又は複数のDRAMセルが形成されるDRAMセル領域とを含み、画素領域及びDRAMセル領域を構成する各層が同一の半導体プロセスによって形成されて成ることを特徴とする。  (もっと読む)

(もっと読む)

薄膜の形成方法および半導体装置の製造方法

【課題】 原子層蒸着法により、基板に設けられたトレンチの内壁を覆う状態で、組成比の変わらない均一な膜厚のキャパシタ絶縁膜を形成可能な薄膜の形成方法および半導体装置の製造方法を提供する。

【解決手段】 基板11に形成されたトレンチ13の内壁に、少なくともキャパシタ絶縁膜14および上部電極を下層から順に積層してなるトレンチキャパシタを備え、原子層蒸着法により、トレンチ13の内壁を覆う状態でキャパシタ絶縁膜14を形成する薄膜の形成方法および半導体装置の製造方法であって、キャパシタ絶縁膜14を形成する工程では、原子層を形成するソースガスのキャリアガスとして水素ガスを用いることを特徴とする薄膜の形成方法および半導体装置の製造方法である。

(もっと読む)

半導体装置及びその製造方法

【課題】 スクラッチ又はクラックなどにより、キャパシタを構成する誘電体膜が水素劣化することを防止する。

【解決手段】 第1の層間絶縁膜(107)と、第1の層間絶縁膜(107)上に形成された絶縁性水素バリア膜(108)と、絶縁性水素バリア膜(108)上に形成された第2の層間絶縁膜(109)と、第1の層間絶縁膜(107)、絶縁性水素バリア膜(108)及び第2の層間絶縁膜(109)よりなる積層膜を貫通するコンタクトプラグ(111,112)と、第2の層間絶縁膜(109)上に形成され、コンタクトプラグ(111,112)と接続するキャパシタ(116)とを備える。そして、コンタクトプラグ(111,112)は、下から順に積層された導電層(111)及び導電性水素バリア膜(112)よりなり、導電層(111)の上面は、絶縁性水素バリア膜(108)の上面よりも下に位置している。

(もっと読む)

1 - 20 / 27

[ Back to top ]