Fターム[5F083BS10]の内容

Fターム[5F083BS10]の下位に属するFターム

Fターム[5F083BS10]に分類される特許

21 - 26 / 26

垂直配向ナノロッドを持つ低リークDRAMメモリセルとその製造方法

半導体メモリストレージセルにおいてリーク電流を減らすための方法と構造が記載される。垂直配向ナノロッド(403)が、アクセストランジスタ(400)のチャネル領域で使用され得る。ナノロッドの直径は、アクセストランジスタのチャネル領域内の電子バンドギャップエネルギーの増加を引き起こすために十分小さくすることができ、これはオフ状態でのチャネルリーク電流を制限するように機能し得る。様々な実施形態では、アクセストランジスタは両面キャパシタ(425)に電気的に結合し得る。本発明の実施形態に従うメモリデバイス、およびそのようなデバイスを含むシステムもまた開示される。  (もっと読む)

(もっと読む)

半導体装置

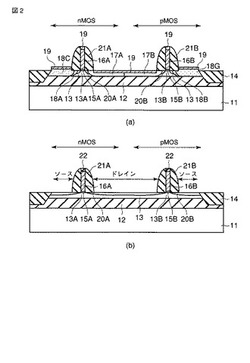

【課題】nチャネルMISトランジスタとpチャネルMISトランジスタとが接続するドレイン領域において、トランジスタ特性を悪化させる不具合が生じないCMOSデバイスを含む半導体装置を提供する。

【解決手段】基板11上の半導体領域に形成されたソース領域18Aと、ドレイン領域17Aとを有するnチャネルMISトランジスタと、半導体領域に形成されたソース領域18Bと、ドレイン領域17Bと有するpチャネルMISトランジスタとを具備する。ドレイン領域17Aと17Bとが接続するように配置されると共に、同一の材料で形成され、ソース領域18A,18Bの少なくともいずれかがドレイン領域17A,17Bと異なる材料で形成されている。

(もっと読む)

MOSFETゲート電極のランディング・パッドのための構造および方法

マイクロエレクトロニクス・トランジスタおよび製作方法の性能および製造可能性を強化するための新たな技術を提供する。

【課題】

【解決手段】トランジスタ装置およびそれを形成する方法であって、基板と、基板上の第1のゲート電極と、基板上の第2のゲート電極と、第2のゲート電極に重なり合うフランジ付き端部の対を備えるランディング・パッドとを備え、第2のゲート電極の構造は、ランディング・パッドの構造と不連続である。

(もっと読む)

半導体装置及びその製造方法

【課題】 カーボンナノチューブ(CNT)トランジスタを用いる半導体装置のレイアウト面積を縮小する。

【解決手段】 半導体装置は、第1の電極103と、第1の層間絶縁膜104を挟み第1の電極に対向する第2の電極106と、第1及び第2の電極間を貫通する第1のCNT部108と、第1の層間絶縁膜104と第1のCNT部108との間に介在する第1のゲート絶縁膜107と、第1の層間絶縁膜104中に形成され且つ第1のゲート絶縁膜107に接する第1のゲート電極105とを備える。更に、第2の層間絶縁膜114を挟み第2の電極と対向する第3の電極116と、各々第1のものと同様に構成された第2のゲート絶縁膜117、第2のCNT部118及び第2のゲート電極115を備える。各々の電極、ゲート絶縁膜、CNT部、ゲート電極により、垂直に配置された第1及び第2の電界効果トランジスタ151及び152が構成されている。

(もっと読む)

CMOSデバイスにおいて自己整合デュアル・フルシリサイド・ゲートを形成するための方法

【課題】 位置ずれの問題を克服する新規のデュアルFUSIゲート形成プロセスを提供する。

【解決手段】 1つのリソグラフィ段階しか必要としない、CMOSデバイスにおいて自己整合デュアル・フルシリサイド・ゲートを形成する方法であり、本方法は、半導体基板(252)の中の第1のウェル領域(253)、第1のウェル領域(253)の中の第1のソース/ドレイン・シリサイド・エリア(266)、及び第1のソース/ドレイン・シリサイド・エリア(266)から分離された第1のタイプのゲート(263)を有する第1のタイプの半導体デバイス(270)を形成するステップと、半導体基板(252)の中の第2のウェル領域(254)、第2のウェル領域(254)の中の第2のソース/ドレイン・シリサイド・エリア(256)、及び第2のソース/ドレイン・シリサイド・エリア(256)から分離された第2のタイプのゲート(258)を有する第2のタイプの半導体デバイス(280)を形成するステップと、第2のタイプの半導体デバイス(280)の上に第1の金属層(218)を選択的に形成するステップと、第2のタイプのゲート(258)のみの上で第1のフルシリサイド(FUSI)ゲート形成を行うステップと、第1及び第2のタイプの半導体デバイス(270、280)の上に第2の金属層(275)を堆積させるステップと、第1のタイプのゲート(263)のみの上で第2のFUSIゲート形成を行うステップとを含む。

(もっと読む)

メモリデバイス、トランジスタ、メモリセル並びにそれらの製造方法

メモリデバイスはメモリセルのアレイと周辺デバイスを含んでいる。少なくとも一部の個別メモリセルはSiCを含む炭酸化部分を含んでいる。少なくとも一部の周辺デバイスは炭酸化部分を含まない。トランジスタは第1ソース/ドレーン、第2ソース/ドレーン、第1ソース/ドレーンと第2ソース/ドレーンとの間にSiCを含む半導体基板の炭酸化部分を含んだチャンネル、及びチャンネルの両側と作動式に関係するゲートを含んでいる。 (もっと読む)

21 - 26 / 26

[ Back to top ]