Fターム[5F083BS11]の内容

Fターム[5F083BS11]に分類される特許

1 - 20 / 34

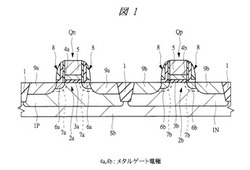

半導体装置およびその製造方法

【課題】ゲート電極の一部にメタルゲート電極を有するMISEFTにおいて、メタルゲート電極を構成するグレインの配向性のばらつきに起因するMISFETのしきい値電圧のばらつきを小さくする。

【解決手段】メタルゲート電極4a、4bに炭素(C)を導入することにより、メタルゲート電極4a、4b内のグレインの粒径が大きくなることを防ぎ、メタルゲート電極4a、4bの中に多数の小さいグレインを形成することにより、グレインの配向性を均一化し、ゲート電極の仕事関数のばらつきを低減する。

(もっと読む)

半導体装置および当該半導体装置の作製方法

【課題】電気的特性の安定した酸化物半導体膜を用いることにより、半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供すること。また、結晶性の高い酸化物半導体膜を用いることにより、移動度の向上した半導体装置を提供すること。

【解決手段】表面粗さの低減された絶縁膜上に接して、結晶性を有する酸化物半導体膜を形成することにより、電気的特性の安定した酸化物半導体膜を形成することができる。これにより、半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供することができる。さらに、移動度の向上した半導体装置を提供することができる。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層の側面からの酸素の脱離を防ぎ、酸化物半導体層中の欠陥(酸素欠損)が十分に少なく、ソースとドレインの間のリーク電流が抑制された半導体装置を提供する。

【解決手段】酸化物半導体膜に対して第1の加熱処理を施した後に該酸化物半導体膜を加工して酸化物半導体層を形成し、その直後に該酸化物半導体層の側壁を絶縁性酸化物で覆い、第2の加熱処理を施すことで、酸化物半導体層の側面が真空に曝されることを防ぎ、酸化物半導体層中の欠陥(酸素欠損)を少なくして半導体装置を作製する。該半導体装置はTGBC(Top Gate Bottom Contact)構造とする。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】高速動作可能な半導体装置を提供する。また、短チャネル効果による電気特性の変動が生じにくい半導体装置を提供する。

【解決手段】トランジスタの半導体層に結晶性を有する酸化物半導体を用い、該半導体層にチャネル形成領域とソース領域とドレイン領域を形成する。ソース領域及びドレイン領域は、ゲート電極をマスクとして、半導体層に第15族元素のうち一種類または複数種類の元素を添加する自己整合プロセスにより形成する。ソース領域及びドレイン領域に、ウルツ鉱型の結晶構造を付与することができる。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体膜をチャネル形成領域に用いたトランジスタにおいて、短チャネル効果による電気特性の変動を抑制し、微細化した半導体装置を提供する。また、オン電流を向上させた半導体装置を提供する。

【解決手段】非晶質領域である一対の第2の酸化物半導体領域と、一対の第2の酸化物半導体領域に挟まれた第1の酸化物半導体領域と、を有する酸化物半導体膜と、ゲート絶縁膜と、ゲート絶縁膜を介して第1の酸化物半導体領域上に設けられるゲート電極と、を有する半導体装置において、第2の酸化物半導体領域には、水素または希ガスのいずれかの元素が添加されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の特性を向上させる。

【解決手段】本発明の半導体装置は、面方位が(110)のシリコン基板1と、pMIS領域1Bに形成されたpチャネル型電界効果トランジスタを有する。このpチャネル型電界効果トランジスタは、ゲート絶縁膜3を介して配置されたゲート電極GE2と、ゲート電極の両側のシリコン基板1中に設けられた溝g2の内部に配置され、Siより格子定数が大きいSiGeよりなるソース・ドレイン領域と、を有する。上記溝g2は、ゲート電極側に位置する側壁部において、面方位が(100)の第1の斜面と、第1の斜面と交差する面方位が(100)の第2の斜面と、を有する。上記構成によれば、基板の表面(110)面と(100)面とのなす角は45°となり、比較的鋭角に第1斜面が形成されるため、効果的にpチャネル型のMISFETのチャネル領域に圧縮歪みを印加することができる。

(もっと読む)

半導体装置

【課題】本発明は、SOIにおいて適したゲッタリング方法を適用して得られる半導体装置を提供する。

【解決手段】埋め込み酸化膜と、埋め込み酸化膜上に表面シリコン層を有するSOI構造を有する半導体装置において、埋め込み酸化膜上に、表面シリコン層を活性層として有するトランジスタと、素子分離絶縁膜を有し、素子分離絶縁膜上に容量が形成されており、素子分離絶縁膜に希ガス元素又は金属元素が含まれていることを特徴とする半導体装置とする。

(もっと読む)

集積回路およびその形成方法

【課題】製造コストを良好に減少できる集積回路およびその形成方法を提供する。

【解決手段】集積回路は、第1のメモリアレイ、および第1のメモリアレイに接続された論理回路を含み、第1のメモリアレイの全てのメモリセルの全ての活性トランジスタおよび論理回路の全ての活性トランジスタは、フィン電界効果トランジスタ(FinFET)であり、第1の縦方向に沿って配置されたゲート電極を有する。FinFETs300a〜300cは、基板301上に配置され得る。基板301は、複数の活性領域305a〜305cを含み得る。活性領域305a〜305cは、基板301の表面301a上の非平面活性領域であり得る。

(もっと読む)

半導体装置

【課題】記憶保持期間において、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体以外の半導体材料が用いられた第1のチャネル形成領域を有する第1のトランジスタ160と、第1のトランジスタ160の上方の、酸化物半導体材料が用いられた第2のチャネル形成領域を有する第2のトランジスタ162と、容量素子164と、を有し、第2のトランジスタ162の第2のソース電極または第2のドレイン電極の一方と、容量素子164の電極の一方とは、電気的に接続される。

(もっと読む)

集積回路構造、及び集積回路の製造方法

【課題】異なるフィン高さを有するFinFETを提供する。

【解決手段】集積回路構造は、第1装置領域の第1部分と、第2装置領域の第2部分と、を有する半導体基板からなる。第1半導体フィンは半導体基板上にあり、第1フィン高さを有する。第2半導体フィンは半導体基板上にあり、第2フィン高さを有する。第1フィン高さは第2フィン高さより高い。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

【課題】

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。一部の構造及び方法は、大部分が、既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。一部の構造及び方法は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。様々な効果を達成するようDDCを構成する手法が数多く存在し得る。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】4個の島状半導体を用いてSRAMを構成することにより、高集積なSGTを用いたSRAMからなる半導体装置を提供することを目的とする。

【解決手段】第1の島状半導体層の周囲上に少なくとも一部に接して第1のゲート絶縁膜が存在し、第1のゲート絶縁膜に第1のゲート電極の一面が接し、該第1のゲート電極の他面に第2のゲート絶縁膜が接し、第2のゲート絶縁膜に少なくとも第2の半導体層が接して、第1の島状半導体層の上部に配置された第1の第1導電型高濃度半導体層と、第1の島状半導体層の下部に配置された第2の第1導電型高濃度半導体層と、第2の半導体層の上部に配置された第1の第2導電型高濃度半導体層と、第2の半導体層の下部に配置された第2の第2導電型高濃度半導体層と、を有することを特徴とするインバータを用いたSRAMにより、上記課題を解決する。

(もっと読む)

半導体装置およびその製造方法

【課題】製造工程の増加を抑えて、通常のコンタクトとシェアードコンタクトとをそれぞれ良好なコンタクト特性を有するようにする。

【解決手段】半導体装置100は、第1の不純物拡散領域106aに接続するとともに、第1のゲート電極112aとは接続しないように形成された第1のコンタクト124と、第2のゲート電極112bおよび第2の不純物拡散領域106bに共通して接続するように形成された第2のコンタクト126とを含む。第1のコンタクト124および第2のコンタクト126は、それぞれ、層間絶縁膜122の表面から基板101に向かう途中の位置でテーパー角度が小さくなるように変化する形状を有し、第2のコンタクト126においてテーパー角度が変化する位置が、第1のコンタクト124においてテーパー角度が変化する位置よりも基板101に近い。

(もっと読む)

独立したソース及びドレイン設計を有するトライゲートSRAM、及びそれから成るデバイス

静的ランダムアクセスメモリ(SRAM)回路は、パス領域のためのソース及びドレイン(S/D)区間を含む少なくとも1つのアクセスデバイスと、少なくとも1つのプルアップデバイスと、プルダウン領域のためのS/D区間を含む少なくとも1つのプルダウンデバイスとを有する。SRAM回路は、プルダウン領域の外部抵抗(Rext)がパス領域の外部抵抗(Rext)よりも低くなるよう構成される。このようなSRAM回路を実現するプロセスはS/Dエピタキシを含む。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】SRAMにおいてNMOS及びPMOSトランジスタのバランスを確保して、PMOSトランジスタの閾値電圧を高くできる半導体装置及びその製造方法を提供する。

【解決手段】メモリ領域において、基板の第1半導体領域(12,13)の第1チャネル形成領域上に第1ゲート絶縁膜(20,21)を介して第1ゲート電極が形成され、第1半導体領域に第1ソースドレイン領域(16,17)が形成されて第1トランジスタが形成され、ロジック領域において、基板の第2半導体領域(14,15)の第2チャネル形成領域上に第2ゲート絶縁膜(22,23)を介して第2ゲート電極が形成され、第2半導体領域に第2ソースドレイン領域(18,19)が形成されて第2トランジスタが形成され、第1ゲート電極の第1ゲート絶縁膜に接する部分が金属(40,41)からなり、第2ゲート電極の第2ゲート絶縁膜に接する部分が半導体(26,27)からなる。

(もっと読む)

ゲート型横型サイリスタベースランダムアクセスメモリ(GLTRAM)セルを製造するための方法

【解決手段】

ゲート型横型サイリスタベースメモリデバイス(gltram)を製造するための方法が提供される。半導体層(406)内の第1の伝導性タイプの第1、第2、第3及び第4のウエル領域(463,471,486,493)を含む半導体層(406)が設けられる。第1のゲート構造(465/408)は第1のウエル領域(463)上にあり、第2のゲート構造(475/408)は第2のウエル領域(471)上にあり、第3のゲート構造(485/408)は第3のウエル領域(486)上にあり且つ第2のゲート構造(475/408)と一体であり、第4のゲート構造(495/408)は第4のウエル領域(493)上に配置される。第1のゲート構造(465/408)の第1の側壁(414)及び第2乃至第4のゲート構造(475/408,485/408,495/408)の側壁(412,413,416,417,418,419)に隣接して側壁スペーサ(469)が形成される。また、第1のウエル領域(463)の部分(468)及び第1のゲート構造(465/408)の部分を覆う絶縁スペーサブロック(467)が形成される。絶縁スペーサブロック(467)は第1のゲート構造(465/408)の第2の側壁(415)に隣接する。第1のゲート構造(465/408)に隣接して第1のソース領域(472)が形成され、第1及び第2のゲート構造(465/408,475/408)の間に共通ドレイン/カソード領域(474/464)が形成され、第3のゲート構造(485/408)に隣接して第2のソース領域(482)が形成され、第3及び第4のゲート構造(485/408,495/408)の間に共通ドレイン/ソース領域(484/492)が形成され、第4のゲート構造(495/408)に隣接してドレイン領域(494)が形成される。第1のゲート構造(465/408)に隣接する絶縁スペーサブロック(467)の下で第1のウエル領域(463)内に延在する第1のベース領域(468)が形成され、第1のベース領域(468)に隣接する第1のウエル領域(463)内に延在するアノード領域(466)が第1のウエル領域(463)内に形成される。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】リーク電流を低減することのできる、スタティック型のメモリセルを含む半導体記憶装置およびその製造方法を提供する。

【解決手段】半導体記憶装置は、複数のメモリセルと、複数のビット線と、複数のワード線と、制御用n型トランジスタTr1とを備えている。制御用n型トランジスタTr1は、複数のワード線または複数のビット線の各々の電位を制御するためのものである。複数のメモリセルの各々は、データを保持するためのメモリセル用n型トランジスタTr2を有している。メモリセル用n型トランジスタTr2のゲート電極GE2におけるn型不純物の濃度は、制御用n型トランジスタTr1のゲート電極GE1におけるn型不純物の濃度よりも低い。この結果、メモリセル用n型トランジスタ(トランジスタTr2)の閾値電圧Vthを高くすることができるので、半導体記憶装置のリーク電流を低減することができる。

(もっと読む)

半導体装置

【課題】メモリセル領域とその周辺回路領域とを含んで構成される半導体装置において、メモリを構成するMOSFETのしきい値のばらつきを小さくできる半導体装置を提供する。

【解決手段】それぞれMOSFETを有してなる複数のメモリセルが形成されたメモリセル領域とMOSFETを回路が形成された周辺回路領域を備えた半導体装置において、メモリセル領域のMOSFETは、周辺回路領域の少なくとも一部のMOSFETとは異なるゲート構造を有し、ゲート絶縁膜及びゲート電極のうちの少なくとも一方の組成が一部のMOSFETとは異なる。

(もっと読む)

半導体装置の製造方法

【課題】MOSFETにおいて、ショートチャネル効果の抑制と移動度向上を両立させることを可能とする。

【解決手段】半導体基板13上にダミーゲート絶縁膜31を介してダミーゲート34を形成する工程と、ダミーゲート34の両側の半導体基板13にソース・ドレイン不純物領域23,24を形成する工程と、ダミーゲート34の両側の半導体基板13上にエクステンション領域25,26を形成する工程と、ダミーゲート34直下のソース側にソース不純物領域23のオーバーラップ領域27を形成する工程と、ダミーゲート34を除去し、該除去領域に露出したダミーゲート絶縁膜31を除去する工程と、除去領域に露出した半導体基板13にリセス形状15を形成する工程と、リセス形状15を形成した半導体基板13上にゲート絶縁膜21とゲート電極22とを順次形成する工程とを備えている。

(もっと読む)

半導体装置

【課題】直接相互拡散による特性劣化を低減することの可能な半導体装置を提供する。

【解決手段】p型ポリシリコン層14A1およびシリサイド層14A2を有するゲート電極14Aと、n型ポリシリコン層14B1およびシリサイド層14B2を有するゲート電極14Aとを備える。p型ポリシリコン層14A1およびn型ポリシリコン層14B1は、互いに接合された接続部Pを素子分離層12の直上に有し、p型ポリシリコン層14A1およびn型ポリシリコン層14B1の少なくとも一方は、素子分離層12の直上に狭窄部17を有する。狭窄部17は、p型ポリシリコン層14A1およびn型ポリシリコン層14B1のうち素子分離層12との非対向領域の幅方向断面積よりも小さな幅方向断面積を有する。

(もっと読む)

1 - 20 / 34

[ Back to top ]