Fターム[5F083EP06]の内容

半導体メモリ (164,393) | EPROM、EEPROMの構造 (21,423) | 電荷蓄積機構 (5,261) | FGを有するもの (3,098) | 不純物濃度 (28)

Fターム[5F083EP06]に分類される特許

1 - 20 / 28

不揮発性半導体記憶装置及びその製造方法

【課題】 書き込み動作及び消去動作の両方の特性向上を図る。

【解決手段】 実施形態による不揮発性半導体記憶装置は、半導体基板11と、半導体基板上に形成されたゲート絶縁膜12と、ゲート絶縁膜上に形成され、13族元素であるP型不純物を含有するポリシリコンからなり、下部膜13aと下部膜上に積層された上部膜13bとを有するフローティングゲート電極13と、フローティングゲート電極上に形成された電極間絶縁膜16と、電極間絶縁膜上に形成されたコントロールゲート電極17と、を具備し、上部膜におけるP型不純物の濃度又は活性化濃度は、下部膜におけるP型不純物の濃度又は活性化濃度より高い。

(もっと読む)

半導体記憶装置及び半導体記憶素子

【課題】素子の面積を増大させることなく、かつ、コントロールゲート電圧を制御しなくとも、低電圧で書き込み量を大幅に増やすことが可能であり、また、安定して十分な書き込みを行うことが可能である不揮発性半導体装置を提供すること。

【解決手段】ドレインアバランシェホットエレクトロンにより書き込みを行う半導体記憶素子であって、第1導電型の半導体基板に形成された第2導電型の第1の半導体層と、前記第1の半導体層上に絶縁膜を介して設けられたフローティングゲートと、前記フローティングゲート下部の前記第1の半導体層の表面に形成されたチャネル領域と、前記チャネル領域に接触するように前記第1の半導体層上に設けられた第1導電型のソース領域及びドレイン領域とを有するMOSトランジスタであって、前記チャネル領域が2種類以上のキャリア濃度の分布をもつ半導体記憶素子とした。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】素子分離絶縁膜の形成時に、浮遊ゲート電極膜の基板に対面する部分の幅寸法が細くなってしまうことを防止する。

【解決手段】本実施形態の半導体装置は、半導体基板と、前記半導体基板上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成され、浮遊ゲート電極膜、電極間絶縁膜および制御ゲート電極膜が積層されたゲート電極とを備えた。そして、前記浮遊ゲート電極膜を、窒素を含む下層シリコン層と窒素を実質的に含まない上層シリコン層とを有する多結晶シリコン層で構成し、前記下層シリコン層のゲート幅方向の寸法を、前記上層シリコン層のゲート幅方向の寸法よりも大きく構成した。

(もっと読む)

NAND型不揮発性メモリのデータ消去方法

【課題】NAND型不揮発性メモリを提供する。

【解決手段】ビット線と、ソース線と、複数の不揮発性メモリが直列に接続されたNAND型セルと、選択トランジスタと、を有し、不揮発性メモリは、第1の絶縁膜を介した半導体上の電荷蓄積層と、第2の絶縁膜を介した電荷蓄積層上の制御ゲートと、を有し、NAND型セルの一方の端子は、選択トランジスタを介して、ビット線に接続され、NAND型セルの他方の端子は、ソース線に接続されたNAND型不揮発性メモリであって、第1の絶縁膜は、半導体に酸素雰囲気で高密度プラズマ処理を行った後、窒素雰囲気で高密度プラズマ処理を行うことで形成されるNAND型不揮発性メモリ。

(もっと読む)

半導体装置の製造方法

【課題】シリコン膜のエッチング時に膜厚方向中央部での括れの発生を防止する。

【解決手段】多結晶シリコン膜3の上部と下部はノンドープ層3a、3cにてそれぞれ構成され、多結晶シリコン膜3の中央部は不純物ドープ層3bにて構成され、多結晶シリコン膜3に凹部M1を形成した後、多結晶シリコン膜3の酸化処理にて凹部M1の表面にシリコン酸化膜6を形成し、凹部M1下の多結晶シリコン膜3を除去する。

(もっと読む)

半導体メモリ装置

【課題】短チャネルでも動作するフローティングゲートを有する半導体メモリ装置を提供する。

【解決手段】フローティングゲート104に窒化インジウム、窒化亜鉛等の仕事関数が5.5電子ボルト以上の高仕事関数化合物半導体を用いる。このことにより、基板101とフローティングゲート104の間のフローティングゲート絶縁膜103のポテンシャル障壁が従来のものより高くなり、フローティングゲート絶縁膜103を薄くしても、トンネル効果による電荷の漏洩を低減できる。フローティングゲート絶縁膜103をより薄くできるのでチャネルをより短くできる。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を提供する。

【解決手段】フローティングゲート電極は、高い不純物濃度領域と低い不純物濃度領域とからなり、高い不純物濃度領域は、コントロールゲート絶縁膜と接する部分に配置し、低い不純物濃度領域はトンネル絶縁膜と接する領域に配置し、フローティングゲート電極のコントロールゲート絶縁膜と接する表面部分には微細凹凸を形成した。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書 き換え可能な半導体不揮発性メモリ装置を得る。

【解決手段】ドレイン領域内のトンネル領域とフローティングゲート電極領域との間には、トンネル絶縁膜が設けられており、トンネル領域のエッジ近傍のフローティングゲート電極の不純物濃度は、その他の箇所のフローティングゲート電極の不純物濃度に比べて低く設定した。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書 き換え可能な半導体不揮発性メモリ装置を得ることを目的とする。

【解決手段】電気的書き換え可能な半導体不揮発性メモリにおいて、第2導電型のドレイン領域内のトンネル領域と前記フローティングゲート電極領域との間には、トンネル絶縁膜が設けられており、前記フローティングゲート電極は第1導電型の導電体で形成されている電気的書き換え可能な半導体不揮発性メモリ装置。

(もっと読む)

半導体記憶装置

【課題】書き込み特性及び電荷保持特性に優れたメモリセル(セルトランジスタ)を具備する半導体記憶装置、或いは、メモリセルと共に製造するのに適した選択又は周辺トランジスタの提供。

【解決手段】セルトランジスタ201は、基板101上に、FNトンネル膜として機能するゲート絶縁膜111、最下層の浮遊ゲートに相当する第1の浮遊ゲート112を備える。更に、FNトンネル膜として機能する第1の浮遊ゲート間絶縁膜113を介して形成され、前記セルトランジスタ内の最下層の浮遊ゲートと最上層の浮遊ゲートとの間に介在する第2の浮遊ゲート114を備える。更に、FNトンネル膜として機能する第2の浮遊ゲート間絶縁膜115を介して形成され、前記セルトランジスタ内の最上層の浮遊ゲートに相当する第3の浮遊ゲート116を備える。更に、電荷ブロック膜として機能するゲート間絶縁膜117を介して形成された制御ゲート118を備える。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】素子分離絶縁膜の埋め込み後の化学機械研磨法による研磨で、浮遊ゲート電極をストッパ膜として使用できるようにする。

【解決手段】シリコン基板1にゲート絶縁膜4、下層多結晶シリコン膜5a、上層多結晶シリコン膜5bを積層形成する。上層多結晶シリコン膜5bは、成膜時に炭素を1×1018atoms/cm3以上例えば2×1020〜2×1021atoms/cm3の範囲の濃度で添加される。素子分離溝1bを形成した後に、素子分離絶縁膜2を埋め込み、化学機械研磨法の研磨で素子分離溝1b内以外の部分を除去する。この時、上層多結晶シリコン膜5bがスクラッチの発生を抑制できるストッパ膜として利用でき、シリコン窒化膜などを不要とした構成とすることができる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】微細化が可能な消去ゲートを備える不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板1上に形成されたフローティングゲート3と、フローティングゲート3上に形成された消去ゲート10と、半導体基板1表層のチャネル領域上にフローティングゲート3と並設され、フローティングゲート3及び消去ゲート10の一方の側面に形成されたコントロールゲート22と、フローティングゲート3及び消去ゲート10の他方の側面に対応する位置の半導体基板1内に形成された第1拡散層15と、第1拡散層15に接続され、フローティングゲート3及び消去ゲート10の側方に位置するように第1拡散層15上に形成されたプラグ17と、コントロールゲート22に隣接する位置の半導体基板1内に形成された第2拡散層23と、を備える。

(もっと読む)

半導体装置

【課題】浮遊ゲートをもち制御ゲートを備えていない不揮発性メモリセルを備えた半導体装置において、その不揮発性メモリセルの読出し特性を飛躍的に改善する。

【解決手段】不揮発性メモリセルは、P型半導体基板1上に形成された書込みメモリゲート酸化膜9及び書込みメモリゲート酸化膜9上に形成された電気的に浮遊状態のポリシリコンからなる書込み浮遊ゲート11をもつPMOS書込みトランジスタと、P型半導体基板1上に形成された読出しメモリゲート酸化膜15及び読出しメモリゲート酸化膜15上に形成された電気的に浮遊状態のポリシリコンからなる読出し浮遊ゲート17をもつNMOS読出しトランジスタを備えている。書込み浮遊ゲート11と読出し浮遊ゲート17は電気的に接続されている。不揮発性メモリセルへの書込みはPMOS書込みトランジスタによって行なわれ、読出しはNMOS読出しトランジスタによって行なわれる。

(もっと読む)

不揮発性半導体記憶装置

【課題】シリサイド領域を形成し、かつ、チャネル形成領域の金属元素濃度増大を防ぎ、記憶素子の信頼性を向上させることを課題とする。

【解決手段】ソース領域及びドレイン領域と、該ソース領域及びドレイン領域の間に設けられたチャネル形成領域を有する半導体層と、前記半導体層上に、第1の絶縁層、第1のゲート電極、第2の絶縁層、第2のゲート電極が順次重ね合わせて設けられ、前記ソース領域及びドレイン領域は、その一部又は全てがニッケルシリサイド層で形成され、前記第1のゲート電極は、絶縁膜で周囲が覆われていると共に、希ガス元素を含む不揮発性半導体記憶装置に関する。

(もっと読む)

半導体装置及びその製造方法

【課題】トンネル絶縁膜とフローティングゲート電極との間の楔状酸化膜の形成を抑制することが可能な半導体装置を提供する。

【解決手段】半導体基板10と、半導体基板上に形成されたトンネル絶縁膜20と、トンネル絶縁膜上に形成された下層半導体膜31と、不純物元素を含有した上層半導体膜33と、下層半導体膜と上層半導体膜との間に形成され且つ上層半導体膜に含有された不純物元素の下層半導体膜への拡散を抑制するバリア絶縁膜32とを含むフローティングゲート電極30と、フローティングゲート電極上に形成された電極間絶縁膜40と、電極間絶縁膜上に形成されたコントロールゲート電極50とを備える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】多結晶シリコンの空乏化を抑制して微細化ができる半導体装置および半導体装置の製造方法を提供する。

【解決手段】多結晶シリコンからなる第1の層を有する制御ゲート電極を備え、前記第1の層は、不純物を含んだ多結晶シリコンからなる第1の膜をエッチバックしてその膜厚を減らしたものであって、前記第1の膜の不純物活性化率を保持していることを特徴とする半導体装置が提供される。また、絶縁膜上に設けたアモルファスシリコン膜を熱処理して、不純物を含んだ多結晶シリコンからなる第1の膜を形成する工程と、前記第1の膜をエッチバックして、前記第1の膜の膜厚を減らす工程と、を備えたことを特徴とする半導体装置の製造方法が提供される。

(もっと読む)

ポリシリコン浮遊ゲートにPN接合を形成した不揮発性メモリ・セル及びそのメモリ・セルを製造する方法

【課題】浮遊ゲート型の不揮発性メモリ・セル及びそのメモリ・セルを製造する方法を提供する。

【解決手段】ソース側(13B)上に軽くドーピングされたホウ素と、ドレイン側(13A)+チャネル領域(Ch)上に高度にドーピングされたヒ素又はリンとを有するP−N接合多結晶シリコン浮遊ゲート(13)により、ソース(11)とドレイン(12)とを有するメモリ・セル(10)のアレーを形成する。多結晶浮遊ゲート(13)におけるP−N接合(JU)を使用することにより、メモリ・セル(10)がデプリーションへ移行するのを阻止し、稠密な分布の消去しきい電圧VTを発生させることにより過消去特性を得ると共に、前記ゲート酸化物(30)を介する電子の移動が少ないので、デバイス寿命を改善する。

(もっと読む)

不揮発性記憶素子の形成方法

【課題】セル特性の分散を減少させることができるNAND型フラッシュメモリ不揮発性記憶素子の形成方法を提供する。

【解決手段】広い間隔で配列された第1マスクパターン120d、120c、120sを形成した後に、間隔調節膜130をコンフォーマルに形成し、間隔調節膜130により第1マスクパターン120d、120c、120sの間に各々定義される溝132、134を充填する第2マスクパターン140c、140gを形成する。これにより、接地選択ゲートライン140g、セルゲートライン140c及びストリング選択ゲートライン120sが全て等間隔で配列されるように形成することができる。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】書き込み特性と消去特性をともに向上させることを可能にする。

【解決手段】半導体基板2と、半導体基板に離間して形成されたソース領域4aおよびドレイン領域4bと、ソース領域とドレイン領域との間の半導体基板上に形成された第1絶縁膜8と、第1絶縁膜上に形成され伸張歪みを有する半導体導電材料層を含む浮遊電極10と、浮遊電極上に形成された第2絶縁膜12と、第2絶縁膜上に形成された制御電極14と、を備え、浮遊電極の伸張歪みは、第2絶縁膜から第1絶縁膜に向かうに従って次第に小さくなっており、第2絶縁膜との界面において0.01%以上の歪みを有し、第1絶縁膜との界面において歪みが0.01%未満である。

(もっと読む)

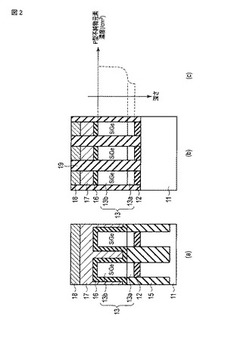

基板トレンチ内にスペーサから形成されたフローティングゲートを有する不揮発性メモリセルアレイ

所定数のフラッシュメモリセルアレイによって占められる集積回路領域を低減するために、フローティングゲート電荷蓄積素子(103、105、111、113)が、基板トレンチ(60、61)の側壁に沿って配置され、ドープされたポリシリコンスペーサから形成されていることが好ましい。デュアルフローティングゲートメモリセルアレイが、一例としてこの構造を有するセルを含む。メモリセルのNANDアレイが、このセル構造の用途の他の例である。メモリセルおよびアレイ構造は、具体的に様々なNORおよびNANDメモリセルアレイアーキテクチャに対する広い用途を有している。  (もっと読む)

(もっと読む)

1 - 20 / 28

[ Back to top ]