Fターム[5F083EP28]の内容

半導体メモリ (164,393) | EPROM、EEPROMの構造 (21,423) | 制御機構 (7,428) | CGを有するもの (4,415) | CGを複数有するもの (58)

Fターム[5F083EP28]に分類される特許

1 - 20 / 58

メモリ用シフトレジスタ

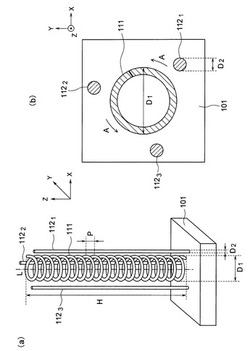

【課題】大容量なメモリ用シフトレジスタを提供する。

【解決手段】メモリ用シフトレジスタは、基板101と、基板101上に形成され、基板101の主面に垂直な軸Lの周りを回転する螺旋形状を有するチャネル層111とを備える。さらに、メモリ用シフトレジスタは、基板101上に形成され、軸Lに平行な方向に延びており、チャネル層111内の電荷を転送するために使用される3本以上の制御電極1121,1122,1123を備える。

(もっと読む)

不揮発性メモリ及びその製造方法

【課題】

不揮発性メモリ構造を提供する。

【解決手段】

必要に応じて、LDD領域が、アクティブ領域のゲートチャネル領域の保護のためのマスクを用いてイオン注入によって形成され得る。2つのゲートが、互いに離隔され、アクティブ領域の中央領域の2つの側方のそれぞれでアイソレーション構造上に配設される。これら2つのゲートの各々は、その全体がアイソレーション構造上に配置されてもよいし、部分的にアクティブ領域の中央領域の側方部分に重なってもよい。電荷トラップ層及び誘電体層が、格納ノード機能を果たすように、2つのゲートの間且つアクティブ領域上に形成される。これらは更に、スペーサとして機能するように、2つのゲートの全ての側壁上に形成されてもよい。ソース/ドレイン領域が、ゲート及び電荷トラップ層の保護のためのマスクを用いて、イオン注入によって形成される。

(もっと読む)

半導体不揮発性メモリ

【課題】 本発明は、不揮発性メモリ・セルにおける電荷貯蔵層を論理工程において形成する方法を提供する。

【解決手段】 論理工程において不揮発性メモリ・セルにおける電荷貯蔵層を形成する方法は、基板のアクティブ領域の上にセレクト・ゲートを形成するステップ、その基板のアクティブ領域に部分的に重なる長いポリシリコン・ゲートを形成するステップ、及びその長いポリシリコン・ゲートの間に電荷貯蔵層を充填するステップを含む。

(もっと読む)

不揮発性半導体記憶装置、不揮発性半導体記憶装置の動作方法

【課題】チップ面積の増大を抑制しつつ、安定的に動作するスプリットゲート型不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体メモリのベリファイステップを以下の手順で実行する。(a)通常読み出し動作のワードゲート電圧よりも低いベリファイ電圧を、ワードゲートに供給する。(b)通常読み出し動作のコントロールゲート電圧を、コントロールゲートに供給する。(c)そのベリファイ電圧とそのコントロールゲート電圧とに応じて流れる電流が、通常読み出し動作のときの参照電流に一致するか否かを判定する。TwinMONOSセルの消去ベリファイ時に、ワードゲートの電圧を低くすることで、コントロールゲートの負電圧を利用せずに消去ベリファイを可能にする。

(もっと読む)

固体撮像素子及び撮像装置

【課題】ドレイン領域等の不純物拡散領域からフローティングゲートに電荷が注入されてしまうことを防止でき、S/Nを向上できる固体撮像素子及び撮像装置を提供する。

【解決手段】半導体基板に配列された複数の画素部が配列され、画素部が、半導体基板に形成された光電変換部と半導体基板の上方に設けられた電荷蓄積領域と、電荷蓄積領域に電荷を蓄積させて、該電荷に応じた信号を読み出すトランジスタ構造とを備え、トランジスタ構造がソース領域及びドレイン領域を含み、ソース領域及びドレイン領域と光電変換部との間の半導体基板に、ソース領域及びドレイン領域と光電変換部との間で移動する電荷に対して電位勾配のポテンシャル障壁となる障壁層を備える。

(もっと読む)

不揮発性半導体記憶装置及び不揮発性半導体記憶装置の製造方法

【課題】ビット線方向のセル間干渉を解消する不揮発性半導体記憶装置及び不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板1と、半導体基板1を複数の素子領域に分離する素子分離絶縁膜2と、半導体基板1の素子領域上に形成されたトンネル絶縁膜3と、トンネル絶縁膜3上に形成されたフローティングゲート電極4と、積層絶縁膜5を介して、フローティングゲート電極4上及びチャネル幅方向に隣接するフローティングゲート電極4間に形成された第1コントロールゲート電極6と、半導体基板1の素子領域のチャネル幅方向に面する側面に形成されたアシスト絶縁膜7と、アシスト絶縁膜7を介して、複数の素子領域間に形成された第2コントロールゲート電極8と、を備えている。

(もっと読む)

逆自己整合方式を利用したツインONO形態のSONOSメモリ素子製造方法

【課題】プログラム及び消去時に生成される電子及びホールの分布を意図的に調節でき、同時に短チャンネル現象を減らせて、0.10μm以下のメモリゲート長でも安定した2ビット特性を有するSONOS形態のメモリ素子を製造できるSONOSメモリ素子製造方法を提供する。

【解決手段】スペーサを使用した自己整合方式でゲート下部のONO誘電層を、中間部分が分離され、分離された両側が対称的なツインONO誘電層構造に形成する。ONO誘電層が分離された中間部分には、ONO誘電層と独立してゲート誘電層を形成する。

(もっと読む)

EEPROM

【課題】2つのメモリトランジスタに同一のデータを確実に書き込むことができる、W(ダブル)セル方式のEEPROMを提供する。

【解決手段】半導体層には、第1不純物領域8、第2不純物領域9、第3不純物領域10、第4不純物領域11、第5不純物領域12および第6不純物領域13が形成されている。セレクトゲート15は、第1不純物領域8と第2不純物領域9との間の領域に、第1絶縁膜14を挟んで対向している。第1フローティングゲート16は、第2不純物領域9と第3不純物領域10との間の領域および第5不純物領域12に、第1絶縁膜14を挟んで対向している。第2フローティングゲート20は、第3不純物領域10と第4不純物領域11との間の領域および第6不純物領域13に、第1絶縁膜14を挟んで対向している。第5不純物領域12および第6不純物領域13は、第2不純物領域9と接続されている。

(もっと読む)

撮像装置及び固体撮像素子の駆動方法

【課題】ノイズを抑えながら電荷蓄積部内の電荷を消去することが可能な撮像装置及び固体撮像素子の駆動方法を提供する。

【解決手段】光電変換部3を含む画素部100を多数有する撮像装置であって、画素部100は、光電変換部3で発生した電荷を蓄積するための半導体基板上方に設けられたフローティングゲートFGを含む書き込みトランジスタWTと読み出しトランジスタRTを有し、複数の画素部100からなるグループ毎に、該グループ内の画素部100の光電変換部3で発生した電荷を該画素部100内の書き込みドレインWD又は読み出しドレインRDに排出する第一の電荷排出駆動を独立に行って、各グループの露光期間の開始タイミングを制御する制御部40を備える。

(もっと読む)

半導体素子とその製造及び動作方法

【課題】 半導体素子とその製造及び動作方法を提供する。

【解決手段】 相異なるナノ構造体を含む半導体素子である。例えば、半導体素子は、ナノワイヤーで形成された第1構成要素とナノパーティクルで形成された第2構成要素とを含む。ここで、ナノワイヤーは、双極性の炭素ナノチューブでありうる。第1構成要素は、チャンネル層であり、第2構成要素は、電荷トラップ層であるが、この場合、前記半導体素子は、トランジスタやメモリ素子でありうる。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリを有する半導体装置の記憶容量を増加させる。

【解決手段】シリコン基板1に形成された不揮発性メモリセルNVM1は、主面s1上にONO構造の第1電荷蓄積膜MI1を隔てて形成された第1メモリゲート電極MG1と、同主面s1上にONO構造の第2電荷蓄積膜MI2を隔てて形成された第2メモリゲート電極MG2とを有する。各電極は、第2電荷蓄積膜MI2を挟んで隣り合って配置されている。この不揮発性メモリセルNVM1は、それぞれ独立して1ビットの情報を記憶する機能を有する第1電荷蓄積膜MI1と第2電荷蓄積膜MI2とを有することで、少なくとも2ビットの情報を記憶する。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】浮遊ゲート電極の高さを低くして制御ゲート電極の形成を容易にしつつ、浮遊ゲート電極と制御ゲート電極とのカップリング比を増加させるとともにメモリセルトランジスタ間の干渉効果を低減することが可能な不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板平面上で第2の方向に隣接する浮遊ゲート電極2間の素子分離領域上には、第1の絶縁膜3が形成されている。制御ゲート電極1は、素子分離領域上の第1の方向の幅D1が素子領域上の第1の方向の幅D2よりも広い。

(もっと読む)

不揮発性半導体記憶装置及びその作製方法

【課題】書き込みや消去を繰り返し行った場合であっても、読み出し不良を抑制することを目的の一とする。又は、メモリトランジスタの面積の増大を抑制しつつ、書き込み電圧、消去電圧を低減することを目的の一とする。

【解決手段】基板上に設けられた書き込み動作及び消去動作に用いる第1の半導体層及び読み出し動作に用いる第2の半導体層上に、絶縁膜を介してフローティングゲートとコントロールゲートを設け、第1の半導体層を用いてフローティングゲートへの電子の注入・放出を行い、第2の半導体層を用いて読み出しを行う。

(もっと読む)

半導体装置の製造方法

【課題】エッチングによって形成されるサイドウォールゲートのばらつきを抑制する技術を提供する。

【解決手段】第1の工程では、半導体基板の表面を露出する第1開口部を有する材料を形成する。第2の工程では、材料の上面と材料の側面と半導体基板の表面とに、第1絶縁膜と導電体膜とを順に形成する。第3の工程では、導電体膜表面に、第2開口部を有する第1導電体保護膜を形成し、第2開口部を第2絶縁膜で埋める。第4の工程では、第2絶縁膜をマスクに第1導電体保護膜を除去する。第5の工程では、第1導電体保護膜と第2絶縁膜とをマスクとして、導電体膜を除去する。第6の工程では、第2開口部の第2絶縁膜を除去した後、露出している導電体膜の表面に第2導電体保護膜を形成する。第7の工程では、第1導電体保護膜を除去した後、第2導電体保護膜をマスクにして、導電体を選択的に除去してゲートを形成する。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリセル面積を増加することなく、メモリトランジスタの書き込み電圧および消去電圧を低減する不揮発性半導体記憶装置を提供する。

【解決手段】メモリセルには、第1の島状半導体領域102、フローティングゲート109、コントロールゲート111が有するメモリトランジスタが設けられている。さらに、フローティングゲート109の下方には、絶縁膜を介して第2の島状半導体領域101が形成されている。第2の島状半導体領域101は、コントロールゲート111に電気的に接続されているため、第2の島状半導体領域101とフローティングゲート109間に静電容量が形成される。この静電容量はメモリトランジスタのカップリング比の増加に寄与するため、メモリセルの面積を増加することなく、カップリング比を高くすることが可能になる。また、カップリング比を低下することなく、メモリセルの面積を縮小することが可能になる。

(もっと読む)

NAND型フラッシュメモリおよびその製造方法

【課題】隣接するメモリセルMC間の干渉効果を低減ことが可能なNAND型フラッシュメモリを提供する。

【解決手段】NAND型フラッシュメモリ100のメモリセルは、素子領域上にゲート絶縁膜を介して形成された柱状の浮遊ゲートと、素子領域のうち浮遊ゲートの両側に位置する領域に形成された拡散層と、浮遊ゲートの側面に形成されたIPD膜を介して前記浮遊ゲートの周囲を囲むように形成された制御ゲートと、を有する。

(もっと読む)

不揮発性半導体記憶装置

【課題】リテンション耐性の良好な不揮発性半導体記憶装置を提供する。

【解決手段】1つのメモリセルMCが導電性電荷蓄積層と絶縁性電荷蓄積層ECSとを有している。導電性電荷蓄積層はフローティング電位を有する第1のゲート電極層GE1であり、1対のソース/ドレイン領域SDに挟まれる半導体基板SUBの主表面上に第1のゲート絶縁層GI1を介して形成されている。絶縁性電荷蓄積層ECSは第2のゲート絶縁層GI2に含まれ、1対のソース/ドレイン領域SDに挟まれる半導体基板SUBの主表面上に形成されている。第1のゲート電極層GE1上のコントロールゲート部分CGと第2のゲート絶縁層GI2上のメモリゲート部分MGとは電気的に接続されている。

(もっと読む)

半導体記憶装置及びデータ転送方法

【課題】 不揮発性メモリ部から揮発性ラッチ回路へのデータ転送動作が不揮発性メモリ部の動作を制御する制御端子の電圧が高い領域でも正常に動作可能な半導体記憶装置を提供する。

【解決手段】 制御回路CNTが、ワード線WL1、Wl2に読み出し電圧Vwlを印加し、第1スイッチング素子Qn2、Qn3及び第2スイッチング素子Qn4を導通状態にした後、プリチャージ回路Qp1、Qp2によりデータノードSD、SDBをプリチャージした後、不揮発性メモリ部M1、M2の各電流量でデータノードを放電する第1プリセンス動作を行い、その後にワード線電圧を部分的或いは徐々に低下させ、揮発性ラッチ回路LCを活性化させて、データノード間の電圧差を予備的に増幅する第2プリセンス動作を行い、その後に、第1スイッチング素子をオフするか、ワード線への電圧印加を完全に停止するか何れか一方または両方の動作を行ってメインセンス動作を開始する。

(もっと読む)

不揮発性半導体記憶装置

【課題】短チャネル効果を抑制し、かつオン/オフ判別電流間の電圧差を低減できる不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板101上に第1の方向に沿って所定間隔を空けて形成された複数のトンネル絶縁膜103と、前記トンネル絶縁膜上に形成された第1の部分104a、及び前記第1の部分上に形成され前記第1の方向の長さが前記第1の部分より短い第2の部分104bをそれぞれ有する複数の浮遊ゲート電極104と、前記浮遊ゲート電極を覆うように形成されたゲート間絶縁膜106と、前記複数の浮遊ゲート電極の各々について前記第2の部分の前記第1の方向側壁部に前記ゲート間絶縁膜を介してそれぞれ形成された第1の制御ゲート電極107及び第2の制御ゲート電極107と、を備える。

(もっと読む)

不揮発性半導体記憶装置及びその動作方法

【課題】情報を記憶するための正のしきい値を有する複数の正の準位及び負のしきい値を有する複数の負の準位を設定することが可能な不揮発性半導体記憶装置及びその動作方法を提供する。

【解決手段】本発明の1態様による不揮発性半導体記憶装置は、半導体層の第1の主面側に設けられ、情報を記憶させるための正のしきい値電圧を有する複数の正の準位と負のしきい値電圧を有する複数の負の準位とを備えた電荷蓄積層を含む記憶素子と、前記半導体層の第2の主面側に前記記憶素子と対向して設けられ、前記負の準位に蓄積された情報を正のしきい値電圧を有する情報へと変換する電圧を印加する電極とを具備する。

(もっと読む)

1 - 20 / 58

[ Back to top ]