Fターム[5F083EP65]の内容

半導体メモリ (164,393) | EPROM、EEPROMの構造 (21,423) | 拡散領域 (1,645) | ドレイン領域 (815) | 素子分離領域下 (19)

Fターム[5F083EP65]に分類される特許

1 - 19 / 19

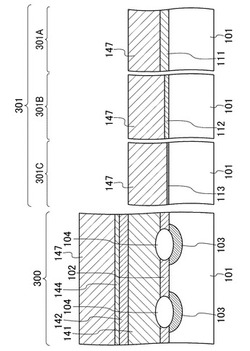

半導体記憶装置の製造方法

【課題】記憶部と論理部とを有する半導体記憶装置において、電気的特性のばらつき及び信頼性の低下を回避できるようにする。

【解決手段】半導体記憶装置の製造方法は、記憶部300及び論理部301を有する基板101の上に、記憶部ゲート絶縁膜102及び第1の導電膜141を形成する工程よりも後に、第1の導電膜141及び記憶部ゲート絶縁膜102における論理部301の上に形成された部分を除去する。論理部ゲート絶縁膜111及び第2の導電膜147を形成する工程よりも後に記憶部300において第1の導電膜141を露出する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】ビット線に拡散層を用いる半導体記憶装置のチャネル領域に発生する2次電子を抑制して信頼性を向上できるようにする。

【解決手段】半導体記憶装置100は、P型の半導体基板101の上部にそれぞれが互いに並行に延びるように形成された複数のビット線拡散層108と、半導体基板101の上で、且つそれぞれが各ビット線拡散層108と交差する方向に互いに並行に延びるように形成された複数のワード線電極110とを有している。さらに、半導体基板101における各ワード線電極110の下方の領域には、周囲よりも濃度が低いP型の複数の第3の不純物層111Aがそれぞれ自己整合的に形成されている。

(もっと読む)

半導体装置の製造方法

【課題】FEOLにおいても半導体装置のチャージングを効果的に抑制できるようにする。

【解決手段】半導体装置の製造方法は、半導体基板101の上に、被保護素子のゲート絶縁膜となる第1の絶縁膜122を形成する工程(a)と、保護素子部302において第1の絶縁膜122の少なくとも一部を除去する工程(b)と、工程(b)よりも後に、被保護素子部301において第1の絶縁膜122の表面を窒化する工程(c)と、工程(c)よりも後に、被保護素子部301及び保護素子部302の上に跨るように導電膜を選択的に形成することにより、互いに接続された被保護素子のゲート電極141及び保護素子の電極142を形成する工程(d)とを備えている。

(もっと読む)

半導体装置

【課題】第1導電型の半導体層とトンネルウィンドウが対向する第2導電型の不純物拡散領域との高い接合耐圧を得ることができる、半導体装置を提供する。

【解決手段】各メモリセルにおいて、半導体基板2の表層部には、N型の第1不純物拡散領域3が形成されている。また、半導体基板2の表層部には、第1不純物拡散領域3に対して所定方向の一方側に、第1不純物拡散領域3と間隔を空けて、N型の第2不純物拡散領域4が形成されている。半導体基板2上には、第1絶縁膜6が形成されている。第1絶縁膜6には、第1厚膜部8が形成されており、第2不純物拡散領域4の全周縁は、第1厚膜部8の直下に位置している。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】MONOS型半導体記憶装置の電荷蓄積用のトラップ膜及びビット線拡散層を有する不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板101に形成され、それぞれ行方向に延伸する複数のビット線拡散層104と、半導体基板101上における互いに隣接する各ビット線拡散層104同士の間に形成され、それぞれが電荷トラップ膜102bを含む複数のONO膜102と、複数のビット線拡散層104の上にそれぞれ形成された複数のビット線絶縁膜105と、半導体基板101の上にそれぞれ複数のONO膜102及び複数のビット線絶縁膜105を覆うように形成され、各ビット線拡散層104と交差して列方向に延伸する複数のワード線106とを有している。ビット線絶縁膜105の膜厚はONO膜102の膜厚よりも小さく、且つビット線絶縁膜105の上面はONO膜102の上面と平行である。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、半導体装置の製造方法等に関し、特にプラズマダメージを受けたゲート絶縁膜のダメージ層を除去し、ゲート絶縁膜の信頼性を向上させることのできる半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、MONOS型メモリトランジスタ領域101及びトランジスタ領域100を同一の半導体基板に有する場合、MONOS型メモリトランジスタ領域の半導体基板上にトンネル酸化膜7を形成し、そのトンネル酸化膜7上及びトランジスタ領域のゲート絶縁膜5上に窒化シリコン膜8を形成し、その上に酸化シリコン膜9を形成する。MONOS型メモリトランジスタ領域にマスク膜10を形成し、マスク膜10を用いて酸化シリコン膜9を除去し、窒化シリコン膜8をドライエッチングにて除去し、トランジスタ領域100のゲート絶縁膜5の上層部分をウェットエッチングにより除去することを特徴とする。

(もっと読む)

半導体装置の製造方法および半導体ウエハ洗浄装置

【課題】カロー酸を用いたウエハ(基板)洗浄工程において、H2O2の使用量を低減しつつ、フォトレジスト膜(感光性マスキング層)の除去性を向上できる技術を提供する。

【解決手段】基板1の洗浄(フォトレジスト膜の除去)時以外のSPM液中のH2O2の濃度は、フォトレジスト膜の少なくとも一部を除去できる最低限の第1濃度以上で制御する。そして、基板1をSPM槽51(内槽51A)へ浸漬する直前に、SPM液中のH2O2の濃度がフォトレジスト膜を確実に除去できる第2濃度以上となり、また基板1をSPM槽51(内槽51A)へ浸漬した時にSPM液中のH2O2の濃度がその第2濃度未満とならないように、過酸化水素水供給系54からSPM槽51(内槽51A)へ所定量のH2O2を供給する。

(もっと読む)

半導体記憶装置

【課題】 埋め込みビット線構造の半導体記憶装置において、当該ビット線構造に起因する諸々の問題を解決し、確実なシリサイド形成を行なうことを可能とし、低抵抗で更なる微細化・高速動作化を実現する。

【解決手段】 ビット線11と不純物拡散層14は、各々の一端が重畳されて接続されており、周辺回路領域3における選択トランジスタのソース/ドレイン17の表層及び重畳部位14aを含む不純物拡散層14の表層に高融点金属、ここではTiとSiとのシリサイド化が施され、チタンシリサイド層18が形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】トラップ膜を有するメモリセルのデータ保持特性の劣化を防止し、信頼性が高いMONOS型不揮発性半導体装置及びその製造方法を提供する。

【解決手段】p型の半導体基板101の上に、電荷を蓄積するONO膜102を有し、ONO膜102の上に多結晶シリコンからなる複数のワードライン103を有し、ワードライン103の表面、ワードライン103の側面、およびONO膜102の表面上に、有機原料を用いた減圧CVD法による、膜厚が約30nm、水素結合量が約5×1022個/cm3、水素含有量が約5×1022atoms/cm3、炭素含有量が約5×1021atoms/cm3のシリコン窒化膜104を有する。これにより、トラップ膜へのチャージングを無くすと共に、ゲート電極間の酸化絶縁膜中の固定電荷を制御することで、メモリセルのデータ保持特性の劣化を防止することができる。

(もっと読む)

半導体記憶装置

【課題】より低電圧での消去動作を可能にすること。

【解決手段】基板上の第1の領域に配設されたセレクトゲート3と、前記第1の領域に隣接する第2の領域に配設されたフローティングゲート6と、前記第2の領域と隣接する第3の領域に設けられた第1の拡散領域7と、フローティングゲート6の上に配設されたコントロールゲート11と、基板1(ウェル1a)、セレクトゲート3、第1の拡散領域7、およびコントロールゲート11に印加される電圧を制御する駆動回路22と、を備え、駆動回路22は、消去動作の際、セレクトゲート3およびコントロールゲート11の電圧を負電圧とし、残り1つ基板1(ウェル1a)の電圧を正電圧とするように制御する。

(もっと読む)

半導体記憶装置

【課題】メモリセルが微細化されても十分な動作マージンを確保できるようにすること。

【解決手段】基板1、セレクトゲートSG0、SG1、ローカルビット線LB2、及びコントロールゲートCGnに印加される電圧を制御する駆動回路22を備える。駆動回路22は、書き換え動作の際、コントロールゲートCGnに対して負電圧、セレクトゲートSG0に正電圧、セレクトゲートSG1にセレクトゲートSG0の電圧よりも低い電圧、ローカルビット線LB2に正電圧をそれぞれ印加することによって、FNトンネリングによりフローティングゲートFG3からローカルビット線LB2に電子を選択的に引き抜く制御を行なう。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】電荷保持膜端部の構造安定性を向上してメモリ特性劣化を軽減し更なる微細化を可能とするとともに、電荷保持膜への工程中チャージングの蓄積を抑制する。

【解決手段】半導体基板100中に形成されたソースまたはドレインとして機能する一対の拡散層と、一対の拡散層間における半導体基板上に形成された電荷捕獲機能を有するゲート絶縁膜104と、ゲート絶縁膜上に形成されたゲート電極とで構成されたメモリセルからなる不揮発性半導体記憶装置である。メモリセルのゲート絶縁膜は端部まで全体が平坦に形成されており、隣接するメモリセルの各ゲート絶縁膜の端面の下端まで接するように、隣接するメモリセル間にビット線絶縁膜111が形成されている。このビット線絶縁膜は、各ゲート絶縁膜に接する端部が厚く、中央部が薄く形成されている。

(もっと読む)

半導体記憶装置

【課題】電極間絶縁膜の容量の低下を抑制し、低消費電力かつ高速動作が可能な半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板1と、この半導体基板1上に形成された第1の絶縁膜2と、この第1の絶縁膜2上に形成され、導電性金属酸化物で形成された浮遊ゲート電極FGと、この浮遊ゲート電極FG上に形成され、7.8以上の比誘電率を有し、常誘電体の絶縁性金属酸化物で形成された第2の絶縁膜INと、この第2の絶縁膜IN上に形成され、金属又は導電性金属酸化物で形成された制御ゲート電極CGとを具備する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】製造工程の際に発生する電磁波が、不揮発性半導体記憶装置の奥深くまで侵入することを確実に防止する。

【解決手段】半導体基板100中に形成され、ビット線として機能する拡散層103と、半導体基板100上に形成され、ゲート絶縁膜として機能する電荷を蓄積することにより情報を記憶するトラップ膜101と、トラップ膜101上に形成されたゲート電極105とからなる複数のメモリセルが、拡散層103上の絶縁膜104によって互いに分離されアレイ状に配置された不揮発性半導体記憶装置において、互いに隣り合う複数のゲート電極105の各々の側面には、遮光性を有する絶縁膜207aが形成されている。

(もっと読む)

不揮発性半導体記憶装置

【課題】

高速かつ安定な読み出しを可能にすること。

【解決手段】

基板1上の第1の領域に絶縁膜2を介して配設されたセレクトゲート3と、第1の領域に隣接する第2の領域に絶縁膜5を介して配設されたフローティングゲート6aと、第2の領域と隣接するとともに基板表面上の第3の領域に設けられた拡散領域7aと、フローティングゲート6aの上に絶縁膜8を介して配設されたコントロールゲート11と、で一つの単位セルを構成し、対応する第1の単位セルと第2の単位セルを用いて1ビットのデータを記憶するように構成されたことを特徴とする。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】 不揮発性半導体記憶素子がマトリックス状に配置されている仮想グラウンドアレイの半導体集積回路装置において、ビット線間およびワード線間のリーク電流を効率よく抑制する。

【解決手段】 ビット線BL1〜4である拡散層とワード線WL1〜3であるゲート電極に囲まれた領域にある半導体基板の表面上に、不揮発性半導体記憶素子とは分離された状態で、シリコン酸化膜を介してシリコン窒化膜(電荷トラップ層)を形成し、さらに基板全体をプラズマ雰囲気に晒すことで、このシリコン窒化膜に電子を意図的にトラップさせる。その結果、この領域の半導体基板表面には正電荷が蓄積状態となり、ビット線間およびワード線間のリーク電流を抑制することができる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】コンタクトレス方式が採用されたメモリセルアレイにおける共用コンタクト領域においてリーク電流を抑制する。

【解決手段】不揮発性半導体記憶装置は、複数の埋め込み拡散ビット線2と、埋め込み酸化膜と、複数のワード線5と、ワード線5とビット線2間領域との交差領域に形成された電荷保持膜からなる複数のメモリセルと、コンタクト7を上面に有する複数の拡散層8があり、複数のブロックに区分されたビット線2同士は拡散層8を介して電気的に接続されており、コンタクト領域となる拡散層8の近傍領域に形成されたビット線2間に形成された素子分離領域9とを備える。さらに、ビット線2上及び素子分離領域9上に跨り、側壁絶縁膜を有するダミーワード線14を備え、側壁絶縁膜は、素子分離領域9と、埋め込み酸化膜と、ビット線2との境界領域上を覆う。

(もっと読む)

半導体装置およびその製造方法

【課題】 埋め込みビット線構造を備えたMONOS型不揮発性半導体のONO膜等の電荷蓄積膜のエッジ付近にかかる電界集中を抑制して電荷蓄積膜の信頼性を確保する。

【解決手段】 半導体基板1中に形成された埋め込みビット線と、埋め込みビット線に対して交差方向の半導体基板1上に形成されたワード線と、埋め込みビット線上に形成されたビット線酸化膜8と、埋め込みビット線8の領域が開口するように半導体基板表面に形成された電荷蓄積保持するONO膜とを有し、半導体基板表面よりも下側に位置するビット線酸化膜8の膜厚に対する半導体基板表面よりも上側に位置するビット線酸化膜8の膜厚の比が1より小さくしてある。これにより、ONO膜はビット線酸化膜8のエッジ付近においても実質的に平坦となるように構成されるため、ONO膜にかかる電界集中が緩和され、ONO膜のTDDB特性が改善される。

(もっと読む)

半導体装置およびその製造方法

【課題】 ゲート絶縁膜としてONO膜積層構造を有した半導体装置において、メモリトランジスタの耐圧劣化を防止する。

【解決手段】 半導体基板1上に下方より順に形成された下部酸化シリコン膜、窒化シリコン膜、上部酸化シリコン膜(ONO膜2)からなるゲート絶縁膜と、ゲート絶縁膜に隣接して半導体基板中に形成された不純物拡散層4と、不純物拡散層4上に形成され、ゲート絶縁膜に隣接する絶縁膜8とを備え、ゲート絶縁膜とこれに隣接する絶縁膜8との境界領域において、窒化シリコン膜の端部が上部酸化シリコン膜の端部よりも後退して形成されている。これにより、ONO膜に部分的に絶縁膜の膜厚が薄い場所が生じないようにすることができ、その結果、メモリトランジスタの耐圧劣化が起こらないようにすることが可能となる。

(もっと読む)

1 - 19 / 19

[ Back to top ]