Fターム[5F083FR02]の内容

半導体メモリ (164,393) | 強誘電体メモリ (1,733) | キャパシタを有するもの(破壊読出型) (1,245) | 1Tr/1C型 (791)

Fターム[5F083FR02]に分類される特許

781 - 791 / 791

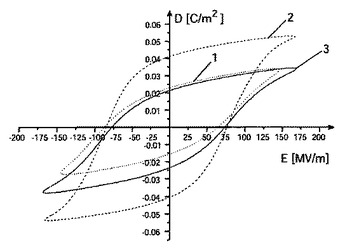

強誘電性ポリマー層のパターニング方法

感光性架橋剤を含んでなる強誘電性スピンコーティング溶液から基材上に強誘電性ポリマーの層をスピンコーティングした後、強誘電性ポリマー層をマスクを通して照射し、強誘電性ポリマー層の非露光部分を除去することにより、例えば二フッ化ビニリデン(VDF)およびトリフルオロエチレン(TrFE)のコポリマーのような強誘電性ポリマーがパターニングされることができる。  (もっと読む)

(もっと読む)

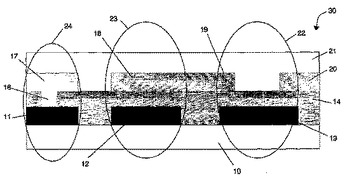

不揮発性強誘電体メモリ装置の製造方法及びその方法によって得られるメモリ装置

本発明は、トランジスタ22及びキャパシタ23を含んでいる不揮発性強誘電体メモリ装置30に関し、特に、不揮発性で、電気的に消去可能、かつプログラム可能な強誘電体メモリ素子及びそのような不揮発性強誘電体メモリ装置30を生産する方法に関する。本発明による方法は、トランジスタ22のゲート誘電体層及びキャパシタ23の誘電体層は同一の有機又は無機強誘電体層から作られるので、限られた数のマスクステップを含む。  (もっと読む)

(もっと読む)

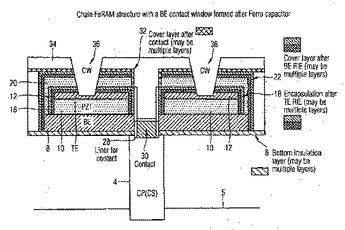

強誘電体キャパシタデバイスおよびFeRAMデバイス

1つ以上のコンタクトプラグが通過して延びている基板と、上記基板上に形成された第1の層間絶縁膜とから、強誘電体キャパシタデバイス(例えばFeRAMデバイス)が形成されている。上記第1の層間絶縁膜上にはスペーサ層が形成されていて、このスペーサ層上には第1の酸素バリア層が形成されていて、この第1の酸素バリア層上にはバッファ層が形成されている。上記バッファ層上において、上記バッファ層と上記コンタクトプラグとの間に下地材料の層が形成されていて、第1の電極と第2の電極との間に誘電体層が挟まれている。上記デバイスに第2の酸素バリア層が塗布される。上記スペーサ層があれば、上記下地材料と上記コンタクトプラグとの界面まで酸化が及ぶことが抑制される。なぜなら、上記界面が、上記第1の酸素バリア層の下に位置しているからである。この結果、電気コンタクトが破損することはない。  (もっと読む)

(もっと読む)

強誘電体コンデンサ装置におけるコンタクトプラグの酸化防止装置およびその方法

本発明は、強誘電体コンデンサ装置およびその製造方法にかかる。この製造方法は、基板を形成する工程と、この基板を貫通するようにコンタクトプラグを形成する工程とを含む。基板の上には電気絶縁層が形成され、この電気絶縁層上に第1の電極が形成される。さらに、第1の電極上には強誘電体層が形成され、強誘電体層上には第2の電極が形成される。第1の電極は、電気絶縁層を貫通して、プラグに電気接続されている。  (もっと読む)

(もっと読む)

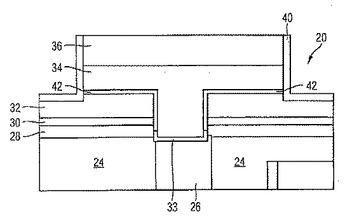

強誘電体キャパシタおよびFeRAMデバイスの形成方法

導電性材料を堆積し、そしてこの導電性材料をエッチングして電極を形成することによって、FeRAMデバイスの縦型キャパシタが形成される。上記電極は、絶縁層内にある開口部の上に配置されるため、上記構造の低い位置に電気的に接続される。上記電極の側面に強誘電体材料の層が形成され、そして所望の均一な厚みになるまでエッチングされる。上記強誘電体材料の上に導電性材料が堆積されて、別の絶縁層を堆積できる均一な表面が形成される。上記プロセスは、上記電極の形成と上記強誘電体材料の堆積との間に絶縁層をエッチングする工程を含んでいないため、これらの間に絶縁材料のフェンスが形成されることがない。形状を正確に制御して、均一な電界と信頼性のある動作パラメータを得ることができる。  (もっと読む)

(もっと読む)

三次元集積回路構造及びこれを作る方法

垂直方向の半導体装置は、電気装置そして/または相互接続を含む分離して作られた基板に付加される。多くの垂直方向の半導体装置は物理的に互いに分離され、そして同一半導体本体又は半導体基板内には配置されない。多くの垂直方向の半導体装置は取り付けられた後に個別のドープされたスタック構造を生成するため、エッチングされた数個のドーピングされた半導体領域を含む薄い層として分離して作られた基板へ付加される。あるいは多くの垂直方向の半導体装置が分離して作られた基板に取り付けるのに先立ち製作される。ドープされたスタック構造は、ダイオードキャパシタ、n‐MOSFET、p‐MOSFET、バイポーラトランジスタ、及び浮遊ゲートトランジスタのベースを形成する。強誘電体メモリー装置、強磁性体メモリー装置、カルコゲニド位相変更装置が分離して作られた基板と連結して使用するために、堆積可能なアッド‐オン層に形成される。堆積可能なアッド‐オン層は相互接続ラインを含む。

(もっと読む)

(もっと読む)

強誘電体膜およびその製造方法ならびに半導体装置

【課題】 低温の結晶化により良好な特性を有するBi層状ペロブスカイト構造を有する強誘電体膜の製造方法を提供する。

【解決手段】 本発明の強誘電体膜の製造方法は、第1の原料液と、第2の原料液とを含む強誘電体の原料液を結晶化することにより、強誘電体膜を形成する工程を含み、前記第1の原料液と前記第2の原料液とは、種類が異なる関係にあり、前記第1の原料液は、Bi系層状ペロブスカイト構造を有する強誘電体を生成するための原料液であり、前記第2の原料液は、AサイトがPbであるABO3系酸化物を生成するための原料液である。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁膜の埋め込み性が高く高集積化に適切に対応することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板の上方に強誘電体キャパシタを形成した後、強誘電体キャパシタを覆うAl2O3膜を形成する。その後、Al2O3膜を覆う高密度プラズマ絶縁膜を、O2ガス及びSiH4ガスを用いて形成する。このとき、O2ガスの流量をSiH4ガスの流量の6乃至9倍とすると共に、半導体基板の温度を280℃乃至320℃とする。

(もっと読む)

強誘電体膜を有する半導体装置の製造方法

【課題】強誘電体膜をエッチングする際に生じる反応副生成物を形成される素子に悪影響を与えることなく除去する。

【解決手段】強誘電体膜をエッチングしたあと、燐酸水溶液を用いてウェット処理をする。レジストをマスクとして強誘電体膜をエッチングしたあと、レジストアッシング後またはアッシング前後の両方に燐酸水溶液を用いてウェット処理をする。

(もっと読む)

半導体装置およびその製造方法

【課題】 強誘電体キャパシタに保護膜を設け、強誘電体膜の還元を抑制する。

【解決手段】 前記保護膜としてAl2 O3 膜を、3.0〜3.1g/cm3 、あるいはそれ以上の密度に形成する。

(もっと読む)

半導体装置の製造方法、強誘電体キャパシタ、およびその製造方法

【課題】 強誘電体キャパシタを有する半導体装置の製造において、強誘電体膜の自発分極を最大化する。

【解決手段】 下側電極を形成後、強誘電体膜を堆積する前に、前記下側電極を不活性雰囲気中において急速熱処理する。

(もっと読む)

781 - 791 / 791

[ Back to top ]