Fターム[5F083FR03]の内容

半導体メモリ (164,393) | 強誘電体メモリ (1,733) | キャパシタを有するもの(破壊読出型) (1,245) | 2Tr/2C型 (102)

Fターム[5F083FR03]に分類される特許

1 - 20 / 102

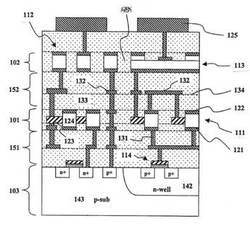

半導体構造

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、半導体構造を提供することを目的とする。

【解決手段】下部誘電層(151)へ接合された基板(103)、および、下部電極(121)を通じて前記下部誘電層(151)と接合される垂直方向半導体装置(111)を含む半導体構造であって、前記垂直方向半導体装置(111)は、n+−p−n+層(124)を有する隔離構造(135)を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】セキュリティを高めるための半導体装置を提供する。

【解決手段】第1トランジスタ4a、および第1トランジスタ4aに接続される第1キャパシタ4bを有する第1メモリセル4を含む第1メモリセルアレイ2と、第1トランジスタ4aよりもオフ電流が高い第2トランジスタ5a、および第2トランジスタ5aに接続される第2キャパシタ5bを有する第2メモリセル5を含む第2メモリセルアレイ3と、を有する。

(もっと読む)

半導体装置の製造方法、強誘電体素子の製造方法および電子機器の製造方法

【課題】液体プロセスに採用し易い配向性の制御が可能な半導体装置や強誘電体素子の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、ソース電極およびドレイン電極と、前記ソース電極及び前記ドレイン電極との間に配置され、チャネル部を有する有機半導体膜と、ゲート電極と、前記チャネル部と前記ゲート電極との間に配置されたゲート絶縁膜と、を有する半導体装置の製造方法であって、前記チャネル部を第1の温度に加熱する工程と、前記第1の温度の前記有機半導体膜に、前記第1の温度よりも低い第2の温度の絶縁性ポリマーを含む液滴材料を配置し一定の方向に延ばす塗工工程により前記ゲート絶縁膜を形成する工程と、を有することを特徴とする。

(もっと読む)

半導体装置

【課題】実動作キャパシタとダミーキャパシタとが形成された半導体装置において、水素・水分、不均一なストレスによる実動作キャパシタの性能劣化を抑制し、FeRAMの寿命特性を向上する。

【解決手段】半導体基板10上の実動作キャパシタ部26の下部電極30と強誘電体膜32と上部電極34を有する複数の実動作キャパシタ36aと、半導体基板10上の実動作キャパシタ部26の外側のダミーキャパシタ部28の下部電極30と強誘電体膜32と上部電極34を有する複数のダミーキャパシタ36bと、複数の実動作キャパシタ36a上の複数の配線40と、複数のダミーキャパシタ36b上の配線40を有し、ダミーキャパシタ36bのピッチの実動作キャパシタ36aのピッチに対する比は、0.9〜1.1の範囲にあり、ダミーキャパシタ36b上の配線40のピッチの実動作キャパシタ36a上の配線40のピッチに対する比は、0.9〜1.1の範囲にある。

(もっと読む)

アッド‐オン層形成方法

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、堆積可能なアッド‐オン層形成方法を提供することを目的とする。

【解決手段】堆積可能なアッド‐オン層形成方法であって、第一半導体基板の取り外し層の形成、取り外し層の上の第一半導体基板に多くのドーピング領域の形成、ここで多くのドーピング層の形成は、第一電導型を有するように、ドーピングされ、取り外し層の上の第一半導体基板の第一ドーピング層の形成、第一電導型に対する第二電導型を有するようにドーピングされ、第一ドーピング層の上の第一半導体基板に最低中間ドーピング層の形成、及び中間ドーピング層上の第一半導体基板に最低第三ドーピング層の形成からなり、第三ドーピング層上に第一の電導性ブランケット層の形成、第一電導ブランケット層上に第二の電導性ブランケット層の形成、及び第二電導性ブランケット層が第二半導体基板の対応する電導性上部層と接触するように、第一半導体基板を第二半導体基板への取り付け、からなる。

(もっと読む)

半導体記憶装置

【課題】強誘電体膜の膜質を均一化するチェインFeRAM型半導体記憶装置を提供する。

【解決手段】半導体記憶装置80は、同一素子形成領域に隣接配置される、一対のソース/ドレイン層5を有するメモリトランジスタTR1及びTR2と、メモリトランジスタのソース/ドレイン層5の他方とメモリトランジスタTR2のソース/ドレイン層5の一方に、ビア及びバリアメタル膜13を介して接続される強誘電体キャパシタCAP1及びCAP2とを有する。強誘電体キャパシタCAP1及びCAP2は、バリアメタル膜13上に設けられ、四角錐台形状の下部電極14と、下部電極14を覆うように設けられる強誘電体膜15とを共有し、強誘電体キャパシタCAP1は、強誘電体膜15上に設けられる第1の上部電極16aを有し、強誘電体キャパシタCAP2は、強誘電体膜15上に設けられ、第1の上部電極16aと離間して配置される第2の上部電極16bを有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】1容量素子当たりの面積を、微細加工に問題を起こすことなく縮小できるようにする容量素子を有するメモリーのような半導体装置を提供する。

【解決手段】酸素バリア膜16、層間絶縁膜17(酸化シリコン膜)上に、薄いエッチングストッパー膜18(窒化シリコン膜)、層間絶縁膜19(酸化シリコン膜)を形成し、酸素バリア膜16の直上にそれより大きい開口部をドライエッチングにより形成する。その後、強誘電体材料を容量絶縁膜とする容量素子の下部電極21を開口部20上を含むように形成する。開口部20を形成するための層間絶縁膜19のエッチングはエッチングストッパー膜18で容易に停止できるので、下地層間絶縁膜17がエッチングされない。こうして酸素バリア膜16を縮小し、容量素子占有面積を小さくできる。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】強誘電体キャパシタを高信頼性化する。

【解決手段】半導体記憶装置70に設けられる強誘電体キャパシタ50は、積層形成される下部電極膜14、強誘電体膜15、及び上部電極膜16から構成される。下部電極膜14は、メモリセルトランジスタ40のソース及びドレインの一方の上部に設けられるコンタクトプラグ11と電気的に接続される部分が下に凸となりコンタクトプラグ上部に埋め込まれる形状を有し、反応防止膜13を介してコンタクトプラグ11に接続される。上部電極膜16は、コンタクトプラグ23を介して配線層25に接続される。コンタクトプラグ11及び反応防止膜13が接続される界面の両端部とコンタクトプラグ11の上側面とは反応防止膜9で覆われる。強誘電体キャパシタ50は、コンタクトプラグ11及び23を除く領域が反応防止膜9と反応防止膜9と接する反応防止膜19により覆われる。

(もっと読む)

半導体装置及びその製造方法

【課題】高いスイッチング電荷量を得ながら、リーク電流の変動を抑制することができる半導体装置及びその製造方法を提供する。

【解決手段】下地膜51上に、Irからなる下部電極52、PZT膜の初期層53、コア層54及び終端層55、並びにIrO2からなる上部電極56を形成する。初期層53は、低酸素分圧にて5nmの厚さで形成する。コア層54の厚さは120nmとする。終端層55は、過剰Zr層とする。即ち、終端層55の組成について、「Zr/(Zr+Ti)」は0.5よりも大きく、終端層55には、平衡組成よりもZrが過剰に含有される。

(もっと読む)

三次元的スタックド不揮発性メモリユニット

メモリユニット(200)であって、メモリユニットの第1の層において第1のトランジスタ領域に広がる第1のトランジスタ(210)と、メモリユニットの第2の層において第2のトランジスタ領域に広がる第2のトランジスタ(220)と、メモリユニットの第3の層において第1のメモリ領域に広がる第1の抵抗センスメモリ(RSM)セル(230)と、メモリユニットの第3の層において、第2のメモリ領域に広がる第2のRSMセル(250)とを含む。第1のトランジスタは第1のRSMセルに電気的に結合され、第2のトランジスタは第2のRSMセルに電気的に結合される。第2の層は第1の層と第3の層との間にある。第1のトランジスタおよび第2のトランジスタは、トランジスタ重畳領域を有する。第1のメモリ領域および第2のメモリ領域は、第1のトランジスタ領域および第2のトランジスタ領域を越えて延在しない。  (もっと読む)

(もっと読む)

前駆体組成物および圧電素子の製造方法

【課題】絶縁性に優れた複合酸化物積層体およびその製造方法を提供する。

【解決手段】基板20と、前記基板20の上方に形成され、一般式ABO3で表される第1複合酸化物層24と、前記第1複合酸化物層24の上方に形成され、一般式AB1-xCxO3で表される第2複合酸化物層26と、を含み、A元素は、少なくともPbからなり、B元素は、Zr、Ti、V、WおよびHfの少なくとも一つからなり、C元素は、NbおよびTaの少なくとも一つからなる。

(もっと読む)

キャパシタ、強誘電体メモリ装置、アクチュエータおよび液体噴射ヘッド

【課題】結晶性の良好な誘電体膜を有し、良好なヒステリシス特性を有することができるキャパシタを提供する。

【解決手段】本発明に係るキャパシタ100は,下部電極4と、下部電極4の上方に形成され、ニオブ酸チタン酸ジルコン酸鉛からなる第1誘電体膜11と、第1誘電体膜11の上方に形成され、チタン酸ジルコン酸鉛、または、前記第1誘電体膜を構成するニオブ酸チタン酸ジルコン酸鉛よりもNb組成が小さいニオブ酸チタン酸ジルコン酸鉛からなる第2誘電体膜13と、第2誘電体膜13の上方に形成された上部電極6と,を含む。

(もっと読む)

半導体記憶装置

【課題】温度の変化に対し常に信号量の変化を最大化した形での読み出し動作を可能とした半導体記憶装置を提供することができる。

【解決手段】ビット線電圧制御回路3は、読み出し時に選択ビット線に結合されてその電位を引き下げるためのカップリング用キャパシタC1、C2と、その一端N1、N2を選択的にビット線対/BL、BLに接続するためのNMOSトランジスタQ11、Q21を有する。キャパシタC1、C2の他端は電圧発生回路4に接続され、制御信号線V1、V2から所定の電圧を与えられる。この制御信号線V1、V2の電圧は、所定の温度特性を与えられている。

(もっと読む)

半導体記憶装置、及びその製造方法

【課題】メモリ特性のバラツキを抑制した半導体記憶装置、及びその製造方法を提供する。

【解決手段】半導体記憶装置100は、強誘電体キャパシタCとセルトランジスタTrを並列に接続したメモリセルMCを有するメモリセルアレイ1aを備える。メモリセルアレイ1aは、基板10の上層に設けられた第1導電層31と、第1導電層31の上面に形成された強誘電体層32と、強誘電体層32の上面に形成された第2導電層34と、強誘電体層32と同層に形成されたストッパー層33とを備える。化学機械研磨によるストッパー層33の選択比は、化学機械研磨による強誘電体層32の選択比よりも大きい。

(もっと読む)

強誘電体メモリの製造方法および試験システム

【課題】 ツインセンスアンプを有する強誘電体メモリの製造工程において、インプリント特性を考慮した試験を実施し、インプリントによる不良が市場で発生することを防止する。

【解決手段】 単一の論理レベルを記憶する強誘電体キャパシタを有する第1メモリセルと、相補の論理レベルを記憶する強誘電体キャパシタ対を有する第2メモリセルと、第1および第2メモリセルに接続されたツインセンスアンプとを有する強誘電体メモリが製造される。まず、第1および第2メモリセルに第1論理が書き込まれ、インプリントを進めるために、強誘電体メモリが高温下で放置される。次に、第1メモリセルに第1論理と逆の第2論理が書き込まれる。そして、第1メモリセルに保持されている論理が読み出され、読み出される論理が第2論理と異なるとき、強誘電体メモリの不良が検出される。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】簡便な方法により、マスク側壁への反応生成物の堆積を防止することができる半導体装置を製造する方法を提供する。

【解決手段】下部電極21、強誘電体、常誘電体、反強誘電体等による誘電体層22、及び上部電極23を含むキャパシタを複数備える半導体装置の製造方法は、上部電極層をパターニングして、複数の上部電極23、23’、23”を形成する工程と、複数の上部電極23、23”を被覆し、かつ最端に配置された上部電極23’の少なくとも一方側の端部を露出する第1マスクパターンを形成する工程と、第1マスクパターンを用いて、誘電体層22をパターニングする工程とを有する。

(もっと読む)

有機複合電子素子及びその製造方法、及び該有機複合電子素子を用いる有機半導体メモリ

【課題】有機薄膜トランジスタと、高誘電体キャパシタとを備える有機複合電子素子の製造を容易化する。

【解決手段】トランジスタTr及びキャパシタCaを備える有機複合電子素子の製造方法である。基板11上にゲート電極Ga及びキャパシタ用対向電極の一方CE1を形成し、その上に高誘電体膜17b、低誘電体膜17a及び有機半導体膜16を形成し、低誘電体膜17a及び有機半導体膜16のキャパシタ用対向電極CE1に対応する部分を除去し、その上に、高誘電体膜17b、低誘電体膜17a及び有機半導体膜16を挟んでゲート電極Gaと所定の位置関係でソース電極So及びドレイン電極Drを、高誘電体膜17bを挟んで対応するようにキャパシタ用対向電極の他方CE2を形成する。

(もっと読む)

半導体記憶装置

【課題】微細化しても信号量の差を低下させず、データの誤検出を抑制することができる半導体記憶装置を提供する。

【解決手段】強誘電体メモリは、互いに並列に接続された強誘電体キャパシタおよびセルトランジスタを含むメモリセルが複数個直列に接続されて構成されたセルブロックと、セルトランジスタのゲートに接続されたワード線と、セルブロックの一端に接続されたブロック選択部と、ブロック選択部を介してセルブロックの一端に接続された複数のビット線と、セルブロックの他端に接続されたプレート線とを備え、ワード線を共有する第1および第2のセルブロックの各一端は、互いに異なるブロック選択部を介して、同一のビット線に接続されており、第1および前記第2のセルブロックの各他端は、互いに異なるプレート線に接続されている。

(もっと読む)

複合酸化物積層体、複合酸化物積層体の製造方法、デバイス

【課題】絶縁性に優れた複合酸化物積層体およびその製造方法を提供する。

【解決手段】基板20と、前記基板20の上方に形成され、一般式ABO3で表される第1複合酸化物層24と、前記第1複合酸化物層24の上方に形成され、一般式AB1-xCxO3で表される第2複合酸化物層26と、を含み、A元素は、少なくともPbからなり、B元素は、Zr、Ti、V、WおよびHfの少なくとも一つからなり、C元素は、NbおよびTaの少なくとも一つからなる。

(もっと読む)

半導体装置の製造方法、強誘電体素子の製造方法および電子機器の製造方法

【課題】液体プロセスに採用し易い配向性の制御が可能な半導体装置や強誘電体素子の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、基板と、前記基板の上方に配置されたソース電極およびドレイン電極と、前記ソース電極およびドレイン電極間に配置されチャネル部を構成する有機半導体膜と、前記チャネル部との間にゲート絶縁膜を介して配置されたゲート電極とを有する半導体装置の製造方法であって、前記基板(2)の上方に絶縁性ポリマーを材料に含む液体材料(6a)を塗布する第1工程と、塗布された前記液体材料に対して送風を行いつつ加熱することにより前記ゲート絶縁膜を形成する第2工程と、を有する。かかる方法によれば、溶液プロセスにおいて簡易な方法で、ゲート絶縁膜の配向性を向上させることができる。

(もっと読む)

1 - 20 / 102

[ Back to top ]