Fターム[5F083FR07]の内容

半導体メモリ (164,393) | 強誘電体メモリ (1,733) | MFS型(非破壊読出型) (230) | MFMIS型 (41)

Fターム[5F083FR07]に分類される特許

1 - 20 / 41

マンガン酸化物、マンガン酸化物を備える強誘電体メモリ素子、および強誘電体メモリ装置

【課題】主成分として有害物質鉛元素を含まずに、強誘電性を示しかつ外部磁場によって分極の大きさを制御可能な新規なマンガン酸化物、およびそのメモリへの利用を提供する。

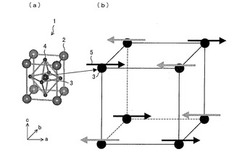

【解決手段】マンガン酸化物は、ペロブスカイト構造を有する、式(1)Sr1−xBaxMnO3(1≧x>0.4)・・・(1)で表されるマンガン酸化物である。単位格子1の対称中心には磁性イオンであるMnイオン3が存在する。単位格子1の対称中心をMnサイトとする。単位格子1が有する8個の頂点には、SrイオンおよびBaイオンのうちいずれか一方が存在している。単位格子1が有する頂点をSrサイト2とする。単位格子1が有する6面の面心には、Oイオン4が存在する。

(もっと読む)

半導体構造

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、半導体構造を提供することを目的とする。

【解決手段】下部誘電層(151)へ接合された基板(103)、および、下部電極(121)を通じて前記下部誘電層(151)と接合される垂直方向半導体装置(111)を含む半導体構造であって、前記垂直方向半導体装置(111)は、n+−p−n+層(124)を有する隔離構造(135)を含む。

(もっと読む)

アッド‐オン層形成方法

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、堆積可能なアッド‐オン層形成方法を提供することを目的とする。

【解決手段】堆積可能なアッド‐オン層形成方法であって、第一半導体基板の取り外し層の形成、取り外し層の上の第一半導体基板に多くのドーピング領域の形成、ここで多くのドーピング層の形成は、第一電導型を有するように、ドーピングされ、取り外し層の上の第一半導体基板の第一ドーピング層の形成、第一電導型に対する第二電導型を有するようにドーピングされ、第一ドーピング層の上の第一半導体基板に最低中間ドーピング層の形成、及び中間ドーピング層上の第一半導体基板に最低第三ドーピング層の形成からなり、第三ドーピング層上に第一の電導性ブランケット層の形成、第一電導ブランケット層上に第二の電導性ブランケット層の形成、及び第二電導性ブランケット層が第二半導体基板の対応する電導性上部層と接触するように、第一半導体基板を第二半導体基板への取り付け、からなる。

(もっと読む)

半導体不揮発性記憶素子及びその製造方法

【課題】MFMIS構造の半導体不揮発性記憶装置において、メモリセル面積を大きくすることなく、効率的に強誘電体キャパシタに分配電圧を加えることができる半導体不揮発性記憶装置及びその製造方法を提供する。

【解決手段】強誘電体不揮発性記憶素子において、チャンネル領域上に第1絶縁体層(3)、第1導電体層(4)、強誘電体層(5)、及び第2導電体層(6)が順次積層された構造を持ち、ソース領域とドレイン領域上にそれぞれ積層された第3導電体(9)と第4導電体(10)を持ち、第3導電体(9)及び第4導電体(10)が、第1導電体層(4)と第2絶縁体薄膜(11)を介して対向する構造を持つ。

(もっと読む)

不揮発性半導体メモリ

【課題】新たなコンセプトに基づく不揮発性半導体メモリを提供する。

【解決手段】本開示の不揮発性半導体メモリは、半導体基板11上の半導体層12と、半導体層12を貫通する複数のコントロールゲートCG11〜CG17と、第1方向の2つの端部における半導体層12内にそれぞれ配置される2つの第1導電型拡散層14と、半導体層12上で第1方向に延びる複数のセレクトゲート線SG1〜SG5と、複数のセレクトゲート線SG1〜SG5上で第2方向に延びる複数のワード線WL1〜WL7とを備える。複数のセレクトゲート線SG1〜SG5の各々は、第1方向に並ぶ複数のコントロールゲートCG11〜CG17と複数のワード線WL1〜WL7との間に接続される複数のセレクトトランジスタに共有されるセレクトゲートとして機能する。半導体層12及び複数のコントロールゲートCG11〜CG17は、メモリセルアレイを構成する。

(もっと読む)

半導体記憶装置

【課題】簡単な動作で、MFSFETに記憶された多値データを読み出すことのできる半導体記憶装置を提供することにある。

【解決手段】強誘電体膜13からなるゲート絶縁膜と、半導体膜14からなるチャネルとを有する第1の電界効果トランジスタ21で構成されたメモリセルと、メモリセルに直列に接続された読み出し用の負荷素子24とを備え、メモリセルは、強誘電体膜13の分極状態に応じた、少なくとも3値以上のチャネル抵抗値を多値データとして記憶している。メモリセルに記憶された多値データは、メモリセルと負荷素子24との間の中間電位を検出することによって読み出され、読み出し動作は、メモリセルに記憶された多値データを、チャネル抵抗値の高い状態から順に判別することによって実行される。

(もっと読む)

強誘電体膜、強誘電体膜を有する半導体装置、及びそれらの製造方法

【課題】従来よりも小型化が可能で安定した動作が可能であり、下地との密着性に優れた強誘電体膜、強誘電体膜を用いた半導体装置、その製造方法および強誘電体膜を用いた強誘電体デバイスを提供する。

【解決手段】半導体装置71は基板55、絶縁体56、酸化イットリウム膜66、強誘電体膜(STN膜)57、上部電極62を有している。酸化イットリウム膜66は強誘電体膜(STN膜)57を結晶化する際に下地となる。酸化イットリウム膜66は酸素を含み、格子情報が強誘電体膜(STN膜)57の結晶と近似している。そのため、酸化イットリウム膜66上にSTNを結晶化すると、酸素欠損がなく、かつ抗電界が200kV/cm以上の強誘電体膜(STN膜)57が得られる。

(もっと読む)

強誘電体膜、金属酸化物、半導体装置、及びそれらの製造方法

【課題】 強誘電体膜厚が薄く、長期のデータ保持特性を有する強誘電体メモリー装置に用いられる半導体装置、その製造方法、その製造装置、強誘電体膜及び強誘電体膜の製造方法を提供すること。

【解決手段】 強誘電体膜57は、膜材料として、Sr、Ta、及びNbを主成分とする強誘電体材料が用いられ、10日以上のデータ保持時間を有する。強誘電体膜を製造する方法は、強誘電体膜57を形成する膜形成工程と、前記強誘電体膜57を酸素ラジカル58によって酸化する酸素導入工程とを有する。

(もっと読む)

半導体基板上の積層構造

【課題】

シリコン基板上に(110)配向したPt薄膜を形成し、優れた特性の強誘電体素子を得ることを目的とする。

【解決手段】

MFMIS構造2の最下層のシリコン基板4上には、γ−Al2O3膜6が形成されている。γ−Al2O3膜6の直上には、酸化物導電体であるLaNiO3膜8が形成されている。LaNiO3膜8の直上には、下部電極材料であるPt膜10が形成され、さらにその直上に強誘電体材料であるPZT薄膜10が形成されている。PZT薄膜10の上面には、上部電極であるPt層12が形成されている。

(もっと読む)

半導体基板上の積層構造

【課題】シリコン基板上にバッファ層としてγ−Al2O3単結晶膜を用いることにより、優れた特性の強誘電体素子を提供する。

【解決手段】MFMIS構造薄膜2の最下層のシリコン基板4上には、γ−Al2O3単結晶膜6が形成されている。γ−Al2O3単結晶膜6の直上には、酸化物導電体であるLaNiO3膜8が下部電極として形成されている。LaNiO3膜8の直上には、強誘電体材料であるPZT薄膜10が形成されている。PZT薄膜10の上面には、上部電極であるPt層12が形成されている。

(もっと読む)

強誘電体メモリの駆動方法および強誘電体メモリ

【課題】強誘電体メモリの駆動方法であって信頼性が高い新規な駆動方法を提供する。

【解決手段】本発明の方法は、半導体11と、半導体11上に積層された絶縁膜12、電極13、強誘電体膜14および電極15とを含む強誘電体メモリの駆動方法である。この駆動方法は、強誘電体膜14を第1分極状態にする第1書き込み電圧、または、第2分極状態にする第2書き込み電圧による書き込みステップと、第2の電極15に、電圧R1ボルトと電圧R2ボルトのパルスを印加する読み出しステップとを含む。|R1|>|R2|、R1・R2<0である。第2分極状態は、第1分極状態よりも分極の大きさが小さい。第1書き込み電圧は電圧W11ボルトのパルスを含み、電圧第2書き込み電圧は、電圧W21ボルトのパルスと電圧W22ボルトのパルスとを含む。強誘電体キャパシタの抗電圧をVcボルトとすると、|W21|>|W22|、W21・W22<0、|W21|≧|W11|>|Vc|である。

(もっと読む)

強誘電体電界効果トランジスタを備える半導体装置及びこれを用いた半導体集積回路装置

【課題】強誘電体電界効果トランジスタを備えそのゲート側に設けられる回路の簡素化を図ることができる半導体装置を提供する。

【解決手段】ゲート部の等価回路が直列接続された強誘電体キャパシタCF及び常誘電体キャパシタCPからなり、強誘電体キャパシタCFの残留分極に応じた閾値電圧VTHを有する強誘電体電界効果トランジスタと、前記強誘電体電界効果トランジスタのゲート電位を固定(例えばグランド電位に固定)し、前記強誘電体電界効果トランジスタのバックゲート電位を可変する(例えば+10V/−10Vの切り替え)ことにより、前記強誘電体電界効果トランジスタのゲートとバックゲート間の電位差に応じた残留分極状態を前記強誘電体キャパシタに書き込む制御部(不図示)とを備えることを特徴とする半導体装置。

(もっと読む)

半導体集積回路

【課題】 信頼性高く不揮発記憶を書き込めるようにする。非記憶と不揮発記憶の両方、一時記憶(揮発記憶)と不揮発記憶の両方を一つの回路で行い得るようにする。

【解決手段】 前段回路の情報を状態検地強調回路Aを介して本段回路に書き込む。制御信号V selectがL、即ち/V selectがHの時、回路Aでは小電圧のVcc0とVss0が選択され、これが前段回路に印加される。この時、本段回路のn-Tr2のゲート-p型基板端子間には0V以上Vcc0-Vss0以下の電位しか印加されないのでオフとオンの判別が可能な程度にチャネル抵抗は変化するが十分な不揮発記憶書き込みを行うほどではない。V selectがH、即ち/V selectがLに変わると、回路Aでは大電圧のVcc3とVss3が選択され、これが前段回路に印加される。V selectがHになる直前のVnの論理がHならば、n-Tr2には不揮発オン状態の書込が行われ、p-Tr2には不揮発オフ状態の書込が行われる。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】FeRAMやMRAM等の半導体記憶装置の側壁部のダメージを軽減し、キャパシタリーク電流を低減する。

【解決手段】半導体基板10に配置されたスイッチングトランジスタのソース・ドレイン拡散層26と、半導体基板10及びソース・ドレイン拡散層26上に配置された層間絶縁膜8と、層間絶縁膜8上に配置された下部電極14,下部電極14上に配置された強誘電体膜16,及び強誘電体膜16上に配置された上部電極18からなる強誘電体キャパシタとを備え、上部電極18が強誘電体膜16と接する側壁部が強誘電体膜16の表面となす角度αが、上部電極18の表面近傍のハードマスクの側壁部20が強誘電体膜16の表面となす角度βよりも大きい半導体記憶装置及びその製造方法。

(もっと読む)

不揮発性半導体記憶素子及び不揮発性半導体記憶装置

【課題】1ビットを超える情報の記憶と低電源電圧化との両立を図り、且つ可及的に簡略な配線の、高集積度且つ高性能の不揮発性半導体記憶素子を得ることを可能にする。

【解決手段】半導体基板1に形成された第一の導電型の半導体領域3内に互いに向かい合う様に形成された第二の導電型のソース・ドレイン領域4と、ソース・ドレイン領域の間の半導体領域上に形成され且つ間に浮遊ゲート電極6,8を介して積層された少なくとも二層の強誘電体絶縁膜5,7,9と、浮遊ゲート電極と強誘電体絶縁膜との積層膜の、ソース・ドレイン領域を結ぶ方向と垂直な方向の側面に設けられた第一の絶縁膜10と、第一の絶縁膜が設けられた、浮遊ゲート電極と強誘電体絶縁膜との積層膜の側面に第一の絶縁膜を挟むように形成されるとともに浮遊ゲート電極と強誘電体絶縁膜との積層膜の上面に形成された制御ゲート電極11と、を備えている。

(もっと読む)

金属酸化物素子及びその製造方法

【課題】より安定な記憶保持が行えるメモリが実現できるようにする。

【解決手段】半導体基板101の上に、ビスマス(Bi)とチタン(Ti)と酸素とから構成された例えば膜厚100nmの金属酸化物層102と、上部電極103とを備え、また、半導体基板101の一部にオーミックコンタクト104を備える。金属酸化物層102は、半導体基板101の上に接して形成されている。例えば、金属酸化物層104は、Bi4Ti3O12の化学量論的組成に比較して過剰なTiを含む基部層の中に、Bi4Ti3O12の化学量論的組成の3nm〜15nm程度の複数の微結晶粒から構成されている。また、金属酸化物層104は、30〜180℃と低温条件のスパッタ法により形成されている。

(もっと読む)

金属酸化物素子及びその製造方法

【課題】より安定な記憶保持が行えるメモリを実現する。

【解決手段】基板101の上に、絶縁層102を介し、下部電極層(第1電極)103と、ビスマス(Bi)とチタン(Ti)と酸素とから構成された金属酸化物層104と、上部電極(第2電極)105とを備える。例えば、金属酸化物層104は、Bi4Ti3O12の化学量論的組成に比較して過剰なTiを含む基部層の中に、Bi4Ti3O12の化学量論的組成の3nm〜15nm程度の複数の微結晶粒から構成されている。また、金属酸化物層104は、30〜180℃と低温条件のスパッタ法により形成されている。

(もっと読む)

酸化物誘電体素子

【課題】

高誘電率で低いリーク電流密度の酸化物誘電体薄膜を備えた、酸化物誘電体素子

を提供すること。

【解決手段】

本発明の酸化物誘電体素子は、従来技術より低い酸素濃度雰囲気下で酸化物誘電体薄膜を形成するので、形成温度を低い温度にでき、酸化物誘電体薄膜が分極軸を上下方向に有する面方位で優先的に配向した結晶構造を有し、酸化物誘電体薄膜と電極材料との反応が無く、さらに酸化物誘電体薄膜の結晶粒の成長を制御するので、高い自発分極と小さい抗電界を有し、リーク電流密度も小さい。

(もっと読む)

半導体装置、半導体装置の製造方法および記憶装置

【課題】ゲート絶縁層を介した、ソース電極とドレイン電極間とのリーク電流の発生を好適に防止または低減し得る半導体装置、かかる半導体装置を簡易に製造し得る半導体装置の製造方法、および信頼性の高い記憶装置を提供すること。

【解決手段】強誘電体メモリ1は、基板2と、基板2の一方の面側に設けられたソース電極3およびドレイン電極4と、ソース電極3とドレイン電極4との間に設けられたチャネル領域51を備える半導体層5と、これらの各部と離間して設けられたゲート電極7と、ゲート電極7に対してソース電極3およびドレイン電極4を絶縁する機能を有し、強誘電体として機能する強誘電体ポリマーを主材料として構成された強誘電体層6とを備え、この強誘電体層6において、強誘電体ポリマーの主鎖が、基板2に対してほぼ平行、かつチャネル長方向とほぼ垂直な方向に沿って揃っている。

(もっと読む)

分極メモリセルアレイ

【課題】 従来の強誘電体メモリは不揮発性を利用する強誘電体薄膜がメモリセル毎に孤立している。したがって、不揮発性メモリとして集積度を高める際には強誘電体薄膜も小さな形状に裁断されることとなり、その結果、充分な特性や信頼性が得られず、微細化、高集積化には限界が生ずるという課題があった。

【解決手段】 強誘電体薄膜を複数個の電極で挟み、強誘電体薄膜の中で分極信号を転送する分極転送デバイスをメモリセルアレイとして集積し、強誘電体薄膜を連続、一体化した構成をとることにより、強誘電体特性を確保し、微細化、高集積化に適した強誘電体メモリを得る。

(もっと読む)

1 - 20 / 41

[ Back to top ]