Fターム[5F083JA20]の内容

半導体メモリ (164,393) | 材料 (39,186) | キャパシタ絶縁膜材料、ゲート絶縁膜材料 (10,102) | ハロゲン化合物系(非酸化物) (14)

Fターム[5F083JA20]に分類される特許

1 - 14 / 14

誘電体膜をパッシベーションする方法

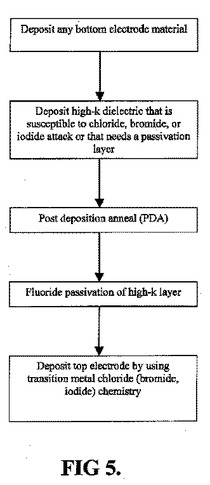

塩素、臭素又はヨウ素と反応しやすい誘電体材料にフッ素を含むパッシベーション層を堆積する方法が本明細書に開示される。パッシベーション層は、反応しやすい誘電体層を保護することができ、それにより、パッシベーション層に塩素、臭素又はヨウ素を含む前駆体を用いて堆積が可能となる。 (もっと読む)

半導体装置

【課題】ゲート絶縁膜とゲート電極との間の界面層にカーボン層を導入して、低い閾値電圧を実現している例では、カーボン層中のカーボンはSi半導体基板中に入り、欠陥準位を形成するため、EWFが不安定であった。本発明は上記問題点を解決するためになされたもので、p−metalを用いたMIS型半導体装置において、EWFを安定して増加させることが可能な半導体装置を提供する。

【解決手段】半導体基板10と、半導体基10上に形成された絶縁膜20と、絶縁膜20上に形成され、且つ、CN基又はCO基を含む界面層30と、界面層30上に形成された金属層40とを備えて半導体装置を構成する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】耐圧が改善され、信頼性が向上した不揮発性半導体メモリ及びその製造方法を与える。

【解決手段】半導体記憶装置は、半導体基板11上に形成され、オキシナイトライド化された第1ゲート絶縁膜14aを含む第1トランジスタと、半導体基板11上に形成された第2ゲート絶縁膜14bと、第2ゲート絶縁膜14b上の少なくとも一部に形成されたバリア膜20を含む第2トランジスタとを備え、前記第2ゲート絶縁膜は、前記第1ゲート絶縁膜より窒素原子濃度が低いことを特徴とする。

(もっと読む)

MFMS型電界効果トランジスタ及び強誘電体メモリ装置並びにこれらの製造方法

【課題】

本発明はMFMS(Metal−Ferroelectric−Metal−Substrate)構造を有する電界効果トランジスタ及び強誘電体メモリ装置並びにこれらの製造方法を提供する。

【解決手段】本発明に係るMFMS型電界効果トランジスタ及び強誘電体メモリ装置はソース及びドレイン領域とその間にチャネル領域が形成される基板と、基板のチャネル領域の上側に形成されるバッファ層と、バッファ層上に形成される強誘電体層、及び強誘電体層上に形成されるゲート電極を備えて構成され、バッファ層が導電性材質で構成される。

(もっと読む)

半導体装置及びその製造方法

【課題】 シリコン基板上に良質のペロブスカイト構造の単結晶を形成することができ、ペロブスカイト構造の単結晶を用いた素子の特性向上をはかる。

【解決手段】 ペロブスカイト構造の強誘電体膜を用いた半導体装置であって、単結晶シリコン基板11上に形成されたZr1-x Six O2 (0.08≦x≦0.10)のa軸配向単結晶バッファ膜13と、バッファ膜13上に形成され、Pt又はペロブスカイト構造の単結晶で形成された下部電極14と、下部電極14上に形成され、ペロブスカイト構造の単結晶で形成された強誘電体膜15と、強誘電体膜15上に形成され、Pt又はペロブスカイト構造の単結晶で形成された上部電極16とを備えた。

(もっと読む)

不揮発性半導体記憶装置

【課題】書き込み特性及び電荷保持特性に優れた不揮発性半導体記憶装置を提供することを目的とする。

【解決手段】互いに離間して形成された一対の不純物領域の間にチャネル形成領域を有する半導体層と、その上層部に、第1の絶縁層、浮遊ゲート、第2の絶縁層、制御ゲートを設ける。浮遊ゲートは少なくとも二層構造とし、第1の絶縁層に接する第1層は、半導体層のバンドギャップより小さいことが好ましい。また、半導体層のチャネル形成領域の伝導帯の底のエネルギーレベルより、浮遊ゲートの伝導帯底のエネルギーレベルを低くすることにより、キャリアの注入性を向上させ、電荷保持特性を向上させるためである。

(もっと読む)

固体素子構造とそれを使用した電気・電子素子及び電気・電子機器

【課題】

フラーレン分子によるナノ構造の電気・電子特性を自在に制御可能とするナノデバイス構造を提供する。

【解決手段】

フラーレン分子層を電極間に配設した固体素子構造を有し、電極への電圧の印加状態によってフラーレン分子層の導電性を制御可能としているフラーレン分子デバイス構造とする。

(もっと読む)

記憶素子、メモリ

【課題】スピンポンピング現象の発生を抑制することができると共に、充分な熱安定性を有する記憶素子を提供する。

【解決手段】情報を磁性体の磁化状態により保持する記憶層17に、トンネル絶縁層16を介して磁化固定層31が設けられ、積層方向に電流を流してスピン偏極した電子を注入することにより、記憶層17の磁化M1の向きが変化して、情報が記録される記憶素子3において、記憶層17の磁化固定層31とは反対側に、スピン偏極した電子の拡散を抑制するスピンバリア層18を設け、このスピンバリア層18を、酸化物、窒化物、フッ化物から選ばれる1種以上の材料から構成する。

(もっと読む)

半導体記憶装置及び半導体記憶装置の製造方法

【課題】

隣接するトランジスタ間のゲート間絶縁膜を介した電荷の移動を防止することが可能な半導体記憶装置を提供する。

【解決手段】 p型半導体層20、p型半導体層20上にトンネル絶縁膜12a〜12gを介してマトリックスをなして配置された複数のフローティングゲート電極FG1a〜FG7a、複数のフローティングゲート電極FG1a〜FG7a上にのみ各々配置された複数のゲート間絶縁膜14aa〜14ga、複数のゲート間絶縁膜14aa〜14ga上に各々配置された複数のコントロールゲート電極CG1a〜CG7a、及びマトリックスのカラム方向において複数のゲート間絶縁膜14aa〜14gaを互いに分離するように複数のコントロールゲート電極CG1a〜CG7aの間からp型半導体層20の内部まで埋め込まれた素子分離絶縁層STIを備える。

(もっと読む)

カーボンナノウォールの処理方法、カーボンナノウォール、カーボンナノウォールデバイス

【課題】ナノスケールを有する新規なカーボン構造物であるカーボンナノウォールの処理方法、カーボンナノウォール、カーボンナノウォールデバイスを提供する。

【解決手段】カーボンナノウォール(CNW)に対して形状処理を行う。形状処理としてはプラズマエッチング等のドライエッチング処理を採用できる。カーボンナノウォールを構成するグラフェンシートの少なくも先端部の厚みを根元部の厚みよりも減少させることが好ましい。

(もっと読む)

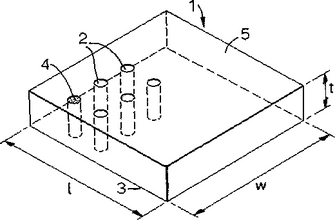

基板上への層の堆積法

本発明によれば、多孔性シリコン、シリカ、又はアルミナ基板の孔に屈折率nが電圧依存性を有する材料を堆積させる方法であって、堆積される前記材料の前駆体物質を前駆体溶液として設けること、前駆体溶液の液滴の微細ミストを形成すること、及び、前記液滴を前記多孔性基板に付着させること、を含む方法が提供される。本発明は初めて、充填率が少なくとも60%である多孔性シリコン、シリカ、及びアルミナ基板を提供するものである。100%近い充填率が実現可能である。上部電極及び下部電極が設けられると、充填された多孔性シリコン、シリカ、及びアルミナウェーハを電圧依存性を有するフォトニックデバイスとして使用することができる。例えばランダムアクセスメモリ等のマイクロ電子デバイスの製造において使用するべく、シリコン基板表面の溝を内張りするために、同じ方法を用いることができる。  (もっと読む)

(もっと読む)

半導体装置の製造方法、製造装置、シミュレーション方法、及びシミュレータ

【課題】 半導体装置製造プロセスを、テストピースなしに、所望の工程通り又は修正しながら進行することを可能とする半導体装置の製造方法を提供すること。

【解決手段】 複数の工程からなる半導体装置の製造方法において、前記複数の工程の少なくとも1つにおける実観測データを得る工程と、abinitio分子動力学プロセスシミュレータ又は経験的ポテンシャルを与えた分子動力学ミュレータにより、前記複数の工程の少なくとも1つにおける予測データを得る工程と、前記予測データと実観測データとを逐次、実時間で比較検定する工程と、前記比較検定により、製造工程因子の設定値と、前記実観測データから推測される前記複数の製造工程因子との間に有意差が認められた場合、前記製造工程因子を逐次実時間で修正処理する工程とを具備することを特徴とする。

(もっと読む)

自己整合型メモリ素子およびワード線

有機ポリマー層(116、2108、2132、2168)と、第1の伝導性(例えば、銅)層(例えば、ビット線)(104、108)の上方に形成された電極層(120、2112、2128、2164)とを有する有機ポリマーメモリセルが提供される。メモリセルは、第2の導電層(例えば、ワード線を形成する)(136、2148、2160)に接続され、さらに詳しく言えば、メモリセルの電極層の上部は、第2の導電層に接続される。任意に、導電層の上方に、伝導促進層(112、2136)が形成される。誘電材料はメモリセルを分離する。メモリセルは、第1の導電層に形成されたビット線と、第2の導電層に形成されたワード線と自己整合される。  (もっと読む)

(もっと読む)

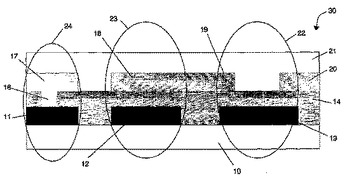

不揮発性強誘電体メモリ装置の製造方法及びその方法によって得られるメモリ装置

本発明は、トランジスタ22及びキャパシタ23を含んでいる不揮発性強誘電体メモリ装置30に関し、特に、不揮発性で、電気的に消去可能、かつプログラム可能な強誘電体メモリ素子及びそのような不揮発性強誘電体メモリ装置30を生産する方法に関する。本発明による方法は、トランジスタ22のゲート誘電体層及びキャパシタ23の誘電体層は同一の有機又は無機強誘電体層から作られるので、限られた数のマスクステップを含む。  (もっと読む)

(もっと読む)

1 - 14 / 14

[ Back to top ]