Fターム[5F083KA01]の内容

Fターム[5F083KA01]の下位に属するFターム

Fターム[5F083KA01]に分類される特許

1,281 - 1,285 / 1,285

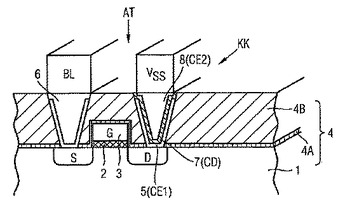

半導体メモリセルおよびその製造方法

本発明は、ストレージキャパシタが選択トランジスタ(AT)に接続されている半導体メモリセル、および、その製造方法に関するものである。本発明では、ストレージキャパシタは、ソース領域Sまたはドレイン領域Dのための少なくとも1つのコンタクトホールにおいて、コンタクトホールキャパシタ(KK)として形成されている。このような半導体メモリセルは、特にコスト効率よく製造することができ、かつ高集積度を達成できる。  (もっと読む)

(もっと読む)

有機両極性半導体を使用する不揮発性強誘電体薄膜デバイス及びそのようなデバイスを処理するための方法

有機強誘電体高分子と有機両極性半導体との組み合わせを備える不揮発性強誘電体メモリデバイスが提案されている。本発明に係るデバイスは、高分子に適合し、また、高分子の利点、即ち、溶液処理、低コスト、低温層堆積及びフレキシブル基板との適合性を十分に活用している。  (もっと読む)

(もっと読む)

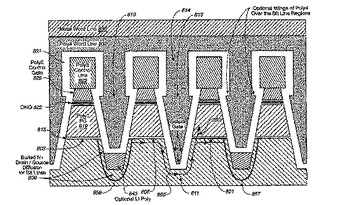

ピラー構造セルのフラッシュメモリ技術

ピラー形不揮発性メモリセル803は各々がトレンチ810によって隣接するメモリセルから絶縁されるメモリセルを各々有している。各メモリセルは基板上に処理層を積層することによって形成される。すなわち、トンネル酸化物層815、ポリシリコンフローティングゲート層819、ONOまたは酸化物層822、ポリシリコンコントロールゲート層825である。ステップの多くの態様が自己整合される。これらのメモリセルのアレイにはより少ない分割しか必要ない。さらに、このメモリセルは、電子がフローティングゲート819に対して直角またはほぼ垂直843に向けられるので、プログラミング特性が増強される。  (もっと読む)

(もっと読む)

縦型スプリットゲートNROMメモリ装置及びその形成方法

【課題】NROMセルの利点と縦型メモリセルの利点とを備えるメモリデバイスを提供する。

【解決手段】スプリットゲート縦型NROMメモリセル(1890)は、複数の酸化物柱状体(1830、1831)から構成される。複数の酸化物柱状体の各々の上部にはソース/ドレイン領域(1840、1841)が形成される。溝部が、酸化物柱状体の各対の間に形成される。ポリシリコン制御ゲート(1800)が、酸化物柱状体の対の間の溝部に形成される。ポリシリコンプログラムゲート(1805、1806)が、制御ゲートと各酸化物柱状体との間に形成される。プログラムゲートは、各酸化物柱状体の側壁に沿って延在する。ゲート絶縁層(1802、1803)が、各プログラムゲートとその近傍の酸化物柱状体との間に形成される。各ゲート絶縁層は、少なくともひとつの電荷を捕獲する電荷捕獲構造を有する。一実施形態において、ゲート絶縁構造は、酸化物−窒化物−酸化物の層である。中間絶縁層(1822、1824)が、プログラムゲートと制御ゲートとの間に形成される。

(もっと読む)

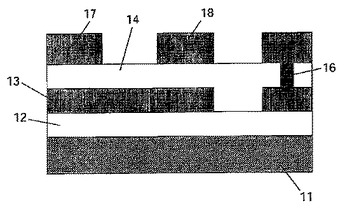

1T‐nメモリセル積層構造体

本発明は、クロスポイントと1T‐1セルとの双方の設計に基づくある種の利点を導入するためのメモリ技術及びメモリアレイに関する新規な変更に関する。これらの設計のある特徴を組み合わせることにより、1T‐1セル設計における読出し時間の高速化及び信号対雑音比の増大と、クロスポイント設計における高記録密度化との双方が達成される。そのために、単一のアクセストランジスタ16を用いて、“Z”軸方向に配置された複数のメモリアレイ層で垂直方向に互いに上下に積み重ねうる多重メモリセルを読出すようにする。  (もっと読む)

(もっと読む)

1,281 - 1,285 / 1,285

[ Back to top ]