Fターム[5F083KA03]の内容

Fターム[5F083KA03]に分類される特許

1 - 20 / 78

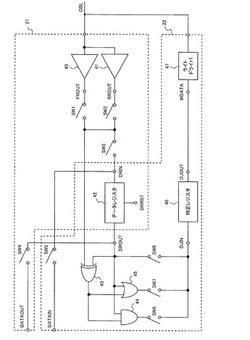

半導体記憶装置及び半導体装置

【課題】 可変抵抗素子への電圧印加極性が異なる2種類の書き込み動作後の各ベリファイ動作を夫々低消費電力且つ高速に実行可能な半導体記憶装置を提供する。

【解決手段】 書き込み回路22が、メモリセルの一端側から可変抵抗素子を経由して他端側へ電流を流すことで可変抵抗素子の電気抵抗を低抵抗化させるセット動作と、メモリセルの他端側から可変抵抗素子を経由して一端側へ電流を流すことで可変抵抗素子の電気抵抗を高抵抗化させるリセット動作を夫々実行可能に構成され、読み出し回路21が、メモリセルの一端側から可変抵抗素子を経由して他端側へ電流を流すことで可変抵抗素子の抵抗状態を読み出す第1読み出し動作と、メモリセルの他端側から可変抵抗素子を経由して一端側へ電流を流すことで可変抵抗素子の抵抗状態を読み出す第2読み出し動作を夫々実行可能に構成されている。

(もっと読む)

半導体記憶装置

【課題】比較的小振幅な信号が伝送される第1の信号線対で発生するカップリングノイズを低減しつつ、該第1の信号線対と直交する方向に異なる配線層で配置される、第1の信号線対よりも振幅が大きい信号が伝送される第2の信号線毎の信号遅延量の差異を低減できる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、メモリアレイ上で配線される第1の振幅信号が伝送される複数の第1の信号線対と、該第1の信号線対と直交する方向に異なる配線層で配置される複数の第2の信号線とを有する。第1の信号線対は、メモリマットの列毎に配置され、メモリマットの列方向において、それぞれ所定の一定間隔で交差される。また、第1の信号線対の交差部位は第2の信号線の配線方向におけるメモリマットの列毎にずらして配置される。

(もっと読む)

半導体記憶装置

【課題】アドレス信号の配線に起因する配線容量を低減させ、アクセス速度の高速化を実現する半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のビット線と複数のワード線に対応して設けられた複数のメモリセルと、複数のメモリセルのいずれかを特定するためのアドレス信号を中継する中継バッファと、複数のワード線のうち、中継バッファにて中継されたアドレス信号に応じたワード線を選択するトランジスタを複数有するワード線ドライバ回路と、を備え、トランジスタでは、2つの拡散層のうち一方の拡散層が他のトランジスタの拡散層と共有し、拡散層を共有している2つのトランジスタで構成される複数の共有回路が、複数のトランジスタ群に分けられ、複数のトランジスタ群のうち隣り合う前記トランジスタ群の隙間部分に、隣り合うトランジスタ群のいずれかのゲート配線が設けられ、中継バッファはトランジスタ群のゲート配線と接続される。

(もっと読む)

ダイオードストラッピングを備えた熱アシストフラッシュメモリ

【課題】フラッシュメモリの動作速度及び耐久性を向上させる技術の提供。

【解決手段】メモリが、行及び列を含むメモリセルのアレイを有している。該メモリは、アレイ内の単数又は複数のワード線上の第1の離隔位置のセットに第1のバイアス電圧を印加するとともに、単数又は複数のワード線上の第2の離隔位置のセットに第1のバイアス電圧とは異なる第2のバイアス電圧を印加する、ワード線に結合された回路部を有し、第1の離隔位置のセットにおける位置は、第2の離隔位置のセットの位置の間に介在しており、それにより、第1の離隔位置のセットにおける位置と第2の離隔位置のセットにおける位置との間に、単数又は複数のワード線の加熱をもたらす電流の流れが誘導される。

(もっと読む)

半導体装置および配線レイアウト方法

【課題】配線間のピッチを縮小可能にした半導体装置を提供する。

【解決手段】半導体基板に形成された複数のトランジスタと、第1の方向に延在する第1の配線を備えた第1の配線層と、第1の配線層よりも上層に設けられ、第1の方向と交差する第2の方向に延在し、第1の配線と電気的に接続された第2の配線を備えた第2の配線層と、半導体基板と第1の配線層との間に設けられ、複数のトランジスタに接続する第1の中継配線と、第1の中継配線が形成された第1の中継配線層と第1の配線層との間に設けられ、第1の配線と複数のトランジスタのうちの一つとを接続する第2の中継配線とを有する構成である。

(もっと読む)

半導体装置及び情報処理システム

【課題】ビット線構成が階層化されたメモリセルアレイにおいて、回路規模が小さくチップ面積の増加及びタイミングスキューを抑制可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、ビット線構成がローカルビット線LBLとグローバルビット線GBLとに階層化され、ローカルビット線LBLとグローバルビット線GBLとの間の接続を制御する階層スイッチSWを備えている。階層スイッチSWの制御のため、ローカルスイッチ制御線LSLとメインスイッチ制御線MSLが配置される。ローカルスイッチ制御線LSLはローカルスイッチドライバLSDにより駆動され、メインスイッチ制御線MSLはメインスイッチドライバMSDにより選択的に活性化される。メモリセルアレイの規模が大きくなっても、ローカルスイッチドライバLSDとメインスイッチドライバMSDの配置によるレイアウト面積の増大及びタイミングスキューを抑制することができる。

(もっと読む)

不揮発性半導体記憶装置

【課題】書き込み可能回数が多く、信頼性の高い不揮発性半導体記憶装置を提供する。

【解決手段】複数の第1の配線、複数の第1の配線に交差する複数の第2の配線、並びに複数の第1及び第2の配線の各交差部に配置された電気的書き換え可能な抵抗値をデータとして不揮発に記憶する可変抵抗素子を含む複数のメモリセル、を有するメモリセルアレイと、複数の第1の配線の少なくとも一端に接続され、第1の配線を選択する第1のデコーダと、複数の第2の配線の両端に接続されて第1のデコーダが選択した第1の配線と第2の配線の両端との距離に応じていずれか一方が第2の配線を選択する少なくとも一対の第2のデコーダと、第1のデコーダ及び第2のデコーダによって選択された第1の配線及び第2の配線間に所定の電圧を印加する電圧印加回路とを備える。

(もっと読む)

半導体記憶装置

【課題】低電源電圧下においても、安定かつ高速に動作する半導体記憶装置を実現する。

【解決手段】メモリセル列ごとにアレイ電源線(ARVD)およびダウン電源線(DWVD)を配置する。ダウン電源線は、読出し時に接地に結合され、書込み時にフローティング状態とされる。書込み時、選択列のアレイ電源線への電源電圧の供給を停止するとともに該アレイ電源線を対応のダウン電源線に接続する。電源系統を複雑化することなく、低電源電圧下においても安定にデータの書込/読出を行うことのできる半導体記憶装置を実現することができる。

(もっと読む)

半導体装置

【課題】リーク電流が発生しにくく、低消費電力化に好適な半導体装置を提供する。

【解決手段】本発明の半導体装置は、半導体基板12内に埋め込まれてX方向に並列して延在する複数のビット線BLと、X方向と交差するY方向に延在するワード線と、ビット線BLと前記第2配線との交点に設けられたメモリセルMと、複数のビット線BLのうち最外列のビット線BLの外側に設けられ、X方向に延在してビット線BLと並走するダミービット線DBLとを含み、ダミービット線DBLが、半導体基板12に供給される電位と同じ電位が供給されるダミービット線(第1ダミー配線)DBL<0>、DBL<1>、DBL<2>を含むことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体素子を有する構造体を複数積層して形成される半導体装置において、上層の構造体を形成する工程で用いられるレーザーによって、下層の構造体に熱負荷が生じることを防ぐ技術を提供する。

【解決手段】積層された複数のメモリマトリクスにより構成される相変化メモリにおいて、下層のメモリマトリクスと、下層のメモリマトリクス上に形成された上層のメモリマトリクスとの間に金属膜19を配置する。これにより、上層のメモリマトリクスを形成する際に用いられるレーザーを金属膜19により反射させることで、レーザーが金属膜19を透過することを防ぎ、下層のメモリマトリクス内の相変化材料層16などが直接レーザーによって加熱されることを防ぐ。

(もっと読む)

半導体装置

【課題】集積度の高い相変化メモリを実現する。

【解決手段】本発明による半導体装置は、複数のワード線と、複数のワード線と直交する複数のビット線との交点に配置された複数のメモリセル群を有する。複数のメモリセル群は、直列接続された第一乃至第二のメモリセルを有する。第一乃至第二のメモリセルの各々は、並列接続される選択トランジスタと抵抗性記憶素子とを有する。第一のメモリセルにおける選択トランジスタのゲート電極は、第一のゲート線に接続され、第二のメモリセルにおける選択トランジスタのゲート電極は、第二のゲート線に接続される。そして、複数のワード線を駆動する第一の回路ブロック(ワードドライバ群WDBK)は、第一乃至第二のゲート線を駆動する第二の回路ブロック(相変化型チェインセル制御回路PCCCTL)と、複数のメモリセル群(メモリセルアレーMA)との間に配置される。

(もっと読む)

半導体装置

【課題】ライト動作などの制御に比較的長い時間を要する半導体装置を小型化する。

【解決手段】第1及び第2のメモリセルアレイに其々対応して設けられたビット線制御回路BLC(1U,1)、BLC(1U,2)と、ビット線制御回路BLC(1U,1)、BLC(1U,2)に共通に接続され、第1の制御信号XCont(1U)を伝送する制御信号線と、ビット線制御回路BLC(1U,1)、BLC(1U,2)に其々接続され、第2及び第3の制御信号YCont(1),YCont(2)を其々伝送する制御信号線と、を備える。ビット線制御回路BLC(1U,1)は、第1及び第2の制御信号が活性化された場合に第1のメモリセルアレイに対する動作制御を行い、ビット線制御回路BLC(1U,2)は、第1及び第3の制御信号が活性化された場合に第2のメモリセルアレイに対する動作制御を行う。

(もっと読む)

半導体装置

【課題】実現が容易な構成により、メモリマットのスタンバイ電流を規格値以下に抑える。

【解決手段】それぞれ複数のメモリセルMCの第1のノードに共通に接続される複数のドレイン線DLと、複数のメモリセルMCそれぞれの第2のノードに接続される複数のビット線BLと、ソース線SLと、複数のドレイン線DLをソース線SLに接続するトランジスタ13と、メモリセルMCへのアクセスに対応してソース線SLを接地電位VSSに接続するトランジスタ31とを備え、複数のメモリセルMCがすべて非活性である制御時、ドレイン線DLを接地電位VSSより高いドレイン電位VDRに制御し、かつ、トランジスタ13,31を非活性に制御することによって、ソース線SLをフローティングに制御する。

(もっと読む)

半導体集積回路装置

【課題】多層配線の下地半導体基板への配線引き出し部のコンタクト抵抗均一化を図った半導体集積回路装置の提供。

【解決手段】半導体集積回路装置は、半導体基板と、前記半導体基板上に複数層積層形成された配線と、前記配線の引き出し領域に前記配線の延長部として形成されて、所定幅のスペースを介して対向するメタル片対により構成されるフックアップ部73と、前記フックアップ部のメタル片対のスペースを貫通するように埋め込まれたコンタクト導体72とを有し、前記配線の少なくとも2層の間で前記フックアップ部のメタル片対のスペース幅を異ならせた。

(もっと読む)

不揮発性半導体記憶装置

【課題】正確な読み出しを実行可能な不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、メモリトランジスタMTr1〜8が直列に接続された複数のメモリストリングMSと、メモリストリングMSの一端に一端を接続されたドレイン選択トランジスタSDTrと、複数のドレイン側選択トランジスタSDTrの他端に共通接続されたローカルビット線LBLと、ローカルビット線LBLに一端を接続されたスイッチ回路SWと、複数のスイッチ回路SWの他端に共通接続されたグローバルビット線GBLとを備える。メモリストリングMSは、柱状部を含むU字状半導体層と、柱状部の側面を取り囲むように形成された電荷蓄積層と、電荷蓄積層を取り囲むように形成されたワード線導電層とを備える。

(もっと読む)

半導体記憶装置

【課題】積層構造を有するメモリセルアレイの平坦性を保持する。

【解決手段】半導体記憶装置は、縦方向に積層され、かつ第1の方向に延在する複数の第1の選択線をそれぞれが有する複数の第1の選択線群WLと、第1の配線群WLと交互に積層され、かつ第1の方向に交差する第2の方向に延在する複数の第2の選択線をそれぞれが有する複数の第2の選択線群BLと、第1の選択線と第2の選択線との間に配置されたメモリセルMCとを具備する。複数の第1の選択線群WLのうち偶数層と奇数層とは、第2の方向にずれて配置される。

(もっと読む)

半導体装置及びこれを備えるシステム

【課題】ビット線が階層化された半導体装置においてセンス感度を向上させる。

【解決手段】グローバルビット線GBL1,BGL2の電位差を増幅するセンスアンプSAと、グローバルビット線GBL1,BGL2に接続された複数の階層スイッチSWと、階層スイッチSWを介してグローバルビット線GBL1,GBL2にそれぞれ接続される複数のローカルビット線を含むメモリマットMAT1,MAT2と、階層スイッチSWを活性化させる制御回路と、を備える。制御回路は、グローバルビット線GBL1,GBL2に沿ったセンスアンプSAからの距離が互いに等しい階層スイッチSWを活性化させる。本発明によれば、どのローカルビット線が選択された場合であっても、寄生CR分布定数に差が生じないことから、センス感度の低下を防止することが可能となる。

(もっと読む)

半導体装置及びこれを備えるシステム

【課題】ビット線が階層化された半導体装置において、端部に位置するメモリマットを他のメモリマットと同様に扱えるよう構成する。

【解決手段】グローバルビット線GBL及びそれより短いダミーグローバルビット線DGBLと、これらの電位差を増幅するセンスアンプSAと、階層スイッチSWを介してグローバルビット線GBLに接続されるローカルビット線LBLをそれぞれ含む複数のメモリブロックMBと、ダミー階層スイッチDSWを介してダミーグローバルビット線DGBLに接続されるLBLと同じ長さのダミーローカルビット線DLBLを含むダミーメモリブロックDMBと、階層スイッチSWのいずれか及びダミー階層スイッチDSWを活性化させる制御回路100とを備える。これにより、端部に位置するメモリマットと他のメモリマットとを同じ記憶容量とすることが可能となる。

(もっと読む)

メモリ半導体装置、その製造方法、及び動作方法

【課題】メモリ半導体装置、その製造方法及び動作方法を提供する。

【解決手段】メモリ半導体装置は、基板の上部面に垂直長軸を有し、2次元的に配列される複数の半導体パターン、及び複数の半導体パターンを横切る長軸を有しながら、複数の半導体パターン間で3次元的に配列される複数のワードラインを包含できる。

(もっと読む)

3次元メモリー装置、及びそのプログラム方法

【課題】集積度の増加と共にプログラムディスターバンス問題を効果的に減らすことができる3次元メモリー装置、及びそのプログラム方法が提供される。

【解決手段】本発明の3次元メモリー装置は、複数のワードライン平面が積層されたメモリーセルアレイ、選択されたワードライン平面に具備された少なくとも2以上のページのメモリーセルを同時にプログラムする書込み読出し回路、そして前記書込み読出し回路のプログラム動作を制御する制御回路を含むことができる。

(もっと読む)

1 - 20 / 78

[ Back to top ]