Fターム[5F083PR29]の内容

Fターム[5F083PR29]に分類される特許

361 - 364 / 364

VSS抵抗が低く、ドレイン誘起バリアハイト効果が低減されたフローティングゲートメモリセルの構造およびその製造方法

フローティングゲートメモリセル202は、基板204上に基板204中のチャネル領域222を覆う状態で配置されたスタックゲート構造208を有する。フローティングゲートメモリセル202は更に、基板204中にスタックゲート構造208に隣接して形成されたリセス228を有し、リセス228は側壁230、底部232、深さ236を有する。フローティングゲートメモリセル202は更に、リセス228の側壁230に隣接し、且つ、スタックゲート構造208の下に配置されるソース234を有する。フローティングゲートメモリセル202は更に、リセス228の底部232にあり、ソース234の下に配置されるVss接続領域238を有し、Vss接続領域238はソース234に接続されている。Vss接続領域238はリセス228の底部232の下に配置されているため、チャネル領域222におけるソース234の側方拡散が低減されている。  (もっと読む)

(もっと読む)

不揮発性メモリ装置を製造する方法及びそれによって得られるメモリ装置

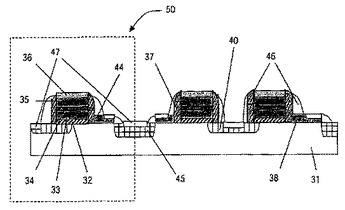

本発明は、ダブル・ゲート・スタック及びシングル・アクセス・ゲートを備える不揮発性メモリ・セル(50)を加工する方法に関する。この方法は、アクセス・ゲートを加工する方法を、自己整合的な、ソース注入とは別のドレイン注入と組み合わせる。本発明の方法は、マスク位置合せ精度を考慮せずに、メモリ装置を消去するための延長されたドレインを自己整合的に注入することを可能にする。さらに、この方法は、さらなるマスクを使用せずにドレイン及びソース注入を互いに異なるドーピングで実施する方法を提供する。  (もっと読む)

(もっと読む)

FETベースの磁気ランダム・アクセス・メモリ・デバイス用の自己整列型導電線およびこれを形成する方法

【課題】下部メタライズ線(302)に導電的に結合された横方向の金属ストラップ(326)を含む、電界効果トランジスタ(FET)ベースの磁気ランダム・アクセス・メモリ(MRAM)デバイス用の導電線構造を提供すること。

【解決手段】金属ストラップ(326)上に磁気トンネル接合(MTJ)スタック(316)が形成され、MTJスタック(316)を覆って金属シールド(324)が形成され、金属シールド(324)は金属ストラップ(326)に対して自己整列される。上部メタライズ線(332)は金属シールド(324)に導電的に結合され、金属シールド(324)は上部メタライズ線(332)の形成時にエッチ・ストップとして働く。

(もっと読む)

垂直方向の突起部を有するフローティングゲート構造

基板面から離れて延在する突起部を有するフローティングゲート構造を開示する。この突起部によって、フローティングゲートとコントロールゲートとを結合するための増加した表面積をフローティングゲートに提供することが可能となる。1つの実施形態では、フローティングゲートの個々の側面でワードラインが下方へ延在して、同じ列の隣接するフローティングゲートを遮蔽する。別の実施形態では、突起部を有するフローティングゲートの組立て製造処理工程を開示する。残りのフローティングゲートに対して自己位置合せを行うために突起部を形成してもよい。  (もっと読む)

(もっと読む)

361 - 364 / 364

[ Back to top ]