Fターム[5F083ZA09]の内容

Fターム[5F083ZA09]に分類される特許

1 - 11 / 11

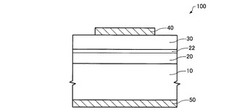

半導体メモリ装置およびその製造方法

【課題】消去、書き込みを繰り返してもON/OFF比を高く維持できる半導体メモリ装置を提供する。

【解決手段】本発明に係る半導体メモリ装置100は、基板10と、基板10の上に形成された炭化シリコン層20と、炭化シリコン層20の上に形成された金属酸化物層30と、金属酸化物層30と電気的に接続された第1電極40と、基板10と電気的に接続された第2電極50と、を含む。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】作製工程が簡略化され、容量素子の面積が縮小化されたメモリ素子を有する半導体装置を提供することを課題とする。

【解決手段】基板上に第1の半導体膜と、第2の半導体膜を形成し、第1の半導体膜及び第2の半導体膜を覆って第1の絶縁膜を形成し、第1の半導体膜及び第2の半導体膜上に、第1の絶縁膜を介してそれぞれ第1の導電膜及び第2の導電膜を形成し、第1の導電膜を覆って第2の絶縁膜を形成し、第1の半導体膜上に設けられた第1の導電膜上に第2の絶縁膜を介して第3の導電膜を選択的に形成し、第1の半導体膜に第3の導電膜をマスクとして不純物元素を導入し、第2の半導体膜に第2の導電膜を通して不純物元素を導入する。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化に対して有利であり、コンタクト電極の抵抗を低くすることが可能な半導体装置及びその製造法を提供する。

【解決手段】選択ゲートトランジスタSTの選択ゲート電極SG、及び周辺トランジスタTRの周辺ゲート電極TGを有し、ゲート電極SG、TG間の不純物拡散層28上及びゲート電極側面に第1絶縁膜30、第1バリア膜31を有し、第1バリア膜31上にゲート電極SG、TG間を埋める第2絶縁膜32を有する。ゲート電極SG、TG間の不純物拡散層28上の第1絶縁膜30及び第1バリア膜31に第1幅A1で第1方向に伸びるコンタクトホール下部35aが、第2絶縁膜32を貫通して底部がコンタクトホール下部35aと連接し、第1方向に第1幅A1よりも大きい第2幅A2を有するコンタクトホール上部35bが設けられ、コンタクトホール下部35a及びコンタクトホール上部35b内にコンタクト電極36が設けられている。

(もっと読む)

半導体集積装置

【課題】SOI基板内の埋め込み酸化膜を薄膜化しても、デバイス特性が劣化することがなく、バイポーラトランジスタも形成可能な半導体集積回路を提供する。

【解決手段】SOI基板3内の埋め込み酸化膜2の上面には、FBC4、NFET5およびPFET6が互いに分離して形成されている。FBC4の下方に位置するp支持基板1内には、埋め込み酸化膜2に接してnウェル拡散領域7が形成されている。NFET5の下方に位置するp支持基板1内には、pウェル拡散領域8が形成されている。PFET6の下方に位置するp支持基板1内には、nウェル拡散領域9が形成されている。NFET5とPFET6の形成箇所に合わせて、埋め込み酸化膜2の下面側にそれぞれpウェル拡散領域8とnウェル拡散領域9を形成して、各ウェル拡散領域にそれぞれ所定の電圧を印加するため、NFET5とPFET6にバックチャネルが形成されなくなり、デバイス特性がよくなる。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、キャパシタの誘電膜用の絶縁膜の膜厚が、増速酸化し、所望の膜厚になり難いという問題があった。

【解決手段】本発明の半導体装置では、キャパシタ3の形成領域において、キャパシタの下部電極用のP型の拡散層41上には、キャパシタ3の誘電膜用のシリコン酸化膜42が形成されている。シリコン酸化膜42上には、キャパシタ3の上部電極用のポリシリコン膜43、44が形成されている。そして、ポリシリコン膜43の膜厚は、イオン注入の際に、不純物が通過できる膜厚である。この構造により、シリコン酸化膜42の膜厚が所望の範囲となり、キャパシタ3の容量値は精度よく形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、キャパシタの誘電膜用の絶縁膜の膜厚が、増速酸化し、所望の膜厚になり難いという問題があった。

【解決手段】本発明の半導体装置では、キャパシタ3の形成領域において、キャパシタの下部電極用のN型の拡散層40上には、キャパシタ3の誘電膜用のシリコン酸化膜41が形成されている。シリコン酸化膜41上には、キャパシタ3の上部電極用のポリシリコン膜42、43が形成されている。そして、ポリシリコン膜42の膜厚は、イオン注入の際に、不純物が通過できる膜厚である。この構造により、シリコン酸化膜41の膜厚が所望の範囲となり、キャパシタ3の容量値は精度よく形成される。

(もっと読む)

半導体記憶装置

【課題】ダミーセルに生じるチャージポンピング現象の対策を施し、かつ、従来よりも回路規模の小さい半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、電気的に浮遊状態のフローティングボディ50を含み、該フローティングボディ内の多数キャリアの数によってデータを記憶するメモリセルMCと、メモリセルのデータを検出するときに検出の基準となる基準電位を生成するダミーセルDCと、メモリセルのゲートに接続されたワード線WLL、WLRと、ダミーセルのゲートに接続されたダミーワード線DWLL、DWLRと、メモリセルのソースまたはドレインおよびダミーセルのソースまたはドレインに接続されたビット線BLL、BLRと、ダミーセルのソースまたはドレインに隣接し、該ダミーセルのフローティングボディと同じ導電型の拡散層80と、ダミーセルのフローティングボディ、ダミーセルのソースまたはドレイン、および、拡散層はバイポーラトランジスタBPTL、BPTRを構成する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】不揮発性メモリ素子と電界効果トランジスタとバイポーラトランジスタとを備えた所望特性の半導体装置を低コストの下に製造し易い半導体装置の製造方法を得ること。

【解決手段】不揮発性メモリ素子と、電界効果トランジスタと、バイポーラトランジスタとを備えた半導体装置を製造するにあたって、1つのポリシリコン膜をパターニングして、不揮発性メモリ素子での浮遊ゲート電極の元となる浮遊ゲート用ポリシリコン膜33aとバイポーラトランジスタのエミッタ電極62とを一緒に形成し、その後、不揮発性メモリ素子での絶縁膜の元となる浮遊ゲート用積層膜を浮遊ゲート用ポリシリコン膜33a上に形成してから、不揮発性メモリ素子の制御ゲート電極、絶縁膜、および浮遊ゲート電極、ならびに電界効果トランジスタのゲート電極を形成する。

(もっと読む)

半導体装置

【課題】D-Aコンバータの性能を向上させることができる。

【解決手段】複数の第1メモリセルを含むメモリマットと、複数の第1メモリセルに接続される複数の出力線とを具備するDACであって、複数のメモリセルの夫々は、バイポーラトランジスタを含み前記バイポーラトランジスタの接合を破壊するか否かで情報を不揮発で記憶する第1メモリ部と、第1メモリ部に接続され複数の出力線のうち対応する一つに情報を出力する第2メモリ部とを有し、第2メモリ部へ情報を書き込む場合に、第1メモリ部から第2メモリ部へ情報を転送する第1モードと、第2メモリ部を外部から特定して情報を書き込む第2モードとを有する。

(もっと読む)

半導体装置

【課題】2つのバイポーラトランジスタを用いたアンチヒューズにおいて、書込み電圧を低減する。

【解決手段】第1エミッタ電極8と、第1ベース電極6と、第1コレクタ電極7とを第1領域の上方に有する第1トランジスタQ1を具備し、第1ベース電極6と第1ベース領域の間を接続するベース引出しポリシリコン9は、第1領域の外に設けられる第2領域の上方を通過させ、抵抗値を付加する。

(もっと読む)

メモリ回路構造およびその製造方法

本発明は、メモリを構成する各部分が2つの異なる基板上に配置されている、メモリ回路構造(10)に関するものである。メモリセルアレイ(16)は、特に、1つの基板に配置されている。制御回路(38)は、特に、他の基板に配置されている。メモリを適切に分割することで、製造コストの大幅な低減を図ることができる。  (もっと読む)

(もっと読む)

1 - 11 / 11

[ Back to top ]