Fターム[5F083ZA25]の内容

Fターム[5F083ZA25]に分類される特許

1 - 20 / 23

半導体装置

【課題】貫通電極を用いた積層型の半導体装置において不良のある信号経路を救済する。

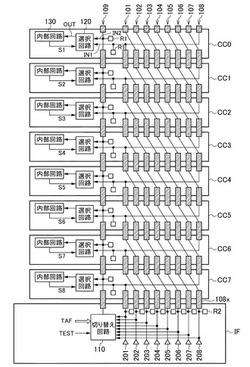

【解決手段】インターフェースチップIFと、互いに積層されたコアチップCC0〜CC7と、コアチップCC0〜CC7を貫通する複数の貫通電極TSV3により構成され、コアチップCC0〜CC7をインターフェースチップIFにそれぞれ個別に接続する複数の第1の信号経路と、コアチップCC0〜CC7を貫通する複数の貫通電極TSV1により構成され、コアチップCC0〜CC7をインターフェースチップIFに共通接続する第2の信号経路と、複数の第1の信号経路のいずれかを第2の信号経路に置換する切り替え回路110とを備える。本発明によれば、貫通電極の全てに切り替え回路を設ける必要がなくなる。また、救済のために追加する貫通電極の数も最小限に抑えられることから、チップ面積の増大を抑制することも可能となる。

(もっと読む)

半導体装置

【課題】制御チップと複数の被制御チップが積層されたタイプの半導体装置において、コマンド信号よりも層アドレス信号を早く伝送させる。

【解決手段】互いに異なる層情報を保持する複数の被制御チップCC0〜CC7と、被制御チップCC0〜CC7に対して層アドレス信号A13〜A15及びコマンド信号ICMDを共通に供給する制御チップIFとを備える。層アドレス信号A13〜A15を構成する各ビットは、複数の第1の貫通電極のうち、被制御チップごとに並列接続された少なくとも2本の貫通電極を経由して伝送され、コマンド信号ICMDを構成する各ビットは、出力切り替え回路及び入力切り替え回路によって選択された対応する1本の貫通電極を経由して伝送される。これにより、コマンド信号ICMDよりも先に層アドレス信号A13〜A15が各被制御チップに到達する。

(もっと読む)

半導体メモリチップ及びこれを用いるマルチチップパッケージ

【課題】マルチチップパッケージのパッケージングを容易にし、半導体メモリチップとマルチチップパッケージのパッドとを接続するボンディングによって伝送される信号のローディングを一定にすることができるようにした半導体メモリチップを提供すること。

【解決手段】第1のデータ信号と第1のストローブ信号と第1のマスク信号とが入力される第1のパッド部と、第1のモードでは、前記第1のデータ信号と前記第1のストローブ信号と前記第1のマスク信号とを第1の書き込み経路回路に伝達し、交換モードでは、前記第1のデータ信号と前記第1のストローブ信号と前記第1のマスク信号とを第2の書き込み経路回路に伝達する第1の選択伝達部と、を備えることを特徴とする。

(もっと読む)

半導体装置

【課題】複数のメモリチップが積層された半導体装置においてリードライトバスの本数及び配線長を削減する。

【解決手段】積層された複数のメモリチップCC0〜CC7を備え、各メモリチップは複数のメモリバンクBank0〜Bank7と、各メモリバンクにそれぞれ割り当てられた複数のリードライトバスRWBS0〜RWBS7と、リードライトバスにそれぞれ割り当てられ当該メモリチップを貫通して設けられた複数の貫通電極TSV1とを備える。積層方向から見て互いに同じ位置に設けられた貫通電極TSV1はチップ間において共通接続される。メモリチップのそれぞれは、アクセスが要求されたことに応答して積層方向から見て互いに異なる位置に設けられたメモリバンクを同時に活性化し、これにより、平面位置の異なる貫通電極TSV1を介してデータの入出力を同時に行う。

(もっと読む)

半導体装置

【課題】積層型の半導体装置においてインターフェースチップからコアチップへのクロック信号の供給を不要とする。

【解決手段】外部から供給されるコマンド信号CMD及びクロック信号CKを受けて、各々がクロック信号CKに同期し、且つ、互いにタイミングが異なる複数のリード制御信号R1,R2を出力するリードタイミング制御回路100を有するインターフェースチップIFと、インターフェースチップIFに積層され、コマンド信号CMDが示す動作をリード制御信号R1,R2に同期してそれぞれ実行する複数の内部回路を有するコアチップCC0〜CC7とを備える。本発明によれば、コアチップに内でのレイテンシ制御が不要となることから、コアチップにクロック信号を供給する必要がなくなる。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】有機基板の使用量を抑えて、製造コストの抑制を図ることのできる半導体記憶装置を提供すること。

【解決手段】半導体記憶装置10は、一方の面に外部接続端子が設けられ、外部接続端子が設けられる領域と略同じ平面形状に個片化された有機基板11と、有機基板11に対して相対的に位置決めされた載置領域21を有するリードフレーム13と、載置領域21に接着された半導体メモリチップ15と、を備えることを特徴とする。

(もっと読む)

半導体記憶装置

【課題】樹脂モールド部を外部に露出させて、部品点数の削減や製造コストの削減を図ることのできる半導体記憶装置を提供すること。

【解決手段】実施の形態の半導体記憶装置10は、半導体メモリチップ15を樹脂モールド部18でモールドした半導体記憶装置であって、樹脂モールド部にモールドされて半導体メモリチップが載置されるプレート21と、半導体記憶装置の外周面に露出される外部接続端子19と、を備え、プレートは、樹脂モールド部の外周面に露出する複数の露出部21bを有し、複数の露出部同士は、樹脂モールド部の内部で互いに電気的に絶縁される。

(もっと読む)

半導体記憶装置

【課題】メモリセルから正確にデータを読み出すことができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、第1ワード線1と、ビット線2と、抵抗変化材4とを備える。ビット線2は第1の面が第1ワード線1と対向するように第1ワード線1と交差する。抵抗変化材4は第1ワード線1とビット線2との各交差部に配置される。また半導体記憶装置は、第2ワード線3と、絶縁膜5とを備える。第2ワード線3はビット線2の第1の面とは反対側の第2の面と対向するようにビット線2と交差する。絶縁膜5は第2ワード線3とビット線2との各交差部に配置される。1つの第1ワード線1と1つの第2ワード線3とは、ビット線2を挟み込むように配置される。第2ワード線3、ビット線2、及び絶縁膜5は、各交差部において電界効果トランジスタを構成する。電界効果トランジスタと抵抗変化材4とにより1つのメモリセルが構成される。

(もっと読む)

半導体装置及びその製造方法

【課題】貫通電極の基板からの抜け落ちを防止する。

【解決手段】半導体装置は、基板80と、基板80に設けられた1又は複数のビアホール91と、1又は複数のビアホール91内にそれぞれ設けられた貫通電極TSVとをそれぞれ有する複数のコアチップと、貫通電極TSVを通じて各コアチップと電気的に接続するインターフェースチップとを備え、ビアホール91は、両端部の径r1,r3に比べて中央部r2の径が大きいボーイング形状部分91aを有する。

(もっと読む)

積層型半導体装置

【課題】積層された複数の半導体チップ間で貫通電極切替情報を共有する。

【解決手段】複数の半導体チップ間でデータ転送を行うための複数の貫通電極を互いに共有した積層型半導体装置であって、複数の半導体チップに含まれる第1の半導体チップIFは、複数の貫通電極のうちデータ転送を行う貫通電極を指定する貫通電極切替情報SWを保持し、複数の半導体チップに含まれる第2の半導体チップCC0〜CC7に貫通電極切替情報SWを転送する。本発明によれば、貫通電極切替情報SWが第1の半導体チップIFから第2の半導体チップCC0〜CC7に転送されることから、第2の半導体チップには貫通電極切替情報SWを不揮発的に記憶する回路を設ける必要がない。これにより、第2の半導体チップのチップ面積を縮小することが可能となる。

(もっと読む)

半導体装置

【課題】センスアンプ接地電位の変動で発生するノイズによる誤動作を防いだ半導体装置を提供する。

【解決手段】センスアンプに接地電位を供給するための電極パッドであるセンスアンプ接地電位用パッドと、センスアンプ接地電位用パッドに接続された第1の導電線と、パッド列に含まれる複数の電極パッドのうち、センスアンプ接地電位用パッドとの距離が最も近い電極パッドに接続された第2の導電線と、を有し、第2の導電線がパッド列を基準にして第1の導電線とは反対側に延びている構成である。

(もっと読む)

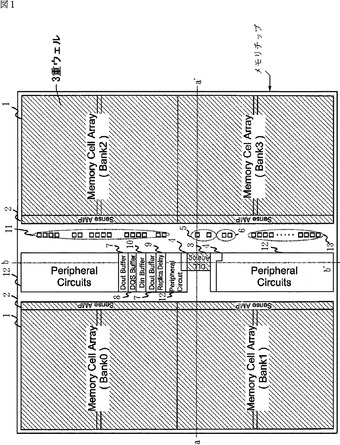

ダイナミック型半導体記憶装置

【課題】安定したクロック発生動作、高精度で低消費電力を実現しDLLを備える。

【解決手段】内部クロック信号を生成するDLL回路、内部クロック信号で動作を制御される周辺回路とメモリセルアレイを含む。第1電源電圧を供給するために同期回路に接続された第1電源パッド、第1電源電圧より低い第2電源電圧を供給するために同期回路に接続された第2電源パッド、周辺回路とメモリセルアレイに第3電源電圧を供給するための第3電源パッド、周辺回路とメモリバンクに第3電源電圧より低い第4電源電圧を供給する第4電源パッドを含む。複数のメモリセルアレイは第1領域と第2領域に分割して配置される。複数の周辺回路は第1領域と第2領域の間の第3領域に配置される。第1、2、3,4電源パッドは第1領域と前記第3領域の間の第4領域に配置されている。

【選択図】図1  (もっと読む)

(もっと読む)

メモリモジュール

【課題】制御チップの裏面側に搭載されたメモリチップにて生じる信号の反射の影響を低減する。

【解決手段】モジュール基板10を介してメモリバッファMBと対向する位置に配置されたメモリチップMC1と、モジュール基板10を介してメモリバッファMBと対向しない位置に配置されたメモリチップMC3と、モジュール基板10を介してメモリチップMC3と対向する位置に配置されたメモリチップMC11とを備え、メモリチップMC1に接続される配線部分A101とメモリチップMC3,11に接続される配線部分A103とが分岐する分岐点B100が、メモリバッファMBの平面的な搭載位置とメモリチップMC3,11の平面的な搭載位置との中間線Cから見てメモリバッファMB側に位置している。これにより、配線部分A101の配線長を十分に短くすることができる。

(もっと読む)

半導体記憶装置

【課題】貫通ビアによって共通接続された積層メモリチップのメモリチップを別々に動作させる。

【解決手段】制御パッド12に入力される信号は、それぞれメモリチップ2が有するRSTバッファ25、CEバッファ26、WEバッファ27、REバッファ28、CLEバッファ29、及びALEバッファ30に出力される。チップアドレス比較器24は、ヒューズ23に記憶された自己のチップアドレスINTCAiとアドレスバッファ17から入力されたチップアドレスEXTCAiとを比較し、一致するか否かをアドレスフラグ信号CAFLGとしてCEバッファ26に出力するよう構成されている。アドレスフラグ信号CAFLGが“H”の状態において、CEバッファ26からチップイネーブル信号CE’が出力され、メモリチップ2への書き込みや読み出しなどの動作が行われる。

(もっと読む)

半導体集積回路装置

【課題】 パッケージの端子数の増加と、ベースチップのI/O領域の増加を抑制すること。

【解決手段】 マスクROM領域と内部バス(13)とを有する半導体集積回路基板(10)と、この半導体集積回路基板上に積層され、複数のROM接続端子(15−1,15−2)を持つプログラマブルROM(15)とを備えた半導体集積回路装置(20)において、内部バスに接続された複数のバス接続端子(132−1,134−1)と複数のROM接続端子とがそれぞれ電気的に接続されている。複数のバス接続端子は、半導体集積回路基板の外周に設けられて良いし、マスクROM領域上に設けられても良いし、内部バス上に設けられても良い。この場合、複数のROM接続端子と複数のバス接続端子とはワイヤボンディングによって電気的に接続される。

(もっと読む)

ダイナミックランダムアクセスメモリおよび半導体記憶装置

【課題】アスペクト比が1:2のパッケージに高い有効比率で収容できる22N+1ビットの半導体記憶装置を提供する。

【解決手段】アスペクト比が1:2の半導体基板2の主表面を3行3列の9個の領域に等分割し、中央領域以外の各領域にアスペクト比が1:2で22N−2ビットのサブアレイ部3を配置する。中央領域には制御回路4およびパッド5群を設ける。アスペクト比が1:2のメモリチップを形成することができ、従来と同様のアスペクト比が1:2のパッケージに高い有効比率で収容できる。

(もっと読む)

半導体装置及びメモリ回路システム

【課題】低消費電力で且つデータを高速に伝達可能な半導体装置及びメモリ回路システムを提供すること。

【解決手段】同一のパッケージ内に複数の半導体チップ3−0〜3−3を備えた半導体装置1であって、複数の前記半導体チップ3−0〜3−3と、前記パッケージ内に設けられた前記半導体チップ3−0〜3−3の数を記憶する記憶装置26とを具備し、前記半導体チップ3−0〜3−3の各々は、データを記憶するメモリセルを有するメモリセルアレイ10と、前記メモリセルアレイ10から読み出されたデータを前記半導体チップ3−0〜3−3の外部へ出力する出力バッファ24と、前記記憶装置26に記憶された前記半導体チップ3−0〜3−3の数に応じて、前記出力バッファ24の駆動力を制御する制御回路25とを備える。

(もっと読む)

半導体装置

【課題】生産性が良く、安価な半導体装置を提供すること。

【解決手段】本発明の半導体装置において、半導体記憶素子5がガラス基板1に取り付けられると共に、半導体記憶素子5の電極7がガラス基板1に設けられた配線パターン2に接続されるため、従来に比して部品点数が少なくなって、生産性が良く、安価なものが得られる。

(もっと読む)

半導体装置及びその製造方法

【課題】小型化・高集積化された超薄型のFeRAMの半導体チップについて、強誘電体キャパシタの特性劣化を抑止した、薄型パッケージ構造およびその製造方法を提供する。

【解決手段】フィラー含有率が90重量%〜93重量%の範囲内の値とされた封止樹脂115を用いて半導体チップ111をモールディングし、パッケージ構造を作製する。

(もっと読む)

メモリモジュールおよびその製造方法

【課題】 薄片化したチップの機械的強度を向上させたメモリモジュールを提供する。

【解決手段】 情報を格納するためのメモリコアチップ10a〜10dと、データの入出力を制御するインターフェースチップ30と、外部との間でデータを送受信するインターポーザチップ40と、インターポーザチップの最近傍に設けられた外部接続用端子46とを有するメモリモジュールにおいて、インターフェースチップ30の最近傍に放熱板20が設けられ、インターポーザチップ40は、メモリコアチップと同質の半導体材料を基板とし、一方の面に外部接続用端子を保持するためのランド41、外部用接続端子に接続された配線44、および配線を絶縁するための絶縁膜が一体形成されている構成である。

(もっと読む)

1 - 20 / 23

[ Back to top ]