Fターム[5F101BA15]の内容

不揮発性半導体メモリ (42,765) | 電荷蓄積機構 (9,664) | FG型 (6,485) | FG形状構造 (858) | FGの突起 (84)

Fターム[5F101BA15]に分類される特許

1 - 20 / 84

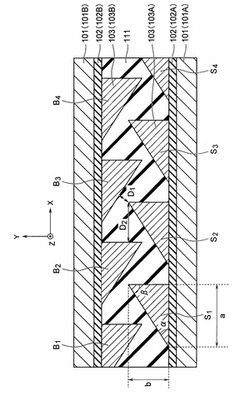

メモリ用シフトレジスタ及びその製造方法

【課題】大容量で、信頼性が高く、少ない工程数で製造可能なメモリ用シフトレジスタを提供する。

【解決手段】一の実施形態によれば、メモリ用シフトレジスタは、基板の主面に平行な第1方向に延び、前記第1方向に垂直な第2方向に向かい合う第1及び第2の制御電極を備える。さらに、前記レジスタは、前記第1及び第2の制御電極間において、前記第1の制御電極側に一列に設けられた複数の第1の浮遊電極を備える。さらに、前記レジスタは、前記第1及び第2の制御電極間において、前記第2の制御電極側に一列に設けられた複数の第2の浮遊電極を備える。さらに、前記第1及び第2の浮遊電極の各々は、前記第1方向に垂直な平面に対し、鏡面非対称な平面形状を有する。

(もっと読む)

ダイオードストラッピングを備えた熱アシストフラッシュメモリ

【課題】フラッシュメモリの動作速度及び耐久性を向上させる技術の提供。

【解決手段】メモリが、行及び列を含むメモリセルのアレイを有している。該メモリは、アレイ内の単数又は複数のワード線上の第1の離隔位置のセットに第1のバイアス電圧を印加するとともに、単数又は複数のワード線上の第2の離隔位置のセットに第1のバイアス電圧とは異なる第2のバイアス電圧を印加する、ワード線に結合された回路部を有し、第1の離隔位置のセットにおける位置は、第2の離隔位置のセットの位置の間に介在しており、それにより、第1の離隔位置のセットにおける位置と第2の離隔位置のセットにおける位置との間に、単数又は複数のワード線の加熱をもたらす電流の流れが誘導される。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を提供する。

【解決手段】フローティングゲート電極は、高い不純物濃度領域と低い不純物濃度領域とからなり、高い不純物濃度領域は、コントロールゲート絶縁膜と接する部分に配置し、低い不純物濃度領域はトンネル絶縁膜と接する領域に配置し、フローティングゲート電極のコントロールゲート絶縁膜と接する表面部分には微細凹凸を形成した。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】対向する二つの記憶素子のコントロールゲートのゲート長に起因する記憶素子の特性のばらつきを抑制する。

【解決手段】上記の課題を解決するために、不揮発性半導体記憶装置(1)を以下のように構成する。第1不揮発性メモリセル(1a)は、第1チャネル領域(11a)と、第1フローティングゲート(5a)と、第1コントロールゲート(6a)とを含むものとする。また、第2不揮発性メモリセル(1b)は、第2チャネル領域(11b)と、第2フローティングゲート(5b)と、第2コントロールゲート(6b)とを含むものとする。ここにおいて、第1チャネル領域(11a)は、第1フローティングゲート側チャネル領域(13a)と、第1コントロールゲート側チャネル領域(12a)とを備え、第1コントロールゲート側チャネル領域(12a)は不純物濃度が濃い高濃度ポケット領域(10)を備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】ゲート電極間絶縁膜のリーク電流を抑制し、電気的信頼性を向上した不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板上に行列状に形成された複数のメモリ素子と、同一列方向のメモリ素子に選択的に接続される複数のビット線と、同一行方向のメモリ素子に接続される複数のワード線とを具備し、各メモリ素子は、半導体基板上に順次形成された第1のゲート絶縁膜、電荷蓄積層、第2のゲート絶縁膜、制御電極と、電荷蓄積層の対向する側面に沿って、前記シリコン基板上面に形成された1対の不純物注入層とを具備し、ビット線に垂直な方向に沿った断面における電荷蓄積層の上部コーナー部が曲面を有し、上部コーナー部が前記第1のゲート絶縁膜の上方にある。

(もっと読む)

不揮発性半導体記憶装置

【課題】微細化された不揮発性半導体記憶装置で、隣接セル間の寄生容量によるセル間干渉とトランジスタ特性の劣化を従来に比して抑制する。

【解決手段】チャネル半導体上にゲート誘電体膜21、フローティングゲート電極22、トンネル誘電体膜23および制御ゲート電極24が順に積層され、フローティングゲート電極22と制御ゲート電極24は、トンネル誘電体膜23側に曲率を有する尖端部25,26を有する。また、トンネル誘電体膜23のキャパシタンスがゲート誘電体膜21のキャパシタンスと同等以下となるようにトンネル誘電体膜23とゲート誘電体膜21の厚さが調整される。さらに、制御ゲート電極24の尖端部26からフローティングゲート電極22に電子を注入する処理と、フローティングゲート電極22の尖端部26から制御ゲート電極24に電子を抜き取る処理とを、チャネル半導体と制御ゲート電極24との間に印加される電圧によって制御する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】従来の半導体記憶装置では、十分に半導体チップの面積を削減することができない問題があった。

【解決手段】本発明の半導体記憶装置は、半導体基板の平坦部に形成されたドレイン領域13と、半導体基板に形成された凸部の上端部に形成されたソース領域10と、ドレイン領域13の一部と重なる領域であって、かつ、平坦部の上層に形成されるコントロールゲート12と、コントロールゲート12と隣り合った領域であって、平坦部、凸部の壁面及びソース領域10の一部を覆う領域に形成されるフローティングゲート11と、を有する。

(もっと読む)

周期的な酸化およびエッチングのための装置と方法

メモリ装置

【課題】シリアル・インターフェース方式のメモリ装置において、回路規模の増加を抑えつつ、データの読み出しを高速化する。

【解決手段】EEPROM100は、データを格納するメモリセルアレイ10と、クロックに同期してシリアル入力されるアドレス信号に応じて、メモリセルアレイ10のアドレスを選択するロウアドレスデコーダ11及びカラムアドレスデコーダ12と、データの各ビットに対応して1個ずつ設けられたセンスアンプSA0〜SA5,SA_M0,SA_M1と、これらのセンスアンプから読み出されたデータをクロックに同期して先頭ビットから順にシリアル出力するシフトレジスタ15とを備える。カラムアドレスデコーダ12は、カラムアドレス信号の全ビットが確定する前に先頭ビットの2個の候補データを2個のセンスアンプSA_M0,SA_M1にそれぞれ入力することにより2個の候補データの読み出しを開始する。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリセルアレイ端部の耐圧を向上させる。

【解決手段】不揮発性半導体記憶装置10は、メモリセルトランジスタが配置される第1の領域と、メモリセルトランジスタに電気的に接続されたワード線を引き出す電極21が配置される第2の領域と、周辺トランジスタが配置される第3の領域とを有する。第1の領域には、第1の幅を有する複数の第1のアクティブ領域AA1が設けられ、第2及び第3の領域にはそれぞれ、第1の幅より広い第2の幅を有する複数の第2及び第3のアクティブ領域AA3,AA5が設けられる。第2の領域の素子分離層23Bの上面は、第1の領域の素子分離層23Aの上面より高く、第2の領域の電荷蓄積層32Bは、上部の角の曲率半径が、第3の領域の電荷蓄積層43よりも大きい。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】N+型ソース層とフローティングゲートとのカップリング比を高くしてプログラム特性を改善すると共にメモリーセルの面積の縮小化を図る。

【解決手段】N+型ソース層4の両側にトレンチ3を形成する。トレンチ3の側壁は2つの素子分離層STI2の端面と平行なトレンチ側壁2a、トレンチ側壁2bと、STI2に垂直な面からなるトレンチ側壁3a、及びトレンチ側壁3aと平行でないトレンチ側壁3bから構成される。かかる構成のトレンチ3の上部からトレンチ側壁3aに平行で、且つP型ウエル層1に垂直又は角度をもった砒素イオン等のイオン注入を行い、トレンチ3底面からトレンチ側壁3bに延在するフローティングゲートFG6と広い面積で対峙するN+型ソース層4を形成する。

(もっと読む)

スプリットゲート型不揮発性半導体記憶装置の製造方法、及びスプリットゲート型不揮発性半導体記憶装置

【課題】スプリットゲート型不揮発性記憶装置に製造における工程数を削減する。

【解決手段】基板(2)と、ゲート絶縁膜(7)を介して基板(2)の上に形成されたフローティングゲート(5)と、トンネル絶縁膜(8)を介してフローティングゲート(5)の隣に形成されたコントロールゲート(6)と、コントロールゲート(6)側の基板(2)に形成された第1ソース/ドレイン拡散層(4)と、フローティングゲート(5)側の基板(2)に形成された第2ソース/ドレイン拡散層(3)と、第1ソース/ドレイン拡散層(4)と第2ソース/ドレイン拡散層(3)との間の基板に設けられるチャネル領域と、第2ソース/ドレイン拡散層(3)に接触しているシリサイド(21)とを具備するスプリットゲート型不揮発性半導体記憶装置を構成する。

(もっと読む)

半導体記憶装置及び半導体記憶装置の製造方法

【課題】フローティングゲートとコントロールゲートとのオーバーラップ量のバラツキを抑制する。

【解決手段】基板(1)と、ゲート絶縁膜(2)を介してその基板(1)の上に設けたれたフローティングゲート(20)と、トンネル絶縁膜(30)を介してそのフローティングゲート(20)の隣に設けられたコントロールゲート(50)と、そのフローティングゲート(20)の上に設けられたスペーサー絶縁膜(9)と、そのスペーサー絶縁膜(9)とそのコントロールゲート(50)との間に設けられた保護膜(7)とを具備する半導体記憶装置(MC)を構成する。そのような半導体記憶装置(MC)において、その保護膜(7)は、スペーサー絶縁膜(9)以外の部分をエッチングするときに、スペーサー絶縁膜(9)の側面のストッパーとして機能している。

(もっと読む)

不揮発性半導体記憶装置

【課題】デポジッション膜を形成することなく、ゲートとコンタクトのショートを抑制する不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置1のコントロールゲート14を、フローティングゲート13側に位置する第1側面と、第1側面の反対に位置する第2側面と、コントロールゲート14の第1側面側の上部に形成されたシリサイド領域22と、コントロールゲート14の第2側面側の上部に形成された突出部8とを含むように構成する。そのサイドウォール絶縁膜21は、シリサイド領域22を覆うことなく突出部8の少なくとも一部を被覆する第1部分と、第1部分から連続的に設けられ、第2側面に接触して第2側面を被覆する第2部分とを含むものとする。

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜界面の汚染を防止し、半導体基板とコントロールゲートの間の絶縁膜の破壊を抑制する。

【解決手段】半導体装置の製造方法は、半導体基板2の第1表面領域C1上にゲート絶縁膜4を介してフローティングゲート5を形成する工程と;第1表面領域C1に隣接する第2表面領域C2及びフローティングゲート5の端部を覆うようにトンネル絶縁膜8aを形成する工程と;トンネル絶縁膜8aを覆い、第2表面領域C2の上方が厚く、フローティングゲート5の上方が薄くなるように第1酸化膜33を形成する工程と;第1酸化膜33とフローティングゲート5上のトンネル絶縁膜8aの表面とをエッチバックする工程と;第2表面領域C2上の第トンネル絶縁膜8a上にコントロールゲート9を形成する工程とを具備する。

(もっと読む)

NAND型フラッシュメモリ

【課題】メモリセルのしきい値電圧の分布幅の拡大を抑制することが可能なNAND型フラッシュメモリを提供する。

【解決手段】NAND型フラッシュメモリは、第1の絶縁膜、電荷保持層、第2の絶縁膜、および、制御ゲートを含み、電荷保持層に保持された電荷量に応じた情報を記憶するメモリセルが直列に複数接続されたNANDストリングと、制御ゲートおよび半導体ウェルに印加する電圧を制御する制御回路とを備え、書き込み動作後、選択メモリセルにデータが書き込まれたか否かを検証するベリファイリード動作を行う前に、制御回路は、選択メモリセルの制御ゲートに、半導体ウェルの電位と同電位または書き込み電圧と同極性である第1の電圧を印加し、書き込み対象ではない非選択メモリセルの制御ゲートには、書き込み電圧と同極性であり第1の電圧よりも絶対値として大きい第2の電圧を印加するデトラップ動作を行う。

(もっと読む)

電気光学装置、電気光学装置の製造方法、電子機器

【課題】不揮発性メモリと画素TFTとを同一基板上に形成でき、且つ両者を良好に動作させることが可能な電気光学装置を提供する。

【解決手段】画素TFTのゲート絶縁膜18を不揮発性メモリのトンネル絶縁膜(第1の絶縁膜)35と、トンネル絶縁膜35よりも膜厚の大きい第2の絶縁膜37によって構成する。また、フローティングゲート電極36のコントロールゲート電極60側の面を凹凸とし、該凹凸によってフローティングゲート電極36の表面積を拡げる。これにより、フローティングゲート電極36とコントロールゲート電極60との間の容量を、フローティングゲート電極36と半導体層33との間の容量よりも大きくする。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】カップリング比を減少させずにゲート電極と不純物拡散領域との位置が整合して形成される不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】半導体基板と、前記半導体基板に形成される複数の不純物拡散領域と、前記半導体基板上に形成される絶縁膜と、隣り合う前記不純物拡散領域を繋ぐように前記半導体基板上に前記絶縁膜を介して形成されるフローティングゲート電極と、前記フローティングゲートの上面及び側面に形成されるゲート間絶縁膜と、前記ゲート間絶縁膜を介して前記フローティングゲート電極の上面及び両側面と接するように形成されるコントロールゲート電極とを備える。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】メモリセルを微細化してもコントロールゲートとフローティングゲートとの結合容量を増大さることができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板上に設けられたトンネル絶縁膜103と、トンネル絶縁膜上に形成され、複数のメモリセルのそれぞれに対応して設けられたフローティングゲートFG1、FG2と、フローティングゲート上に設けられたゲート絶縁膜104と、ゲート絶縁膜上に設けられたコントロールゲートCGとを備え、或る単一のメモリセルMCに対応して設けられたフローティングゲートは、第1のゲート部分FG1と第2のゲート部分FG2とを有し、該メモリセル内において第1のゲート部分と第2のゲート部分との間にトンネル絶縁膜とゲート絶縁膜とが接触する部分を有している。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】高いカップリング比を有するセルトランジスタを備えた不揮発性半導体記憶装置およびその製造方を提供する。

【解決手段】半導体基板11の第1領域11aにおいて、第1ゲート電極15の上面15bおよび第1絶縁分離層12の側面12aを露出させる工程と、第1絶縁分離層12の側面12aに第1側壁膜35aを形成する工程と、第1側壁膜35aをマスクとして、第1ゲート電極15の上部をエッチングし、第1ゲート電極15の上部に第1凹部15aを形成する工程と、第1ゲート電極15の上部を露出させる工程と、第1ゲート電極15の上部を含む第1絶縁分離層12上にコンフォーマルに第2ゲート絶縁膜16を形成する工程と、第1凹部15aを埋め込むように、第2ゲート絶縁膜16上に第2ゲート電極材料膜を形成する工程と、を具備する。

(もっと読む)

1 - 20 / 84

[ Back to top ]