Fターム[5F101BA19]の内容

不揮発性半導体メモリ (42,765) | 電荷蓄積機構 (9,664) | FG型 (6,485) | FG材料(多結晶シリコンを除く) (223)

Fターム[5F101BA19]に分類される特許

141 - 160 / 223

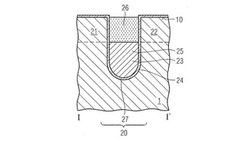

トランジスタ、集積回路および集積回路形成方法

【課題】トランジスタ、集積回路、および、集積回路形成方法を提供する。

【解決手段】半導体基板1内に形成されたゲート溝27内にゲート誘電体24を介してゲート電極23が配置された構成を有する。該ゲート電極23は、導電性炭素材を有している。

(もっと読む)

半導体装置の作製方法

【課題】高速動作が可能で駆動電圧の低い半導体素子を有する低消費電力な半導体装置を、複雑な工程を経ることなく作製することを目的とする。

【解決手段】半導体層の局所的に薄膜化された領域を、加熱処理により周辺の半導体層を溶融し、その溶融した半導体材料を流動させることによって形成する。薄膜化領域に開口を有する島状の半導体層を形成し、開口周辺の半導体層端部をレーザ光により局所的に加熱することによって溶融し、溶融した半導体材料を開口に流動させ開口を充填する。流動した半導体材料によって開口は埋められ、固化することによって膜厚の薄い半導体層領域となる。従って半導体層は局所的に薄膜化領域を有する連続した半導体層となる。

(もっと読む)

半導体装置の作製方法

【課題】大面積基板に、高性能な半導体素子、及び集積回路を高スループットで生産性よく作製することを目的とする。

【解決手段】単結晶半導体基板(ボンドウエハー)より単結晶半導体膜を転置する際、単結晶半導体基板を選択的にエッチング(溝加工ともいう)し、作製する半導体素子の大きさに複数に分割された複数の単結晶半導体層を、異種基板(ベース基板)に転置する。従って、ベース基板には、複数の島状の単結晶半導体層(SOI層)を形成することができる。

(もっと読む)

不揮発性半導体記憶装置

【課題】シリサイド領域を形成し、かつ、チャネル形成領域の金属元素濃度増大を防ぎ、記憶素子の信頼性を向上させることを課題とする。

【解決手段】ソース領域及びドレイン領域と、該ソース領域及びドレイン領域の間に設けられたチャネル形成領域を有する半導体層と、前記半導体層上に、第1の絶縁層、第1のゲート電極、第2の絶縁層、第2のゲート電極が順次重ね合わせて設けられ、前記ソース領域及びドレイン領域は、その一部又は全てがニッケルシリサイド層で形成され、前記第1のゲート電極は、絶縁膜で周囲が覆われていると共に、希ガス元素を含む不揮発性半導体記憶装置に関する。

(もっと読む)

不揮発性メモリ素子の製造方法

【課題】セルの書き込みしきい値電圧の分布を均一にできる不揮発性メモリ素子の製造方法を提供すること。

【解決手段】ゲート導電膜202、ゲート絶縁膜201、及び基板200の一部をエッチングしてトレンチを形成し、該トレンチを埋め込むように素子分離膜を形成する段階と、所定の深さに素子分離膜を後退させる段階と、後退した素子分離膜203Aによって形成される段差に沿って、バッファ膜204Aを形成する段階と、バッファ膜の内側壁に、バッファ膜に対して高いエッチング選択比を有する物質でスペーサスペーサ205Aを形成する段階と、スペーサを用いて、後退した素子分離膜203Aの一部をエッチングし、素子分離膜203A内に溝を形成する段階と、スペーサ205A及びバッファ膜204Aを除去し、バッファ膜204Aが除去された基板200上の段差に沿って誘電体膜を形成し、誘電体膜上にコントロールゲートを形成する段階とを含む。

(もっと読む)

不揮発性メモリ素子の製造方法

【課題】ウエハ全域において、EFH(Effective Field oxide Height)の不均一性を最小化し、しきい値電圧均一性を確保可能な不揮発性メモリ素子の製造方法を提供すること。

【解決手段】基板200上に、ゲート絶縁膜201、第1ゲート導電膜202、第1犠牲膜204及び第2犠牲膜206を形成するステップと、第1犠牲膜及び第2犠牲膜、第1ゲート導電膜、ゲート絶縁膜、及び基板をエッチングし、トレンチを形成するステップと、トレンチが埋め込まれるように、第1絶縁膜を形成するステップと、第2犠牲膜を停止膜として第1絶縁膜を研磨するステップと、第2犠牲膜を除去するステップと、第1絶縁膜をトレンチの内部で一定の深さに後退させるステップと、トレンチ内の空間が埋め込まれるように、第2絶縁膜を形成するステップと、第1犠牲膜を研磨停止膜として第2絶縁膜を研磨するステップとを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】トンネル絶縁膜とフローティングゲート電極との間の楔状酸化膜の形成を抑制することが可能な半導体装置を提供する。

【解決手段】半導体基板10と、半導体基板上に形成されたトンネル絶縁膜20と、トンネル絶縁膜上に形成された下層半導体膜31と、不純物元素を含有した上層半導体膜33と、下層半導体膜と上層半導体膜との間に形成され且つ上層半導体膜に含有された不純物元素の下層半導体膜への拡散を抑制するバリア絶縁膜32とを含むフローティングゲート電極30と、フローティングゲート電極上に形成された電極間絶縁膜40と、電極間絶縁膜上に形成されたコントロールゲート電極50とを備える。

(もっと読む)

不揮発性メモリ素子及びその製造方法

【課題】高集積化が容易で、且つ高い信頼性を有する不揮発性メモリ素子及びその製造方法を提供する。

【解決手段】本発明の不揮発性メモリ素子は、複数の第1半導体層、複数の第2半導体層、複数の第1ストレージノード、及び複数の第1制御ゲート電極を備える。複数の第1半導体層は、基板上に積層され、複数の第2半導体層は、複数の第1半導体層の間にそれぞれ介在して複数の第1半導体層の間に複数の第1トレンチを限定するように複数の第1半導体層の一端からリセスされ、複数の第1ストレージノードは、複数の第1トレンチの内部の第2半導体層の表面上に提供され、複数の第1制御ゲート電極は、複数の第1トレンチを満たすように複数の第1ストレージノード上に形成される。

(もっと読む)

ニューロンMOSトランジスタ及びその製造方法

【課題】微細化が容易で、電流駆動力が大きなニューロン素子を提供する。

【解決手段】基板2に板状の第1導電型の半導体層と、半導体層の長手方向に離間するように設けられた第2導電型のソース・ドレイン領域と、半導体層の上面に設けられた保護膜8と、ソース領域とドレイン領域との間に形成されるチャネル領域6aと、チャネル領域6aの両側面に設けられた一対のゲート絶縁膜10と、チャネル領域6aの両側面のゲート絶縁膜10を挟み上面に保護膜8を挟む第1部分12aと、第1部分12aから延在する第2部分12bと、第1および第2部分12a,12bよりも幅の広い第3部分12cと、を有する浮遊ゲート電極12と、浮遊ゲート電極12の上に設けられた電極間絶縁膜14と、浮遊ゲート電極12の第3部分12c上に電極間絶縁膜を挟むように設けられた複数の制御ゲート電極161、162と、を備える。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】作製工程が簡略化され、容量素子の面積が縮小化されたメモリ素子を有する半導体装置を提供することを課題とする。

【解決手段】基板上に第1の半導体膜と、第2の半導体膜を形成し、第1の半導体膜及び第2の半導体膜を覆って第1の絶縁膜を形成し、第1の半導体膜及び第2の半導体膜上に、第1の絶縁膜を介してそれぞれ第1の導電膜及び第2の導電膜を形成し、第1の導電膜を覆って第2の絶縁膜を形成し、第1の半導体膜上に設けられた第1の導電膜上に第2の絶縁膜を介して第3の導電膜を選択的に形成し、第1の半導体膜に第3の導電膜をマスクとして不純物元素を導入し、第2の半導体膜に第2の導電膜を通して不純物元素を導入する。

(もっと読む)

半導体装置

【課題】一方は高速動作が可能で駆動電圧の低い薄膜トランジスタ、他方は電圧に対して高耐圧で信頼性の高い薄膜トランジスタの両方を有する半導体装置を提供することを目的とする。従って、低消費電力かつ高信頼性を付与された半導体装置を提供することを目的とする。

【解決手段】絶縁表面を有する同一基板上に半導体層の膜厚の異なる複数種の薄膜トランジスタを有する。高速動作を求められる薄膜トランジスタの半導体層のチャネル形成領域を、電圧に対して高い耐圧性を求められる薄膜トランジスタの半導体層のチャネル形成領域より薄膜化し、チャネル形成領域の膜厚を薄くする。また、ゲート絶縁層においても、高速動作を求められる薄膜トランジスタは、電圧に対して高い耐圧性を求められる薄膜トランジスタより膜厚が薄くてもよい。

(もっと読む)

非揮発性メモリセルおよびその製造方法

【課題】本発明は、非揮発性メモリセル、および、その製造方法に提供することを目的とする。具体的に、本発明は、単位セルが動作する際に隣接したセルへの影響を最小にすることができる非揮発性メモリおよびその製造方法を提供することを目的とする。

【解決手段】本発明の一実施例に係る非揮発性メモリセルは、基板と、前記基板の活性領域上に形成された第1の酸化膜と、前記活性領域内に形成されたソースおよびドレインと、前記第1の酸化膜上に形成された電荷蓄積部と、前記電荷蓄積部を囲む、前記第1の酸化膜上に形成された第2の酸化膜と、前記第2の酸化膜を囲んで形成されたゲートと、を有している。

(もっと読む)

半導体装置及びその作製方法

【課題】動作特性及び信頼性の向上した新規な構造の半導体装置及びその作製方法を提供する。

【解決手段】基板上に設けられ、一対の不純物領域の間に設けられたチャネル形成領域を含む島状の半導体層と、半導体層の側面に接して設けられた第1絶縁層と、チャネル形成領域上に設けられ、半導体層を横断するように設けられたゲート電極と、チャネル形成領域及びゲート電極の間に設けられた第2絶縁層と、を有する。半導体層は局所的に薄膜化され、薄膜化された領域にチャネル形成領域が設けられており、第2絶縁層は、少なくともゲート電極が重畳する領域の半導体層の側面に設けられた第1絶縁層を覆う。

(もっと読む)

半導体装置

【課題】一方は高速動作が可能で駆動電圧の低い薄膜トランジスタ、他方は電圧に対して高耐圧で信頼性の高い薄膜トランジスタの両方を有する半導体装置を提供することを目的とする。従って、低消費電力かつ高信頼性を付与された半導体装置を提供することを目的とする。

【解決手段】絶縁表面を有する同一基板上に半導体層の膜厚の異なる複数種の薄膜トランジスタを有する。高速動作を求められる薄膜トランジスタの半導体層を、電圧に対して高い耐圧性を求められる薄膜トランジスタの半導体層より薄膜化し、半導体層の膜厚を薄くする。また、ゲート絶縁層においても、高速動作を求められる薄膜トランジスタは、電圧に対して高い耐圧性を求められる薄膜トランジスタより膜厚が薄くてもよい。

(もっと読む)

半導体装置の作製方法

【課題】ゲート絶縁層の膜厚が薄くなった部分、すなわち段差部による半導体素子特性への影響を低減し、半導体素子の信頼性を向上させることを目的とする。

【解決手段】絶縁表面上に半導体層を形成し、半導体層の端部をウェット酸化して第1の絶縁層を形成し、半導体層上および第1の絶縁層上に第2の絶縁層を形成し、第2の絶縁層を介して、半導体層上および第1の絶縁層上にゲート電極を形成する。

(もっと読む)

半導体素子の製造方法

【課題】ゲート酸化膜やトンネル酸化膜に作用するストレスを最小化することで素子の電気特性に優れたものが得られる半導体素子の製造方法を提供する。

【解決手段】半導体基板100上にワードラインやセレクトラインを形成後、層間絶縁膜122を形成する前に後続工程で発生するプラズマダメージからそうしたワードラインなどを保護するためにキャッピング膜120を形成する。その際、圧縮性キャッピング膜と伸長性キャッピング膜を少なくとも一層ずつ含んでキャッピング膜120を多層に形成する。そのようにして圧縮性ストレスと伸張性ストレスを相殺させ、ワードラインやゲート絶縁膜に作用するストレスを最小化させ、素子の電気的特性を維持し、ひいては向上させる。

(もっと読む)

不揮発性メモリ素子及びその動作方法

【課題】動作信頼性が高くて高集積化が可能である不揮発性メモリ素子及びその動作方法を提供する。

【解決手段】不揮発性メモリ素子は半導体基板110aを含み、電荷保存層120は、半導体基板上110aに提供され、例えばポリシリコン、金属、シリコン窒化膜、量子ドット、またはナノクリスタルを含むことができ、制御ゲート電極140は、電荷保存層140上に提供され、第1補助ゲート電極130aと第2補助ゲート電極130bは、電荷保存層140の一側に離隔配置され、半導体基板110aから絶縁される。この不揮発性メモリ素子によれば、メモリトランジスタ内部にソース及びドレイン領域が省略され、代わりに第1補助ゲート電極130a及び第2補助ゲート電極130bが配され、不純物ドーピングによるソース及びドレイン領域より微細線幅に形成され、従って不揮発性メモリ素子の集積度向上に寄与できる。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】書き込み特性と消去特性をともに向上させることを可能にする。

【解決手段】半導体基板2と、半導体基板に離間して形成されたソース領域4aおよびドレイン領域4bと、ソース領域とドレイン領域との間の半導体基板上に形成された第1絶縁膜8と、第1絶縁膜上に形成され伸張歪みを有する半導体導電材料層を含む浮遊電極10と、浮遊電極上に形成された第2絶縁膜12と、第2絶縁膜上に形成された制御電極14と、を備え、浮遊電極の伸張歪みは、第2絶縁膜から第1絶縁膜に向かうに従って次第に小さくなっており、第2絶縁膜との界面において0.01%以上の歪みを有し、第1絶縁膜との界面において歪みが0.01%未満である。

(もっと読む)

不揮発性半導体メモリ

【課題】ゲート間絶縁膜に発生するリーク電流の増大なく、カップリング比を向上させる。

【解決手段】本発明の例に係る不揮発性半導体メモリは、第1及び第2拡散層12,13と、第1及び第2拡散層12,13の間に形成されるチャネルと、チャネル上に形成されるゲート絶縁膜14と、ゲート絶縁膜14上に形成されるフローティングゲート電極15と、フローティングゲート電極15上に形成されるゲート間絶縁膜16と、ゲート間絶縁膜16上に形成されるコントロールゲート電極17とを備え、ゲート間絶縁膜16のチャネル長方向の端部がフローティングゲート電極15の側面又はコントロールゲート電極17の側面よりも内側に存在する。

(もっと読む)

ナノスケール浮遊ゲートおよび形成方法

半導体基板(102)の上にあるトンネル誘電体層(104)を含むメモリセル(100)が提供される。メモリセルは、トンネル誘電体層の上にある第一の部分(106)と、第一の部分からのびるナノロッドの形の第二の部分(116)とを持つ浮遊ゲートも含む。加えて、制御ゲート層(122)は、ゲート間誘電体層(120)によって浮遊ゲートから分離される。  (もっと読む)

(もっと読む)

141 - 160 / 223

[ Back to top ]