Fターム[5F101BB13]の内容

不揮発性半導体メモリ (42,765) | 制御 (5,368) | 制御装置 (5,154) | コントロールゲートなし (38) | SDとFG間容量による制御 (15)

Fターム[5F101BB13]に分類される特許

1 - 15 / 15

不揮発性半導体メモリ素子、および不揮発性半導体メモリ装置

【課題】フローティングゲートへの電荷の蓄積と消去を容易に行え、またフローティングゲートの電荷を消去する場合にメモリセルの閾値を容易に制御できる、不揮発性半導体メモリ素子を提供する。

【解決手段】フローティングゲートへの電荷の蓄積時に、フローティングゲートとドレイン(またはソース)間に電圧を印加し、バンド・バンド間によるホットエレクトロンを半導体基板中に発生させ、フローティングゲートに電荷を注入する。また、フローティングゲートの電荷の消去時には、フローティングゲートとドレイン(またはソース)間に電圧を印加し、バンド・バンド間によるホットホールを発生させ、該ホットホールにより蓄積された電荷を消去する。また、フローティングゲートの電荷の消去時には、メモリセルのコントロールゲートとソース間の閾値が所望の値になるように制御しながら、電荷を消去する。

(もっと読む)

不揮発性メモリセル及びその製造方法

【課題】 CMOS製造プロセス工程内で実装が可能で、素子面積の拡大を抑制しながらも、書き込み、読み出し、及び消去の能力を十分に発揮できる信頼性の高い不揮発性メモリセルを提供する。

【解決手段】 P型半導体基板1aと、基板1a上に分離形成された2つのN型不純物拡散領域2a,2bと、該2a,2bに挟まれる領域を少なくとも含む領域の上方に第1ゲート絶縁膜15を介して形成された第1ゲート電極13と、基板1a上に形成されるN型ウェル領域4aと、領域4a上に分離形成された2つのP型不純物拡散領域5a,5bと、該5a,5bに挟まれる領域を少なくとも含む領域の上方に第2ゲート絶縁膜14を介して形成された第2ゲート電極6と、P型不純物拡散領域5a,5bと電気的に接続された配線層9dと、を有するとともに、配線層9dが、第2ゲート電極6の形成領域を少なくとも含む領域の上方に、層間絶縁膜55を介して形成されている。

(もっと読む)

不揮発性半導体記憶装置及びその作製方法

【課題】書き込みや消去を繰り返し行った場合であっても、読み出し不良を抑制することを目的の一とする。又は、メモリトランジスタの面積の増大を抑制しつつ、書き込み電圧、消去電圧を低減することを目的の一とする。

【解決手段】基板上に設けられた書き込み動作及び消去動作に用いる第1の半導体層及び読み出し動作に用いる第2の半導体層上に、絶縁膜を介してフローティングゲートとコントロールゲートを設け、第1の半導体層を用いてフローティングゲートへの電子の注入・放出を行い、第2の半導体層を用いて読み出しを行う。

(もっと読む)

不揮発性半導体記憶装置、不揮発性メモリアレイ、および不揮発性半導体記憶装置の製造方法

【課題】不揮発性半導体記憶装置の構造を簡便化する。

【解決手段】半導体基板20の上にゲート絶縁膜30を介してポリシリコンからなるフローティングゲート40が設けられている。フローティングゲート40の両側壁には、側壁絶縁膜50が設けられている。拡散層60は、半導体基板20内に設けられ、フローティングゲート40から所定の距離だけ離間している。拡散層70は、半導体基板20内に設けられ、チャネル領域のチャネル幅方向およびチャネル長さ方向においてフローティングゲート40とオーバーラップしている。フローティングゲート40と容量カップリングした拡散層70に高電圧を印加することによりフローティングゲート40に電子が注入される。

(もっと読む)

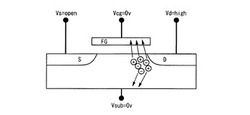

可変結合を有する不揮発性プログラマブルメモリに組み込まれた集積回路

マルチプログラマブル不揮発性デバイスは、ソース/ドレイン領域の一部分に重なるFETゲートとして機能する浮遊ゲートで動作し、ジオメトリ及び/又はバイアス条件によって可変結合を可能にする。これにより、デバイス用のプログラム供給電圧が可変容量結合によって浮遊ゲートに付与され、デバイスの状態を変更する。本発明は、データ暗号化、リファレンス調整、製造ID、セキュリティID及び他の多くのアプリケーションなどの各環境において使用できる。  (もっと読む)

(もっと読む)

不揮発性ワンタイムプログラマブル及びマルチタイムプログラマブルメモリに組み込まれた集積回路

プログラム可能な不揮発性デバイスが、ソース/ドレイン領域の一部分に重なるFETゲートとして機能する浮遊ゲートを使用する。これにより、デバイス用のプログラム供給電圧が容量結合によって浮遊ゲートに付与され、デバイスの状態を変更する。本発明は、データ暗号化、リファレンス調整、製造ID、セキュリティID及び他の多くのアプリケーションなどの各環境において使用できる。  (もっと読む)

(もっと読む)

半導体装置

【課題】浮遊ゲートをもち制御ゲートを備えていない不揮発性メモリセルを備えた半導体装置において、その不揮発性メモリセルの読出し特性を飛躍的に改善する。

【解決手段】不揮発性メモリセルは、P型半導体基板1上に形成された書込みメモリゲート酸化膜9及び書込みメモリゲート酸化膜9上に形成された電気的に浮遊状態のポリシリコンからなる書込み浮遊ゲート11をもつPMOS書込みトランジスタと、P型半導体基板1上に形成された読出しメモリゲート酸化膜15及び読出しメモリゲート酸化膜15上に形成された電気的に浮遊状態のポリシリコンからなる読出し浮遊ゲート17をもつNMOS読出しトランジスタを備えている。書込み浮遊ゲート11と読出し浮遊ゲート17は電気的に接続されている。不揮発性メモリセルへの書込みはPMOS書込みトランジスタによって行なわれ、読出しはNMOS読出しトランジスタによって行なわれる。

(もっと読む)

半導体装置の製造方法

【課題】砒素を含んだシリコン窒化膜に対して、燐酸を用いたウェットエッチングを行うと、ウェットエッチング液中に反応生成物(パーティクル)が発生し、汚染の原因になってしまう。

【解決手段】本発明の半導体装置の製造方法は、砒素が含まれている部分と砒素が含まれていない部分とを有するシリコン窒化膜を形成する工程と、ドライエッチングにより、前記シリコン窒化膜のうちの前記砒素が含まれている部分をエッチングする第1のエッチング工程と、ウェットエッチングにより、前記シリコン窒化膜のうちの前記砒素が含まれていない部分をエッチングする第2のエッチング工程と、を含む、ことを特徴とする

(もっと読む)

不揮発性メモリ製造方法

【目的】シリコン層の下側に電荷蓄積膜を有する不揮発性メモリを容易に製造する不揮発性メモリ製造方法を提供する。

【構成】複数のメモリセルが少なくとも1次元のセル配列なす不揮発性メモリを、支持基板と埋込酸化膜とシリコン層とからなるSOIウエハに形成する不揮発性メモリ製造方法であり、複数孔の孔配列パターンに従って該シリコン層及び埋込酸化膜に対して異方性エッチング処理を施して該シリコン層を貫通し該埋込酸化膜の内部に伸張する複数の貫通孔を形成し、該貫通孔を介して露出した埋込酸化膜に対して等方性エッチング処理を施して各々が該貫通孔の半径方向に広がる複数の円柱腔を形成し、該円柱腔を電荷蓄積膜で充填する。さらに、該円柱腔の所定領域内の電荷蓄積膜を素子分離膜で置換して残された電荷蓄積膜を島状に形成し、当該島状に形成された電荷蓄積膜上方のシリコン層にアクティブ領域を形成する。

(もっと読む)

半導体装置

【課題】特に、横方向および斜め方向からの光の進入を低減でき、特性の変動が抑制された半導体装置を提供する。

【解決手段】本発明の半導体装置は、半導体層10に設けられた半導体素子と、

前記半導体素子の周囲に設けられた遮光壁50と、

前記半導体素子に電気的に接続された配線層26であって、前記遮光壁50の設けられていない開孔52から該遮光壁50の外側に延伸された配線層26と、を含み、

前記配線層26は、前記開孔52に位置している第1部分26Aと、該開孔の外側に位置し該第1部分26Aと比して大きい幅を有する第2部26B分と、を含むパターンを有し、

前記第2部分26Bの幅は、前記開孔52の幅と同一以上の幅である。

(もっと読む)

EEPROMデバイスを消去する方法

本出願書は、FNトンネリング消去サイクルが自己制限的ではないという、EEPROMの消去の間に起こる問題を取り上げる。既存の方法は、監視する計算法を用いることによってこの問題に対処している。しかしながら、この計算法は、消去処理時間を遅くする。本出願書は、監視する計算法の必要性を低減する、EEPROMセルを消去するための代替方法を提供する。該方法は、FNトンネリングが消去ゲートを通して起こるように、消去ゲートの電位を引き上げて制御ゲートの電位を引き下げる最初のステップを備える。引き続くソフトプログラミングのステップは、制御ゲートの電位を十分高い値に引き上げて、FNトンネリングがトランジスタの酸化膜を通して開始するように誘導するために用いられる。本方法が特に適している新構造も開示される。  (もっと読む)

(もっと読む)

単一ゲートの不揮発性フラッシュメモリセル

【課題】その場で消去する能力を有し、従来のCMOSプロセスに適合する単一ポリのフローティングゲートメモリデバイスを提供する。

【解決手段】従来のロジックプロセスに適合する単一ポリシリコンゲートを有する不揮発性フローティングゲートメモリセルは、第1導電型の基板を備えている。第2導電型の第1及び第2領域は、基板内にあって、互いに離間されて、それらの間にチャンネル領域を画成する。第1ゲートが基板から絶縁され、チャンネル領域の第1部分の上及び第1領域の上に配置されて、それに実質的に容量性結合される。第2ゲートは、基板から絶縁され、第1ゲートから離間されると共に、第1部分とは異なるチャンネル領域の第2部分の上に配置され、第2領域にほとんど又は全く重畳しない。

(もっと読む)

集積回路装置及び電子機器

【課題】 耐圧確保のために、リード及び消去モードとプログラム時とで、メモリセルに接続されたトランスファーゲートを構成するP型及びN型MOSトランジスタの制御を変更でき、かつ、小面積化を達成できるサブワード線デコーダを搭載した集積回路装置及び電子機器を提供すること。

【解決手段】 メモリセルMCとビット線BLとの間に設けられた第1のトランスファーゲート240は、サブワード線デコーダSWDecに接続されたP型及びN型MOSトランジスタXfer(P,N)を有する。サブワード線デコーダは、第2及び第3のトランスファーゲート610,630と2つのトランジスタ600,620とを有する計6個のトランジスタから構成され、第2及び第3のトランスファーゲートの一方610のソースにカラムドライバCLDrvの出力線が接続され、第2及び第3のトランスファーゲートの他方630のソースに反転プログラム線XPGMを接続した。

(もっと読む)

不揮発性半導体記憶置

【課題】電気的消去が可能であり、メモリセルを積層構造ではない単一のゲート電極を持つMOSトランジスタで構成する。

【解決手段】ゲート電極を有するMOSトランジスタからなる選択トランジスタ11と、選択トランジスタ11のドレイン領域に接続されたビット線BLと、選択トランジスタ11のゲート電極に接続されたワード線WLと、いずれにも電気的に接続されず電位的に浮遊状態にされたゲート電極を有し、ドレイン領域が選択トランジスタ11のソース領域に接続され、選択トランジスタ11と同一極性のMOSトランジスタからなるセルトランジスタ12と、セルトランジスタ12のソース領域に接続されたソース線SLとを具備している。

(もっと読む)

半導体装置

【課題】 素子劣化が小さくデータ保持特性の良好な不揮発性メモリを提供する。

【解決手段】 相補型MISFETの製造工程に他の工程を追加することなく形成した不揮発性メモリにおいて、データの消去時には、n型ウエル5(n型半導体分離領域3)に9Vを印加し、p型半導体領域15Bに9Vを印加し、p型半導体領域15Aに−9Vを印加し、データ書き込み用および消去用のMISFETQw1およびデータ読み出し用のMISFETQr1のソース、ドレイン(n型半導体領域14B)を開放電位とし、ゲート電極7Aから電子をFNトンネル方式でp型ウエル4へ放出する。この時、容量素子C1が形成されたp型ウエル4に負の電圧を印加し、MISFETQw1、Qr1が形成されたp型ウエル4に正の電圧を印加することにより、ゲート破壊を起こさない電圧でデータ消去動作に必要な電位差を確保する。

(もっと読む)

1 - 15 / 15

[ Back to top ]