Fターム[5F101BF08]の内容

不揮発性半導体メモリ (42,765) | 動作 (2,287) | 寄生 (642) | 寄生容量 (142)

Fターム[5F101BF08]に分類される特許

121 - 140 / 142

半導体記憶装置

【課題】近接セル間干渉の影響を低減した半導体記憶装置を提供する。

【解決手段】シリコン基板4上に第一の絶縁膜5aを介して面方向に所定間隔で形成された浮遊ゲート6a層と、当該浮遊ゲート6a層上に第二の絶縁膜9を介して形成された制御ゲート10a層とを備えることとし、シリコン基板4上の浮遊ゲート6a層間に第三の絶縁膜5bを介して選択エピ層12が形成されるようにする。このような構成とすることにより、浮遊ゲート6a層間の静電容量を低減させ、隣接セル間干渉の影響を低減することが可能となる。

(もっと読む)

半導体装置の製造方法

【課題】 隣接した浮遊ゲートどうしがショートすることを抑制できる半導体装置の製造方法を提供すること

【解決手段】 スタックゲート型のNAND型フラッシュメモリが備えるメモリセルの浮遊ゲートをワード線方向に沿って分離した後に(ST.2)、シャロートレンチを形成して上記浮遊ゲートをビット線方向に沿って分離する(ST.3)。

(もっと読む)

不揮発性半導体記憶装置

【課題】フローティングゲート間の電気容量を抑制できる不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、直線状の第1のコントロールゲートと、第1のコントロールゲートと隣り合って並走する直線状の第2のコントロールゲートと、第1および第2のコントロールゲートと交差するアシストゲートと、それぞれが第1のコントロールゲートと半導体基板との間に配置されアシストゲートを挟んで互いに隣り合うように配置された第1および第2のフローティングゲートと、第2のコントロールゲートと半導体基板との間に配置された第3のフローティングゲートとを有している。第1のコントロールゲートの直線状に延びる方向に直交する方向を直交方向としたとき、第1および第2のフローティングゲートに挟まれる領域の直交方向に位置する領域に第3のフローティングゲートが配置されている。

(もっと読む)

半導体装置及びその動作方法

【課題】メモリセルのしきい値電圧のばらつきを減少することができ、誤動作を防止することができる不揮発性記憶回路を備えた半導体装置及びその動作方法を提供する。

【解決手段】3値以上の正数のM値のデータの書き込みが可能なメモリセルが行列状に複数配列されたメモリセルアレイと、メモリセルに接続され、メモリセルアレイ上を第1の方向に延在し、第2の方向に複数本配列されたワード線と、メモリセルに接続され、メモリセルアレイ上を第2の方向に延在し、第1の方向に複数本配列されたビット線と、複数本のビット線毎にそれぞれ配設された複数のセンスアンプ回路と、センスアンプ回路毎にそれぞれ配設されたラッチ回路とを備える。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】コントロールゲートの抵抗上昇を抑制でき、かつメモリセルのしきい値電圧Vthボケを抑制できる不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】メモリセルMCは、フローティングゲート8と、ゲート間絶縁層10と、コントロールゲート11と、保護絶縁層20とを有している。コントロールゲート11は高融点金属シリサイド層11bを有している。保護絶縁層20は、少なくとも高融点金属シリサイド層11bの壁面を覆うように形成されている。ゲート間絶縁層10直下のフローティングゲート8の幅がゲート間絶縁層10直上のコントロールゲート11の幅よりも小さい。

(もっと読む)

半導体装置

【課題】配線間のカップリング容量に起因する誤動作を防ぐことが可能な半導体装置を提供する。

【解決手段】半導体装置は、第1の配線層M1と、第2の配線層M2とを備え、第1の配線層M1および第2の配線層M2の各々は、グローバルビット線GBL_EVENと、グローバルビット線GBL_EVENが活性化されていないときに活性化されるグローバルビット線GBL_ODDとを含み、第1の配線層M1および第2の配線層M2の各々においてグローバルビット線GBL_EVENおよびGBL_ODDが交互に配置され、第1の配線層M1および第2の配線層M2におけるグローバルビット線GBL_EVENおよびGBL_ODDがほぼ平行に配置され、第1の配線層M1および第2の配線層M2の積層方向において、第1の配線層M1および第2の配線層M2に異なるグローバルビット線GBLが配置される。

(もっと読む)

フラッシュメモリ素子のレジスタ形成方法

【課題】SAFG工程を適用したフラッシュメモリ素子でレジスタを形成するためのフラッシュメモリ素子のレジスタ形成方法を提供すること。

【解決手段】半導体基板内に素子分離膜を形成した後、前記素子分離膜の所定の領域をエッチングしてトレンチを形成する段階と、全体構造の上部に第1ポリシリコン膜を形成した後、前記素子分離膜の上部が露出するまで研磨する段階と、誘電体膜パターンを形成した後、第2ポリシリコン膜を形成する段階と、前記第2ポリシリコン膜の所定の領域をエッチングし、前記第1ポリシリコン膜と第2ポリシリコン膜が連結される部分と前記誘電体膜パターンの上部に形成された第2ポリシリコン膜とが分離されるようにする段階と、全体構造の上部に層間絶縁膜を形成し、前記層間絶縁膜および第2ポリシリコン膜の所定の領域内にコンタクトプラグを形成する段階とを含む、フラッシュメモリ素子のレジスタ形成方法。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の動作不良発生を防止できるとともに、電極間絶縁膜によって相互に隣接するコントロールゲート電極間での寄生容量が大きくなることを回避可能な半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1を含む。トンネル絶縁膜3は、半導体基板上に設けられる。フローティングゲート電極11は、トンネル絶縁膜上に設けられる。電極間絶縁膜12は、フローティングゲート電極上に設けられる。コントロールゲート電極13は、電極間絶縁膜上に設けられ、電極間絶縁膜上の第1部分と第1部分上に設けられ且つチャネル長方向に関し第1部分より大きな幅を有する第2部分とを含む。ソース/ドレイン拡散領域15は、半導体基板の表面に形成され、フローティングゲート電極下方のチャネル領域を挟む。

(もっと読む)

不揮発性半導体記憶装置と半導体装置および、不揮発性半導体記憶装置の製造方法

【課題】 メモリセルのしきい値電圧の変動を抑制することができ、良好に読出しを行なうことができる不揮発性半導体記憶装置およびその製造方法を提供すると共に、配線間に形成される容量を低減することができ、駆動速度の向上を図ることができる半導体装置を提供する。

【解決手段】 半導体基板1の主表面上に、第1絶縁膜15を介して形成された第1フローティングゲートFGaと、第2フローティングゲートFGbと、第1フローティングゲートFGa上に形成された第1コントロールゲートCG1と、第2フローティングゲートFGb上に形成された第2コントロールゲートCG2と、第1コントロールゲートCG1と、第2コントロールゲートCG2とを覆うように形成された層間絶縁膜17と、層間絶縁膜17において、少なくとも、第1フローティングゲートFGaと第2フローティングゲートFGbとの間に位置する部分に形成された空隙部GAとを備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】微細、高集積で、素子分離能力に優れ、寄生抵抗、容量の小さいたフラッシュメモリを提供する。

【解決手段】SOI基板上にNAND型フラッシュEEPROMが形成される。素子領域(活性層)は、格子パターンで、その間の溝は、絶縁材により埋め込まれる。ロウ方向の素子同士は、完全に絶縁材により分離される。メモリセルが形成されるシリコン薄膜は、微量のn型不純物を含み、真性半導体に近い。周辺回路や選択ゲートトランジスタが形成されるシリコン薄膜は、p型である。メモリセル及び選択ゲートトランジスタの拡散層は、n型である。NANDストリングを構成する各メモリセルのチャネルは、しきい値の異なる少なくとも2つの領域から構成される。

(もっと読む)

半導体装置およびその製造方法

【課題】 補助ゲート電極構成を持つフラッシュメモリを有する半導体装置の信頼性を向上させる。

【解決手段】 半導体基板1の主面上にゲート絶縁膜2を介して形成された複数の補助ゲート電極AGと、補助ゲート電極AGの側壁に形成された側壁絶縁膜4により補助ゲート電極AGとは電気的に絶縁された状態で形成され、ゲート絶縁膜2を介して形成された浮遊ゲート電極FGと、浮遊ゲート電極FGを覆うように形成された層間絶縁膜5上に形成された複数の制御ゲート電極CGとを有している。この層間絶縁膜5の表面形状が凹凸状である。

(もっと読む)

フラッシュメモリ素子およびその製造方法

【課題】安定的な自己整列コンタクトを形成すると同時にプログラム動作の際にしきい値電圧干渉現象(Vt disturbance)を最小化しかつ動作速度を向上させることができる、フラッシュメモリ素子およびその製造方法を提供する。

【解決手段】半導体基板上に形成された多数のソース選択ライン、多数のワードラインおよび多数のドレイン選択ラインと、前記ワードラインの間、前記ワードラインと前記ソース選択ラインとの間、前記ワードラインと前記ドレイン選択ラインとの間の前記半導体基板上に形成された第1絶縁膜と、前記ソース選択ライン間の前記ソース選択ラインの側壁に形成され、第2絶縁膜からなるスペーサとを含み、前記第1絶縁膜の誘電定数値が前記第2絶縁膜の誘電定数値より低いことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 閾値変調が抑制された半導体装置およびその製造方法を提供する。

【解決手段】 半導体装置は、半導体基板10と、半導体基板10の主表面上にゲート絶縁膜42を介して複数形成された電荷蓄積用のフローティングゲート電極FGと、フローティングゲート電極FG上に形成されるコントロールゲート電極CGとを備える。半導体基板10における隣り合う複数のフローティングゲート電極FGが設けられる部分の主表面の高さが互いに異なる。

(もっと読む)

フラッシュメモリ素子及びその製造方法

【課題】 本発明は、フラッシュメモリ素子及びその製造方法に関するものであり、フローティングゲートを下部より上部が狭くなるように構成し、コントロールゲートとフローティングゲート間のオーバーラップ面積は維持させながらフローティングゲートの面積を減少させてプログラムスピード(program speed)の低下なしにセル間の干渉(interference)を減らすことを目的としている。

【解決手段】 フィールド領域及びアクティブ領域が定義された半導体基板と、前記フィールド領域の半導体基板に浅いトレンチ分離構造で形成される素子分離膜と、前記アクティブ領域の半導体基板上のトンネル酸化膜と、前記トンネル酸化膜上に形成され、上部より下部の幅が広いフローティングゲートと、前記フローティングゲートを含む半導体基板の表面段差に沿って形成された層間誘電膜と、前記層間誘電膜上に形成されるコントロールゲートとを含んで構成されるフラッシュメモリ素子であることを特徴とする。

(もっと読む)

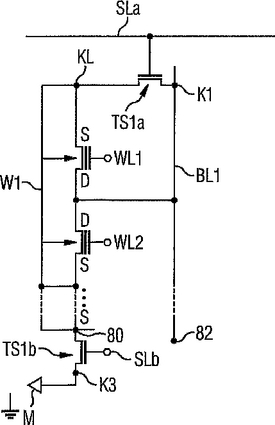

集積されたメモリ回路構造、特にUCPフラッシュメモリ

【課題】チップ面積の低減および電気特性の改善の少なくとも一方を実現できるメモリ回路構造50を提供する。

【解決手段】トランジスタをそれぞれ含む複数のメモリセルをマトリックス状に配置する。上記マトリックスの行における、メモリセルの各トランジスタの各制御電極に各ワード線WL1、WL2を配置する。上記マトリックスの列における、メモリセルの各トランジスタの各端子電極に各ビット線BL1、W1を配置する。スイッチング素子TS1aを、上記列毎に配置する。上記スイッチング素子TS1aは、上記の同一の列に位置する2つの各ビット線BL1、W1同士を電気的に断接できるようになっている。上記スイッチング素子TS1aにより、メモリ回路構造50における、チップ面積を低減および/または電気特性を改善できる。  (もっと読む)

(もっと読む)

半導体装置

【課題】FG間の容量結合を効果的に抑制することが可能な半導体装置を提供する。

【解決手段】第1及び第2の下部ゲート絶縁膜21と、第1及び第2のフローティングゲート22aと、第1及び第2の下部ゲート絶縁膜の側面及び第1及び第2のフローティングゲートの側面の一部を覆うように半導体基板11の表面から突出した素子分離絶縁膜31であって、上部に凹部が形成され、凹部の底は半導体基板の表面よりも下に位置し、第1及び第2のフローティングゲートの側面に接触する上端部の高さはそれぞれ第1及び第2のフローティングゲートの上面の高さより低く形成された素子分離絶縁膜と、上部ゲート絶縁膜23と、上部ゲート絶縁膜を介して及び上部ゲート絶縁膜と素子分離絶縁膜を介して第1及び第2のフローティングゲートの上面及び側面全体と対向形成され凹部の底まで埋め込まれたコントロールゲート線26とを備える。

(もっと読む)

フラッシュメモリ素子の製造方法

【課題】タングステンハードマスク膜の酸化を防止することができるとともに、ビットラインキャパシタンスを減らしてビットラインスピードを向上させることができる、フラッシュメモリ素子の製造方法の提供。

【解決手段】所定の構造物が形成された半導体基板上にストップ窒化膜と酸化膜を形成する段階と、前記酸化膜とストップ窒化膜にトレンチを形成する段階と、前記トレンチの側面にALD法によってバリア酸化膜を形成する段階と、前記トレンチ内にビットラインを形成する段階とを含む、フラッシュメモリ素子の製造方法を提供する。

(もっと読む)

半導体装置およびカップリング比検出装置

【課題】 フラッシュメモリセルのカップリング比を高精度で検出する。

【解決手段】 ダミーメモリセルトランジスタ(MCT)およびフローティングゲートとコントロールゲートが短絡された参照フローティングゲートトランジスタ(DT)のゲートを充放電して、直流電流をそれぞれ検出して、これらのトランジスタ(MCT,DT)のゲート容量を算出する。この算出したゲート容量に基づいて、ゲートカップリング比αcgを算出する。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】 誤動作耐性を向上させ、ひいては書き換え耐性を向上することのできる不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】 本発明のフラッシュメモリは、主表面を有する半導体基板2と、ビット線BL1と、半導体基板2の主表面上に形成された積層ゲート電極SG1,SG2と、積層ゲート電極SG1と積層ゲート電極SG2との間の半導体基板2の主表面に形成されたソース3bと、積層ゲート電極SG1を間に挟んでソース3bの反対側の半導体基板2の主表面に形成されたドレイン3aと、積層ゲート電極SG2を間に挟んでソース3bの反対側の半導体基板2の主表面に形成されたドレイン3cとを備えている。ドレイン3aとドレイン3cとが共に同一のビット線BL1に電気的に接続されている。さらに、積層ゲート電極SG1と積層ゲート電極SG2との間に形成され、かつ一定電位に固定されたシールド導電層1を備えている。

(もっと読む)

不揮発性半導体記憶装置

【課題】読み出し動作信頼性及び動作速度を向上できる不揮発性半導体記憶装置を提供すること。

【解決手段】不揮発性半導体記憶装置は、電荷蓄積層と制御ゲートとを備える第1MOSトランジスタと、ドレインが前記第1MOSトランジスタのソースに接続された第2MOSトランジスタとを含む複数のメモリセルと、同一行にある前記第1MOSトランジスタの前記制御ゲートが共通接続されて形成されたワード線と、前記ワード線毎に設けられ、対応する前記ワード線に電気的に接続され、且つ前記ロウデコーダが前記ワード線を選択するための第1ロウ選択信号を伝達する第1金属配線層と、前記半導体基板上に形成され、前記メモリセルを被覆する層間絶縁膜と、前記層間絶縁膜中の複数のレベルに形成された金属配線とを具備し、前記第1金属配線層は、最下層のレベルにある前記金属配線によって形成される。

(もっと読む)

121 - 140 / 142

[ Back to top ]