Fターム[5F101BF08]の内容

不揮発性半導体メモリ (42,765) | 動作 (2,287) | 寄生 (642) | 寄生容量 (142)

Fターム[5F101BF08]に分類される特許

61 - 80 / 142

半導体装置の作製方法

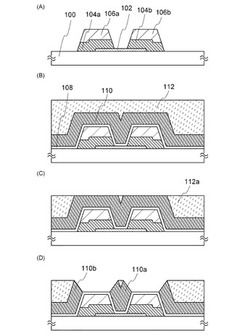

【課題】不良を抑制しつつ微細化を達成する半導体装置の作製方法を提供することを目的の一とする。

【解決手段】絶縁表面上に、酸化物半導体層と、酸化物半導体層と接するソース電極およびドレイン電極と、を形成し、ソース電極上およびドレイン電極上にそれぞれ絶縁層を形成し、酸化物半導体層、ソース電極、ドレイン電極および絶縁層上にゲート絶縁層を形成し、ゲート絶縁層上に導電層を形成し、導電層を覆うように絶縁膜を形成し、導電層におけるソース電極またはドレイン電極と重畳する領域の少なくとも一部が露出するように絶縁膜を加工し、導電層の露出した領域をエッチングして、ソース電極とドレイン電極に挟まれた領域の少なくとも一部と重畳するゲート電極を自己整合的に形成する半導体装置の作製方法である。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、メモリセルアレイを有する半導体装置において、直列に接続された第1乃至第mのメモリセルに含まれる各ノードに生じる寄生容量の値を同等の値とすることで、安定して動作可能な半導体装置とする。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】低消費電力で動作し、記憶情報の信頼性が高く、小型で軽量、安価な記憶装置と

その駆動方法を提供することを課題とする。さらに低消費電力で動作し、記憶情報の信頼

性が高く、無線通信距離の長い、小型で軽量、安価な半導体装置とその駆動方法を提供す

ることを課題とする。

【解決手段】記憶装置は、少なくとも記憶素子がマトリックス状に配置されたメモリセル

アレイと、書き込み回路とを有し、記憶素子は第一の導電層と、第二の導電層と第一の導

電層と第二の導電層とに挟まれて設けられた有機化合物層とを有し、書き込み回路は、複

数回印加する電圧を発生させる電圧発生回路と、電圧の出力時間を制御するタイミング制

御回路とを有することを特徴とする。

(もっと読む)

パルス変換回路

【課題】回路面積を低減する。

【解決手段】第1の信号が入力され、第2の信号を出力する論理回路を具備し、論理回路は、ゲートに第1の信号が入力され、ゲートの電圧に応じて第2の信号の電圧を第1の電圧に設定するか否かを制御するP型トランジスタと、エンハンスメント型であり、閾値電圧の絶対値がP型トランジスタより大きく、ゲートに第1の信号が入力され、ゲートの電圧に応じて第2の信号の電圧を第1の電圧より高い第2の電圧に設定するか否かを制御するN型トランジスタと、を備え、P型トランジスタは、チャネルが形成され、第14族の元素を含有する半導体層を含み、N型トランジスタは、チャネルが形成され、キャリア濃度が1×1014/cm3未満である酸化物半導体層を含む。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】書込・消去特性が高く、動作の信頼性が高い半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置は、半導体基板と、前記半導体基板上に設けられたトンネル絶縁膜と、前記トンネル絶縁膜上に設けられた第1電極と、前記第1電極上に設けられた電極間絶縁膜と、前記電極間絶縁膜上に設けられた第2電極と、を備える。前記電極間絶縁膜は、積層絶縁層と、前記積層絶縁層上に設けられ、前記積層絶縁層よりもバリアハイトが低い電荷蓄積層と、前記電荷蓄積層上に設けられ、前記電荷蓄積層よりもバリアハイトが高いブロック絶縁層と、を有する。前記積層絶縁層は、第1絶縁層と、前記第1絶縁層上に設けられ、前記第1絶縁層よりもバリアハイトが低い量子効果層と、前記量子効果層上に設けられ、前記量子効果層よりもバリアハイトが高い第2絶縁層と、を有する。

(もっと読む)

不揮発性半導体メモリトランジスタ、不揮発性半導体メモリ、および、不揮発性半導体メモリの製造方法

【課題】浮遊ゲートと制御ゲート間の容量を大きくすることができるとともに、かつ制御ゲートと島状半導体間の寄生容量を低減する、島状半導体を用いた構造を持つ不揮発性半導体メモリ、およびその製造方法を提供する。

【解決手段】不揮発性半導体メモリを構成する不揮発性半導体メモリトランジスタは、基板側からソース領域303、チャネル領域304及びドレイン領域302がこの順に形成された島状半導体301と、チャネル領域の外周を囲むように、トンネル絶縁膜305を間に介在させて配置された中空柱状の浮遊ゲート306と、当該浮遊ゲートの外周を囲むように、インターポリ絶縁膜307を間に介在させて配置された中空柱状の制御ゲート308と、を備えている。浮遊ゲートと、制御ゲートの上面、下面および内側面との間には、インターポリ絶縁膜が介在配置されている。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、第2のトランジスタの半導体層にはオフセット領域が設けられた半導体装置を提供する。第2のトランジスタを、オフセット領域を有する構造とすることで、第2のトランジスタのオフ電流を低減させることができ、長期に記憶を保持可能な半導体装置を提供することができる。

(もっと読む)

配線形成方法

【課題】配線層で、配線密度の高い領域では隣接する配線間のショートを防ぎ、配線密度の低い領域では所望の平坦度が得られるとともに所望の配線抵抗が得られるように配線高さを制御できる配線形成方法を提供する。

【解決手段】まず、基板上に第1の絶縁膜111と、第1の絶縁膜111に比してCMP研磨レートの小さい所定の厚さの第2の絶縁膜112を順に積層させて層間絶縁膜11を形成し、ついで、層間絶縁膜11の第1の領域に第1の配線密度となり、第2の領域に第1の配線密度よりも低い第2の配線密度となるように、第2の絶縁膜112を貫通し、底部が第1の絶縁膜111に至る配線形成用溝21を形成した後、配線形成用溝21を形成した層間絶縁膜11上に導電性材料膜14を形成し、そして、CMP法によって、少なくとも第1の領域で第1の絶縁膜111が露出、後退するように層間絶縁膜11と導電性材料膜14を研磨する。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。または、良好な特性を維持しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面に第1の絶縁膜を形成し、第1の絶縁膜上に第1のマスクを形成し、第1のマスクにスリミング処理を行うことにより、第2のマスクを形成し、第2のマスクを用いて第1の絶縁膜にエッチング処理を行うことにより、第2の絶縁膜を形成し、第2の絶縁膜を覆うように第1の導電膜を形成し、第1の導電膜および第2の絶縁膜に研磨処理を行うことにより、等しい厚さの第3の絶縁膜、ソース電極およびドレイン電極を形成し、第3の絶縁膜、ソース電極およびドレイン電極上に酸化物半導体膜を形成し、酸化物半導体膜上にゲート絶縁膜を形成し、ゲート絶縁膜上の第3の絶縁膜と重畳する領域にゲート電極を形成する半導体装置の作製方法である。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面上に絶縁膜を形成し、絶縁膜上にマスクを形成し、マスクにスリミング処理を行い、マスクを用いて絶縁膜にエッチング処理を行い、絶縁膜を覆うように導電膜を形成し、導電膜および絶縁膜に研磨処理を行うことにより、導電膜および絶縁膜の厚さを等しくし、導電膜をエッチングして、導電膜より厚さの小さいソース電極およびドレイン電極を形成し、絶縁膜、ソース電極、およびドレイン電極と接する酸化物半導体膜を形成し、酸化物半導体膜を覆うゲート絶縁膜を形成し、ゲート絶縁膜上の絶縁膜と重畳する領域にゲート電極を形成する。

(もっと読む)

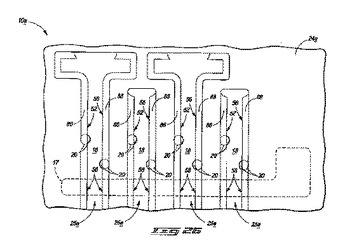

メモリセル電荷記憶素子あたりに二重のコントロールゲートを有するフラッシュメモリセルアレイ

【課題】フローティングゲートが少なくとも2つのコントロールゲートラインと容量的に結合するようになっているフラッシュNANDタイプのEEPROMシステムの提供。

【解決手段】コントロールゲートラインはフローティングゲートの側壁と結合するようにフローティングゲート間に位置し、メモリセルの結合比が望ましく高められる。フローティングゲートの選択された行の両側の両方のコントロールゲートラインは普通同じ電圧まで高められ、隣接するフローティングゲートの選択されていない行に結合された第2のコントロールゲートラインは低く保たれる。選択されたフローティングゲートの領域でその電圧を選択的に高めるために、コントロールゲートラインを基板と容量的に結合させる。フローティングゲートの長さとコントロールゲートラインの厚さとは、スペーサのエッチマスクを形成することによってプロセスの最小分解エレメントより小さくされ得る。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】寄生容量を抑制した不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】第1方向に沿って交互に積層された複数の電極膜WLと複数の電極間絶縁膜14とを有する積層構造体MLと、積層構造体MLを第1方向に貫通する半導体ピラーSPと、複数の電極膜WLのそれぞれと半導体ピラーSPとの間に設けられた電荷蓄積膜48と、電荷蓄積膜48と半導体ピラーSPとの間に設けられた内側絶縁膜42と、電極膜WLのそれぞれと電荷蓄積膜48との間に設けられた外側絶縁膜43と、を有するメモリ部MUと、メモリ部MUと、第1方向に対して直交する第2方向に沿って併設され、積層構造体MLの第1方向に沿った少なくとも一つの電極膜WLの位置と同じ位置に絶縁部50と、を有する非メモリ部PR10とを備えている。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いたトランジスタと、酸化物半導体以外の半導体材料を用いたトランジスタとを積層して、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタと、第1のトランジスタ上に絶縁層と、絶縁層上に第2のトランジスタと、を有し、第1のトランジスタは、第1のチャネル形成領域を含み、第2のトランジスタは、第2のチャネル形成領域を含み、第1のチャネル形成領域は、第2のチャネル形成領域と異なる半導体材料を含んで構成され、絶縁層は、二乗平均平方根粗さが1nm以下の表面を有する半導体装置。

(もっと読む)

周期的な酸化およびエッチングのための装置と方法

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体OSを用い、オフ状態でのソースとドレイン間のリーク電流(オフ電流)が少ない書き込み用トランジスタ162、書き込み用トランジスタ162と異なる半導体材料を用いた読み出し用トランジスタ160及び容量素子164を含む不揮発性のメモリセルを有する半導体装置において、メモリセルへの情報の書き込みは、書き込み用トランジスタ162のソース電極またはドレイン電極の一方と、容量素子164の電極の一方と、読み出し用トランジスタ160のゲート電極とが電気的に接続されたノードFGに電位を供給し、ノードFGに所定量の電荷を保持させることで行う。書き込みを1×109回行う前後において、メモリセルのメモリウィンドウ幅の変化量は2%以内である。

(もっと読む)

不揮発性半導体記憶装置と半導体装置および、不揮発性半導体記憶装置の製造方法

【課題】配線間に形成される容量を低減でき、メモリセルのしきい値電圧の変動を抑制できる不揮発性半導体記憶装置およびこの製造方法を提供する。

【解決手段】半導体基板1上に、第1絶縁膜15を介して形成された第1フローティングゲートFGa及び第2フローティングゲートFGbと、第1フローティングゲートFGa上に、第3絶縁膜18aを介して形成され、幅が第1フローティングゲートFGaより広い第1幅広部28aを有する第1コントロールゲートCG1と、第2フローティングゲートFGb上に、同様に形成された第2幅広部28bを有する第2コントロールゲートCG2と、第1コントロールゲートCG1と、第2コントロールゲートCG2とを覆うように形成された層間絶縁膜17と、層間絶縁膜17において、少なくとも、第1フローティングゲートFGaと第2フローティングゲートFGbとの間に位置する部分に形成された空隙部GAとを備える。

(もっと読む)

半導体装置

【課題】記憶保持期間において、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のソース電極および第1のドレイン電極と、第1のソース電極および第1のドレイン電極と電気的に接続され、酸化物半導体材料が用いられている第1のチャネル形成領域と、第1のチャネル形成領域上の第1のゲート絶縁層と、第1のゲート絶縁層上の第1のゲート電極と、を有する第1のトランジスタと、容量素子と、を有し、第1のトランジスタの第1のソース電極または第1のドレイン電極の一方と、容量素子の電極の一方とは、電気的に接続された半導体装置である。

(もっと読む)

半導体装置

【課題】記憶保持期間において、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体以外の半導体材料が用いられた第1のチャネル形成領域を有する第1のトランジスタ160と、第1のトランジスタ160の上方の、酸化物半導体材料が用いられた第2のチャネル形成領域を有する第2のトランジスタ162と、容量素子164と、を有し、第2のトランジスタ162の第2のソース電極または第2のドレイン電極の一方と、容量素子164の電極の一方とは、電気的に接続される。

(もっと読む)

半導体装置の製造方法

【課題】浮遊ゲート電極を有するメモリセルの高集積化を実現する半導体装置の製造方法を提供する。

【解決手段】半導体層11の表面にトンネル絶縁膜12を介してシリコンを含む第1の導電体層を形成する工程と、第1の導電体層の表面から半導体層11に至る分離溝9を形成し、第1の導電体層が所定幅で分離された、浮遊ゲート電極となる複数の導電板13bを形成する工程と、導電板13b側面の中間部まで、分離溝9を素子間絶縁膜15で埋め込む工程と、複数の導電板13bの間隔を所定幅と同等以上の幅に維持しながら、導電板13bの露出面にシリコン窒化膜16aを形成する工程と、制御ゲート電極19aとなる第2の導電体層を形成して分離溝9の上部を埋め込む工程と、を備え、シリコン窒化膜16aは、窒素元素を含む原料ガスを励起させて生成する窒素ラジカルによって、導電板13bに含まれるシリコンを窒化して形成される。

(もっと読む)

集積回路の製造において複数の導電線を形成する方法、導電線アレイを形成する方法、および集積回路

集積回路の製造において導電線対を形成する方法は、基板上に受けられるダマシン材料にトレンチを形成することを含み、導電性材料34a/35aが、そのダマシン材料を覆ってそしてトレンチ内へ蒸着されてそのトレンチを過充填する。その導電性材料は、少なくともダマシン材料へと戻すように除去されて、そのトレンチ内に残っている導電性材料の少なくともいくらかが残される。エッチングがトレンチ内で導電性材料を通って縦方向に処理されて、トレンチ内に少なくとも第1および第2の導電線の長さの大部分に沿って横断面図において互いにミラー像となる第1および第2の導電線が形成される。他の装いが考えられる。  (もっと読む)

(もっと読む)

61 - 80 / 142

[ Back to top ]