Fターム[5F101BH09]の内容

不揮発性半導体メモリ (42,765) | 製造方法 (5,495) | イオン注入 (487)

Fターム[5F101BH09]の下位に属するFターム

イオン注入によるトラップ形成 (10)

Fターム[5F101BH09]に分類される特許

461 - 477 / 477

半導体装置の製造方法

【課題】 使用中の電荷の不要な移動に伴う閾値電圧の変動を抑制することができる半導体装置の製造方法を提供する。

【解決手段】 Si基板1の表面に、不揮発性メモリセル、nMOSトランジスタ及びpMOSトランジスタを形成した後、不揮発性メモリセル、nMOSトランジスタ及びpMOSトランジスタを覆う層間絶縁膜19を形成する。次に、層間絶縁膜19中に、夫々、不揮発性メモリセルのコントロールゲート11、nMOSトランジスタのソース又はドレイン17、pMOSトランジスタのソース又はドレイン18に接続される複数個のコンタクトプラグ20を形成する。そして、複数個のコンタクトプラグ20を介して、コントロールゲート11とnMOSトランジスタ及びpMOSトランジスタのソース又はドレイン17、18とを接続する単層の配線21を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の信頼性の劣化を抑制しつつ、トレンチ内の内壁酸化膜に多量の窒素を導入する。

【解決手段】シリコン基板1の素子分離領域に形成したトレンチ2の内壁を酸化して内壁酸化膜3を形成する。当該内壁酸化膜3に対しては、熱窒化処理とラジカル窒化処理との2つの窒化処理が行われる。熱窒化処理によって内壁酸化膜3とシリコン基板1との界面近傍に第1窒化層3aが形成され、ラジカル窒化法によって内壁酸化膜3の表面に第2窒化層3bが形成される。前記熱窒化処理においては、活性領域に形成される半導体素子の信頼性が生じない程度に、導入する窒素の量を抑制する。

(もっと読む)

抵抗回路と不揮発性メモリーとを有する半導体装置の製造方法

【課題】 高精度で高安定な多結晶シリコンの抵抗体と特性ばらつきの小さいMOSトランジスターと2つの多結晶シリコンから成るEEPROMを同一チップに形成する場合、工程数の増大が問題となっていた。逆に工程数を抑えようとすると、抵抗体の精度やMOSトランジスターの特性ばらつきを犠牲にせざるを得ないという問題があった。

【解決手段】 膜厚100Å〜2000Åの第1の多結晶シリコン膜を抵抗体とフローティングゲートに、膜厚3000Å〜5000Åの第2の多結晶シリコン膜をHV-Tr.、LV-Tr.のゲートとコントロールゲートに用いることで、工程数の削減と高精度化が同時に実現できる。

(もっと読む)

半導体記憶装置およびその製造方法並びに携帯電子機器

【課題】微細化が容易な半導体記憶装置を提供する。

【解決手段】半導体基板211上には、ゲート絶縁膜214を介して単一のゲート電極217を形成している。ゲート電極217の両側には、第1,第2のメモリ機能体261,262を形成している。半導体基板211のゲート電極217側の表面部にはP型のチャネル領域472を形成し、チャネル領域472の両側にN型の第1,第2の拡散領域212,213を形成している。チャネル領域472は、第1,第2のメモリ機能体261,262下に位置するオフセット領域401と、ゲート電極217下に位置するゲート電極下領域402とで構成されている。オフセット領域401にP型の導電型を与える不純物の濃度は、ゲート電極下領域402にP型の導電型を与える不純物の濃度に比べて実効的に薄くなっている。

(もっと読む)

不揮発性メモリーデバイスおよびそれの形成方法

一実施形態において半導体デバイス(10)は、半導体基板(20)中に均一に注入された第1の導電型を有する高ドープ層(26)を有し、基板(20)の頂部表面と高ドープ層(26)との間にはチャンネル領域(28)が配置されている。別の実施形態では半導体デバイス(70)は、カウンタドープされたチャンネル(86)およびそのチャンネルの下のパンチスルー防止領域(74)を有する。ゲートスタック(32)を基板(20)上に形成する。第2の導電型を有するソース(52)およびドレイン(54,53)をその基に注入する。得られた不揮発性メモリーセルは、低い自然閾値電圧を与えることで、読取サイクル時の閾値電圧ドリフトを小さくする。さらに、第2の導電型を有し、ドレイン側に斜めで注入されたハロー領域(46)を用いて、熱キャリア注入を支援することができ、それによってより高いプログラミング速度が可能となる。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】 不揮発性半導体記憶装置のデータ線間のリーク電流を低減する。

【解決手段】 AND型のフラッシュメモリを有する不揮発性半導体記憶装置のメモリアレイにおいて、ワード線の隣接間であって、補助ゲート配線AGLの隣接間の接合素子分離領域に凹部8を形成し、その凹部8の形成領域の半導体基板1の主面(第1主面部)の高さを、補助ゲート配線AGLが対向する半導体基板1の主面(第2主面部)の高さよりも低くした。これにより、フラッシュメモリの動作時に、上記接合素子分離領域においてドレイン線/ソース線間にリーク電流が流れてしまうのを抑制することができる。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】半導体記憶装置およびその製造方法。

【解決手段】トンネル効果を利用するトランジスタ100Cを含む半導体記憶装置の製造方法であって、半導体層10に、トレンチ素子分離法により、トランジスタ100Cの形成領域10Cを画定する素子分離絶縁層20を形成する工程と、トランジスタ100Cの形成領域10Cにおいて、少なくとも素子分離絶縁層20に隣接した半導体層10の上部のコーナー部11に、酸化抑制物質を注入する工程と、トランジスタ100Cの形成領域10Cにおける半導体層10の上方に、熱酸化によりトンネル絶縁層31を形成する工程と、トンネル絶縁層31の上方にフローティングゲート電極32を形成する工程と、フローティングゲート電極32に印加する電圧を制御するコントロールゲート42を形成する工程と、少なくともトランジスタ100Cの形成領域10Cに、ソースおよびドレイン領域を形成する工程と、を含む。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】半導体記憶装置の製造方法。

【解決手段】領域10Cを画定する素子分離溝を形成する工程と、半導体層10の上部コーナー部11を熱酸化によりラウンディング形状にする第1ラウンド酸化工程と、半導体層10の上方に、耐酸化膜50を形成する工程と、領域10A,10Bにおいて、素子分離溝に隣接した半導体層10の上部のコーナー部11を熱酸化によりラウンディングする第2ラウンド酸化工程と、素子分離溝に分離絶縁層20を形成する工程と、半導体層10の上方にトンネル絶縁層31を形成する工程と、トンネル絶縁層31の上方にフローティングゲート電極32を形成する工程と、フローティングゲート電極32に印加する電圧を制御するコントロールゲート42を形成する工程と、半導体層10にソースおよびドレイン領域を形成する工程とを含み、第1ラウンド酸化工程における熱酸化温度は、第2ラウンド酸化工程に熱酸化温度より高い。

(もっと読む)

不揮発性半導体記憶装置

【課題】 複数のスタックゲート型メモリセルを含むフラッシュメモリにおいて、消去前書込動作を不要とすることにより一括消去動作に要する時間を短縮し、データの書換動作に要する時間も短縮することである。

【解決手段】 消去時に、複数のメモリセルのソース1003からフローティングゲート1005に同時に電子を注入する。それにより、複数のメモリセルのしきい値電圧が上昇する。プログラム時に、選択されたメモリセルのフローティングゲート1005からドレイン1002に電子を放出する。それにより、選択されたメモリセルのしきい値電圧が下降する。

(もっと読む)

不揮発性半導体メモリ装置およびその動作方法

【課題】電源電圧相当の電圧でメモリデバイスの閾値電圧を最大限に上昇させる動作を実現する。

【解決手段】半導体基板2とゲート電極6との間に形成され電荷蓄積能力を有する積層膜5を備えるメモリトランジスタ1は、書き込み時と読み出し時とで短チャネル効果が生じているか否かの境界として見積もられるチャネル長Lminが異なり、当該異なるチャネル長Lmin(R)とLmin(W)の間に、実デバイスのチャネル長Lを有する。

(もっと読む)

フラッシュッモリ素子の製造方法

【課題】ONO層のスマイリング現象及びトンネル酸化膜のバーズビーク現象を防止することができ、コントロールゲートの面抵抗の増加を抑制することができるうえ、全体時間時間を短縮して生産性を向上させることができるフラッシュメモリ素子の製造方法を提供する。

【解決手段】ゲート形成工程でセル領域及び周辺回路領域の半導体基板上にゲートを形成する段階と、前記ゲート形成工程時のエッチング損傷を回復するために第1急速熱酸化工程を行うことにより、サイドウォール酸化膜を形成する段階と、前記セル領域にセルトランジスタの接合部を形成する段階と、前記周辺回路領域に周辺回路トランジスタの接合部を形成する段階と、前記接合部に注入されたイオンを活性化させるために第2急速熱酸化工程を行う段階とを含む。

(もっと読む)

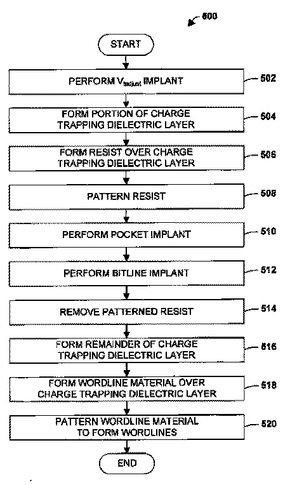

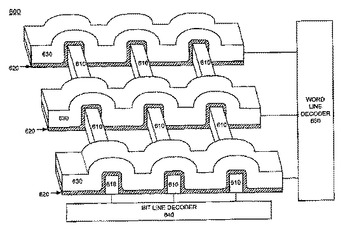

デュアルポリを用いたビット線注入

本発明は、トランジスタベースメモリデバイス(600)の形成において、デュアルポリプロセス(500)を実装することに関する。このプロセスにより、従来のビット線よりも少ないエネルギーで埋め込みビット線(662)を、深さを浅くして形成することができ、リソースおよびスペースを節約し、Vtロールオフを改善する。埋め込みビット線(662)上には酸化物材料(670、674)も形成され、ビット線(662)とワード線(678)との間の破壊電圧を改善(例えば、増加する)し、これにより、プログラミング電荷と消去電荷との間の識別度を更に高めることができ、さらに、結果として、より確実にデータを記録することができる。このプロセス(500)はまた、埋め込みビット線幅(666)の縮小を促進し、それにより、ビット線(662)を互いに近接して形成することができる。その結果、より多くのデバイスが、同じ領域あるいはより小さな領域に”詰め込まれ”得る。  (もっと読む)

(もっと読む)

フラッシュメモリ装置のワード線を保護するための方法および装置

製造中に、プロセスに関連する帯電からフラッシュメモリのワード線(WL)およびメモリセル(101)を保護するための方法と構造とが与えられる。ドープされたポリシリコンのワード線(110a)の端部にドープされていないポリシリコン(110b)が形成され、抵抗(110b)が生成される。これを通じて、プロセスにより生じる電荷が、基板(102)に結合された、ドープされたポリシリコン放電構造(110c)へ放電される。ワード線抵抗(110b)、および、放電構造(110c)は、単一のパターニングされたポリシリコン構造として形成される。ワード線(110a)および放電部分(110c)は導電性になるように選択的にドープされ、また、抵抗部分(110b)は、製造後に通常のセル動作が可能なほどに十分高い抵抗が与えられる一方で、製造中にプロセスに関連する電荷に対しては放電路を供給するように、実質的にドープされない。  (もっと読む)

(もっと読む)

SONOSメモリセルの相補ビット妨害および蓄電の改善のためのポケット注入

デュアルビットメモリコアのアレイの少なくとも一部を形成する方法が開示される。最初に、電荷トラップ誘電層(608)の一部が基板(602)上に形成され、電荷トラップ誘電層(608)の一部の上にレジスト(614)が形成される。レジスト(614)がパターニングされ、ポケット注入(630)が所定の角度で実行され、基板(602)内にポケット注入部(620)が形成される。次に、基板(602)内に埋込みビット線(640)を形成するためにビット線注入(634)が実行される。次に、パターニングされたレジストが除去され、電荷トラップ誘電層(608)の残部が形成される。電荷トラップ誘電層の残部の上にワード線の材料(660)が形成されて、それはビット線(640)上にワード線(662)を形成するためにパターニングされる。ポケット注入部(620)は、特に、微細化によって生じるおそれのある相補ビット妨害(CBD)を軽減するのに役立つ。このように、ここに記載する発明思想により、半導体デバイスを小型化でき、高い実装密度を実現することができる。  (もっと読む)

(もっと読む)

半導体装置と半導体装置の製造方法

バリア性を有する絶縁膜サイドウォールスペーサを有する半導体装置を提供する。 半導体装置は、半導体基板の上に形成されたゲート酸化膜とゲート電極と;半導体基板内に形成されたソース/ドレイン領域と;ゲート電極側壁上に形成された2層以上の積層サイドウォールスペーサであって、最外層以外の層として窒化膜を含み、最外層は、酸化膜又は酸化窒化膜で形成され、下面が半導体基板またはゲート酸化膜、又は窒化膜以外の他のサイドウォールスペーサ層と接している第1積層サイドウォールスペーサと;を有する。さらに、不揮発性メモリの積層ゲート電極構造と;積層ゲート電極構造の側壁上に形成され、中間層として半導体基板に接しない窒化膜を含む3層以上の第2積層サイドウォールスペーサと;を有することもできる。  (もっと読む)

(もっと読む)

2−トランジスタメモリセル及びその製造方法

本発明は、メモリゲートスタック(1)を有する記憶トランジスタ(1)及び選択トランジスタを有する2-トランジスタメモリセルを基板(50)上に製造する方法であって、トンネル誘電層(51)が前記基板(50)と前記メモリゲートスタック(1)との間にもたらされる方法を提供する。前記方法は、第一の導電層(52)及び第二の導電層(54)をもたらし、前記第二の導電層(54)をエッチし、それによってコントロールゲートを形成し、前記第一の導電層(52)をエッチし、それによってフローティングゲートを形成することによって前記メモリゲートスタック(1)を形成するステップを有する。前記方法は更に、前記第一の導電層(52)がエッチされる前に、前記トンネル誘電層(51)の下に形成されるべきチャネルの方向で前記コントロールゲートに対してスペーサ(81)を形成するステップと、その後、前記第一の導電層(52)をエッチするために前記スペーサ(81)をハードマスクとして使用し、それによって前記フローティングゲートを形成し、それによってフローティングゲートをコントロールゲートに自己整合させるステップとを有することを特徴とする。本発明は、前記コントロールゲート(54)は前記フローティングゲート(52)よりも小さくなり、スペーサ(81)が、前記コントロールゲート(54)に隣接してもたらされるメモリセルも提供する。  (もっと読む)

(もっと読む)

不揮発性メモリデバイス

不揮発性メモリデバイス(100)は、基板(110)、絶縁層(120)、フィン(210)、複数の誘電層(310〜330)及び制御ゲート(510/520)を備える。絶縁層(120)は、基板(110)上に形成され、フィン(210)は、絶縁層(120)上に形成される。誘電層(310〜330)は、このフィン(210)を覆うように形成され、制御ゲート(510/520)は、誘電層(310〜330)上に形成される。誘電層(310〜330)は、メモリデバイス(100)の電荷格納構造として機能する酸化物−窒化物−酸化物層を備える。  (もっと読む)

(もっと読む)

461 - 477 / 477

[ Back to top ]