Fターム[5F101BH10]の内容

不揮発性半導体メモリ (42,765) | 製造方法 (5,495) | イオン注入 (487) | イオン注入によるトラップ形成 (10)

Fターム[5F101BH10]に分類される特許

1 - 10 / 10

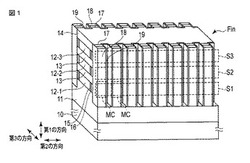

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセルの電荷蓄積層内での電荷の横方向の移動を抑制する。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、第1乃至第nの半導体層(nは2以上の自然数)12−1〜12−3と、第1乃至第nの半導体層12−1〜12−3をチャネルとする第1乃至第nのメモリストリングS1〜S3とを備える。第iのメモリストリング(iは1〜nのうちの1つ)Siは、第iの半導体層12−iの第3の方向にある表面上に、複数のメモリセルMCに対応する、複数の電荷蓄積層16及び複数のコントロールゲート18を備える。また、第iのメモリストリング内において、少なくとも第2の方向に隣接する2つのメモリセルMCの電荷蓄積層16が互いに結合される。そして、複数のコントロールゲート18間に、複数の電荷蓄積層16のバンドオフセットを上昇させる金属元素19が添加される。

(もっと読む)

半導体装置およびその製造方法

【課題】 周辺回路領域の電荷蓄積層へのホットキャリア注入の影響を少なくする半導体装置等を提供する。

【解決手段】 半導体装置であって、少なくとも1つの不揮発性記憶セルの少なくとも1つの第1のトランジスタと、前記少なくとも1つの不揮発性記憶セルを駆動するための少なくとも1つの第2のトランジスタと、を含む。第1のトランジスタは、第1のゲート絶縁層と、第1のゲート電荷蓄積層と、第2のゲート絶縁層とを有する。第2のトランジスタは、第3のゲート絶縁層と、第2のゲート電荷蓄積層と、第4のゲート絶縁層とを有する。フッ素系ガスおよび/または水素系ガスを用いるイオン注入が実施された前記第2のゲート電荷蓄積層(22b’)の全部または一部の第1の電荷蓄積能力は、フッ素系ガスおよび/または水素系ガスを用いるイオン注入が実施される前の前記第2のゲート電荷蓄積層(22b’)の前記全部または前記一部の第2の電荷蓄積能力より低い。

(もっと読む)

不揮発性半導体記憶装置及びその書き込み方法

【課題】 本発明は、NAND型不揮発性半導体記憶装置の集積密度を向上させることが

できる。

【解決手段】 本発明の不揮発性半導体記憶装置は、半導体基板1表面内に、チャネル領

域を挟んでソース領域2及びドレイン領域3が形成される。そして、チャネル領域上に、

第1の絶縁層8a、トラップ層8b、第2の絶縁層8cの順で積層された積層膜8が形成

される。そして、積層膜8のソース領域側側部には、第3の絶縁層6が形成される。また

、ソース領域2と第3の絶縁層6との間のチャネル領域上には、ゲート絶縁膜5が形成さ

れる。そして、ゲート絶縁膜5上及び積層膜8のソース領域2側端部上には、制御ゲート

7が形成される。また、積層膜8上であって、ソース領域2からドレイン領域3の方向に

向かって、制御ゲート7と離間形成され、かつ互いに離間形成された複数のプログラミン

グゲート9とを備える。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】電荷トラップ効率が可及的に高いMONOS型メモリセルを有する不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】半導体基板5に離間して設けられたソース・ドレイン領域4a、4bと、ソース領域とドレイン領域4a、4bの間の半導体基板5上に設けられたトンネル絶縁膜12と、トンネル絶縁膜12上に設けられ、電荷をトラップする電荷蓄積膜13と、電荷蓄積膜13上に設けられた制御ゲート電極16と、電荷蓄積膜13と制御ゲート電極16との間に設けられ、電荷蓄積膜13側に設けられた遷移アルミナ層14aおよび制御ゲート電極16側に設けられたα相アルミナ層15aを有するアルミナ膜と、を含むメモリセルを備えている。

(もっと読む)

電荷トラップ層を有する不揮発性メモリ素子及びその製造方法

【課題】電荷トラップ層を有する不揮発性メモリ素子及びその製造方法を提供する。

【解決手段】結晶質物質を含むように形成された電荷トラップ層を備える不揮発性メモリ素子である。基板上にトンネリング絶縁膜を形成する工程と、トンネリング絶縁膜上に結晶質電荷トラップ層を形成する工程と、を含む不揮発性メモリ素子の製造方法である。

(もっと読む)

電荷蓄積構造

【課題】 低い電圧でデータ格納が可能なセミコンダクタ・オン・インシュレータタイプの構造及びその製造プロセスを提供する。

【解決手段】 本発明は、ドナー基板(10)の半導体層(11)と、絶縁体層(60)と、レシーバ基板(20)とを備えるセミコンダクタ・オン・インシュレータタイプの構造において、レシーバ基板(20)上にドナー基板(10)を接合するステップを備え、基板の少なくとも1つが絶縁体層でコーティングされる、セミコンダクタ・オン・インシュレータタイプの構造の製造プロセスであって、電荷キャリアを保持するのに適切な電気的に活性なトラップを備える、いわゆる、トラップ界面(30)を接合界面に形成するステップを備えることを特徴とする、製造プロセスに関する。また、本発明は、トラップ界面を備えるセミコンダクタ・オン・インシュレータタイプの構造に関する。

(もっと読む)

絶縁膜、およびそれを用いた半導体装置

【課題】リーク特性等の特性が優れた高誘電体絶縁膜を提供する。

【解決手段】本発明の絶縁膜は、第1の金属と酸素からなる金属酸化物にフッ素を導入した絶縁膜であって、窒素或いは前記金属酸化物をなす第1の金属の価数よりも小さな価数の第2の金属を少なくとも1つ、前記フッ素と同時に導入したことを特徴とし、窒素または前記第2の金属の量を[X]、フッ素の量を[F]と表わすとき、{[X]−[F]}/2≦8.4atomic%であることを特徴とする。

(もっと読む)

NROM用2次注入

2次電子注入(SEI)は、NROMセルなどのONO層内に別個の電荷蓄積領域を有するNVMセルをプログラムするために使用される。低ワード線電圧(Vwl)、負基板電圧(Vb)、更に狭い及び深いインプラントの種々の組合せによりプロセスが促進される。第2ビット問題を制御することができ、保存及びパンチスルーを改善することができる。より低いSEIプログラミング電流が、ビット線抵抗、必要な接点の数、及び電源要件に関する制約の緩和をもたらすことができる。 (もっと読む)

微粒子含有体及び微粒子含有体の製造方法並びに記憶素子、半導体装置及び電子機器

【課題】良好な特性が得られる微粒子含有体と、比較的少ない手間で良好な特性の微粒子含有体を製造できる微粒子含有体の製造方法を提供すること。

【解決手段】シリコン基板100の表面に、膜厚が約50nmのシリコン酸化膜110を熱酸化によって形成する。シリコン酸化膜110中に、約30keVの注入エネルギーで、負イオン注入法によって銀を注入する。銀が注入されたシリコン酸化膜110を、200℃よりも高く、かつ、銀の融点未満の温度で熱処理して、銀微粒子を形成する。酸化雰囲気中で熱処理をして、微粒子の表面部分を酸化して、被覆層としての酸化銀140を形成する。ナノメートルサイズの複数の微粒子130および被覆層140を、少ない工程で形成する。

(もっと読む)

ラテラルサイリスタ及びトラッピング層を有するシリコン‐オン‐インシュレータ読み取り‐書き込み不揮発性メモリ

改善した、サイリスタに基づくメモリセルを提供する。一例では、シリコン‐オン‐インシュレータ(SOI)技術を用いて、セル(10)をフローティング基板内に形成する。セルには、第2ワードラインによりゲート駆動されるとともに完全にフローティング基板内に形成されたラテラルサイリスタ(20)を有するのが好ましい。このサイリスタのカソードは、アクセストランジスタ(18)のソースをも有し、このアクセストランジスタのドレインは装置のビットラインに接続されており、このアクセストランジスタは第1ワードライン(14)によりゲート駆動される。フローティング基板内にはトラッピング層が形成され、セルに書き込みを行う場合、パルスを加えて、論理状態“1”に対し正孔をトラッピング層にトラッピングさせ、論理状態“0”に対し電子をトラッピング層にトラッピングさせる。トラッピング層に電荷をトラッピングさせることにより、記憶されたデータ状態に追加の余裕度を加え、これらデータ状態の劣化を回避し、セルを不揮発性とする。  (もっと読む)

(もっと読む)

1 - 10 / 10

[ Back to top ]