Fターム[5F102FA10]の内容

接合型電界効果トランジスタ (42,929) | 目的、効果 (2,241) | 実装構造の改良 (50)

Fターム[5F102FA10]に分類される特許

1 - 20 / 50

高周波半導体装置

【課題】半導体チップを実装できる幅を増大し、実装基板上を有効に使用可能な高周波用半導体装置を提供する。

【解決手段】導体ベースプレートと、導体ベースプレート上に配置されたマルチセル構成の半導体チップと、導体ベースプレート上に配置され、半導体チップを内在する矩形のキャビティを形成する金属壁と、金属壁の入出力部に設けられた貫通孔とを備え、半導体チップを、金属壁に囲まれた矩形のキャビティ内において、半導体チップの長手方向が、貫通孔の設けられていない金属壁の延伸方向から0度より大で、90度より小の所定の角度に配置した半導体装置。

(もっと読む)

高周波半導体装置

【課題】ボンディングワイヤの長さを長くすることなくインダクタンスの値を大きくできる高周波用半導体装置を提供する。

【解決手段】高周波半導体装置1は、マルチセル構成の半導体チップ24と、整合回路と、半導体チップ24と整合回路間に並列に接続された複数本のボンディングワイヤ12、14とを備え、複数本のボンディングワイヤ12、14は、半導体チップ24に対して平面上で90°以下の所定の角度を有する。

(もっと読む)

半導体装置の製造方法

【課題】チャージアップに起因するリーク電流及び閾値電圧の変動を抑制することが可能な半導体装置の製造方法を提供すること。

【解決手段】本発明は、半導体層内に、活性領域30を含むFET34、活性領域30からなるスクライブライン36、FET34とスクライブライン36との間に位置する不活性領域32、及び不活性領域32を横断してFET34とスクライブライン36とを電気的に接続する接続領域38を設ける工程と、半導体層上に絶縁膜20を形成する工程と、ドライエッチング法により絶縁膜20に選択的に開口部21を形成する工程と、を有する半導体装置である。

(もっと読む)

集積型半導体装置

【課題】 従来に比べて小型で、素子機能部間で、高い周波数の信号を高精度に伝送することができる集積型半導体装置を提供する。

【解決手段】

サファイア単結晶基板10の一方主面10A上に配置された第1素子機能部26と、一方主面上10Aに配置された第1アンテナ部23と、他方主面10Bに配置された第2素子機能部36と、他方主面10B上に配置された第2アンテナ部33とを備え、第1素子機能部26が第1アンテナ部23に送信用電気信号を送り、第1アンテナ部23が送信用電気信号に応じた電波を発信し、第2アンテナ部33がサファイア単結晶基板10を透過した電波を受信することで、高い周波数の信号を基板の上下面で高精度に処理することができる。

(もっと読む)

半導体装置

【課題】窒化物半導体を用いたFETを樹脂封止パッケージに搭載した半導体装置の耐湿性を向上させること。

【解決手段】本発明は、窒化物半導体を用いたFETが形成されたチップ30と、前記チップがAgペースト22を用い搭載されたベース12と、前記チップ30を封止するガラス転移温度が190℃以上の樹脂20と、を具備する半導体装置である。

(もっと読む)

電界効果トランジスタ

【課題】ゲート電極とソース電極との間に印加される電圧がソース電極パッドの電気抵抗による電圧降下で低下することを防止でき、安定した動作を実現できる電界効果トランジスタを提供する。

【解決手段】このGaN HFETによれば、ボンディング部16Bの第2のパッド部16B‐2は、電極接続部16Aが含有する複数の接続部分19のうちの第2の方向(ソース電極12とドレイン電極11が対向している方向)の一端に配置された接続部分19の上記第2の方向の外端を電極延在方向へ延長した仮想延長線L1に関して第1のパッド部16B‐1とは反対側に位置している。第2のパッド部16B‐2に接続された第2のソース配線24のボンディング箇所の第2の方向の位置を電極接続部16Aのソース電極12との接続部分19の第2の方向の位置と重ならないようにして、ソース電極12からの電流が第2のソース配線24に流れにくくできる。

(もっと読む)

窒化物半導体装置

【課題】リードフレーム上に搭載された窒化物FETを備えスイッチング特性に優れた窒化物半導体装置を提供する。

【解決手段】窒化物FETと、複数のリードを含むリードフレームと、を備え、前記窒化物FETは少なくとも第1の主電極と第2の主電極と制御電極とを有し、前記リードフレームは、前記第1の主電極に接続される第1のリードと、前記第2の主電極に接続される第2のリード及び第3のリードと、前記制御電極に接続される第4のリードと、を有し、前記窒化物FETは、前記第3のリードと前記第4のリードとの間に印加される電圧に応じて前記第1のリードと前記第2のリードとの間に電流を流すことを特徴とする窒化物半導体装置。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体パッケージ内における半導体素子の位置ずれを抑制することができる半導体装置を提供すること。

【解決手段】実施形態に係る半導体装置10は、凸部23が形成されたパッケージ基板11、導電性の接着剤25、およびパッケージ基板11上に実装された半導体素子14、を具備する。パッケージ基板11は、少なくとも2箇所に凸部23が形成された基板である。導電性の接着剤25は、凸部23を含むパッケージ基板11上に形成される。パッケージ基板11上に実装される半導体素子14は、各凸部23に係合する複数のバイアホール24を有している。さらに、半導体素子14は、少なくとも2箇所のバイアホール24が、各凸部23に接着剤25を介して係合するようにパッケージ基板11上に実装される。

(もっと読む)

半導体装置

【課題】差分周波数Δfが数百MHzにおいても高周波半導体チップのドレイン端面の電圧が平滑化された半導体装置を提供する。

【解決手段】高周波半導体チップと、高周波半導体チップの入力側に配置された入力側分布回路と、高周波半導体チップの出力側に配置された出力側分布回路と、入力側分布回路に接続された高周波入力端子と、出力側分布回路に接続された高周波出力端子と、高周波半導体チップのドレイン端子電極近傍に配置された平滑化キャパシタとを備え、高周波半導体チップと、入力側分布回路と、出力側分布回路と、平滑化キャパシタとが1つのパッケージに収納されたことを特徴とする半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】放熱性と耐久性に優れた半導体装置およびその製造方法を提供する。

【解決手段】導電ベースプレートと、導電ベースプレート上に接合される半導体チップと、半導体チップと導電ベースプレートとの接合面の中央部に配置された第1接着剤と、半導体チップと導電ベースプレートとの接合面の周辺部に配置された第2接着剤とを備え、第1接着剤は第2接着剤よりも相対的に熱伝導率が高く、第2接着剤は第1接着剤より相対的に接合力が高い半導体装置。

(もっと読む)

半導体装置

【課題】横方向からのノイズに対するトランジスタ動作の影響を抑制する。

【解決手段】GaNを用いたHEMTが形成されたチップ30と、前記チップを搭載する導電性のステージ11と、前記ステージと前記HEMTのソースとに電気的に接続されたソースリード12と、前記HEMTのゲートに電気的に接続されたゲートリード14と、前記HEMTのドレインに電気的に接続されたドレインリード13と、を具備し、前記ソースリード、前記ドレインリードおよび前記ゲートリードの順に配列されている半導体装置。

(もっと読む)

III−V族トランジスタとIV族縦型トランジスタを含む積層複合デバイス

【課題】従来の共通基板上へのデバイスの並置構成は、電流通路の寄生のインダクタンス、抵抗、及びパッケージの放熱要件を増大し、製造コストも増大するため、III−窒化物又は他のIII−V族トランジスタをIV族ダイオードと一体化するコンパクトでコストエフェクティブなパッケージングを提供する。

【解決手段】積層複合デバイスはIV族縦型トランジスタ120と該IV族縦型トランジスタの上に積層されたIII−V族トランジスタ110とを備える。IV族縦型トランジスタのドレインがIII−V族トランジスタのソースと接触され、IV族縦型トランジスタのソースが前記積層複合デバイスの底面の複合ソースを与えるためにIII−V族トランジスタのゲートに結合され、III−V族トランジスタのドレインが積層複合デバイスの上面の複合ドレインを与える。IV族縦型トランジスタのゲートが前記積層複合デバイスの上面の複合ゲートを与える。

(もっと読む)

III−V族トランジスタとIV族横型トランジスタを含む積層複合デバイス

【課題】内部に横型トランジスタが形成されたシリコン又はIV族アクティブダイの上面に、III−V族アクティブダイが積層された積層複合デバイスを製作する。

【解決手段】積層複合デバイスはIV族横型トランジスタ120と、IV族横型トランジスタの上に積層されたIII−V族トランジスタ110とを備える。IV族横型トランジスタのドレインがIII−V族トランジスタのソースと接触され、IV族横型トランジスタのソースがIII−V族トランジスタのゲート116に結合されて前記複合デバイスパッケージの上面の複合ソース102を与え、III−V族トランジスタのドレインが複合デバイスパッケージの上面の複合ドレイン104を与える。IV族横型トランジスタのゲート126が積層複合デバイスの上面の複合ゲート106を与え、IV族横型トランジスタの基板が積層複合デバイスの底面にある。

(もっと読む)

半導体装置及び電力増幅器

【課題】トランジスタの占有面積をほとんど増やすことなく、かつ、HBTとHFETとを接続する配線による悪影響を受けないBi−HFET(半導体装置)を提供する。

【解決手段】基板101上に形成されたHFET160と、HFET160上に形成されたHBT170とを備え、HFET160は、チャネル層102と、コンタクト層104とを有し、HBT170は、HFET160のコンタクト層104と接続、又は、一体化されたサブコレクタ層107と、コレクタ層108と、ベース層109と、エミッタ層110と、エミッタキャップ層111と、エミッタコンタクト層112とを有し、コレクタ層108、ベース層109及びエミッタ層110は、メサ形状の構造体であるベースメサ領域830を構成し、ゲート電極202は、第一のコレクタ電極203とベースメサ領域830との平面的な間に設けられたリセス領域820内に形成されている。

(もっと読む)

パッケージ

【課題】電流容量が高く、かつ生じる応力が低減されてクラックの発生が抑制され、信頼性の高いパッケージを提供する。

【解決手段】パッケージ外壁16と、パッケージ外壁16を貫通する貫通孔と、貫通孔にはめ込まれた凸状フィードスルー25と、凸状フィードスルー25に固定され端子電極21bとを備え、端子電極21bは、相対的に線熱膨張率は低いが抵抗率が高い第1の金属層90と、相対的に線熱膨張率は高いが抵抗率が低い第2の金属層80a,80bとを備える。

(もっと読む)

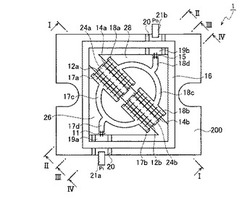

MMIC用パッケージ

【課題】チップサイズの大きい高周波部品(MMIC)とパッケージ端子間を接続するインダクタンス成分を抑制し、高周波特性を改善したMMIC用パッケージを提供する。

【解決手段】導体ベースプレート200と、導体ベースプレート200上に配置され、入力端子24aおよび出力端子24bを有するMMIC基板24と、導体ベースプレート200上に配置され、MMIC基板24を囲むセラミック枠体180と、セラミック枠体180上に配置されたパッケージ入力端子21aおよびパッケージ出力端子21bと、MMIC基板24とセラミック枠体180との間の導体ベースプレート200上に配置された結合用基板25と、結合用基板25上に配置された結合ライン25aとを備え、パッケージ入力端子21aと結合ライン25a間、および結合ライン25aと入力端子24a間とが接続されている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート電極の電界集中を緩和して耐圧の更なる向上を実現することに加え、デバイス動作速度を向上させ、アバランシェ耐量が大きく、サージに対して強く、例えばインバータ回路等に適用する場合に外部のダイオードを接続することを要せず、ホールが発生しても安定動作を得ることができる信頼性の高い高耐圧の化合物半導体装置を実現する。

【解決手段】化合物半導体積層構造2に形成された電極用リセス2Cを、ゲート絶縁膜6を介して電極材料で埋め込むようにゲート電極7を形成すると共に、化合物半導体積層構造2に形成されたフィールドプレート用リセス2Dをp型半導体で埋め込み、化合物半導体積層構造2とp型半導体層8aで接触するフィールドプレート8を形成する。

(もっと読む)

パッケージ

【課題】ベース面の反りの少ないパッケージを提供する。

【解決手段】導体ベースプレート200と、導体ベースプレート上に配置された半導体装置と、半導体装置を内在し、導体ベースプレート上に配置され、導体ベースプレートとは異なる材料からなる金属壁16とを備え、導体ベースプレートは、対抗する1対の端面100a・100bが緩やかな弧を有し、金属壁も緩やかな弧を有しているので、接合時や基板実装時、キャップ半田付け時の反りの発生を抑制できる。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】良好なノーマリ・オフ動作を可能とすることに加え、アバランシェ耐量が大きく、外部のダイオードを接続することを要せず、確実に安定動作を得ることができる信頼性の高い高耐圧のHEMTを得る。

【解決手段】化合物半導体積層構造2に形成された電極用リセス2Cを、ゲート絶縁膜6を介して電極材料で埋め込むようにゲート電極7を形成すると共に、化合物半導体積層構造2に形成された電極用リセス2Dを、少なくとも電極用リセス2Dの底面で化合物半導体積層構造2と直接的に接するように電極材料で埋め込み、化合物半導体積層構造2とショットキー接触するフィールドプレート電極8を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】歩留りが高く信頼性の高いパッケージングされた半導体装置を提供する。

【解決手段】電極が形成された半導体チップと、前記電極に対応するリードと、前記電極と前記リードとを接続する金属配線と、前記金属配線と前記電極との接続部分及び前記金属配線と前記リードとの接続部分を覆う第1の樹脂部と、前記金属配線、前記第1の樹脂部及び前記半導体チップを覆う第2の樹脂部と、を有することを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

1 - 20 / 50

[ Back to top ]